Месяц назад в российских университетах прошли семинары по MIPSfpga (1, 2, 3, 4), а джентлемен из НИИСИ по имени Антон Павлов написал заметку про его собственные улучшения MIPSfpga «MIPSfpga: вне канона». Так как профессора встретили новый продукт для обучения студентов электронике в целом положительно, то возникла идея помочь начинаю платами, причем сразу у нескольких людей и организаций.

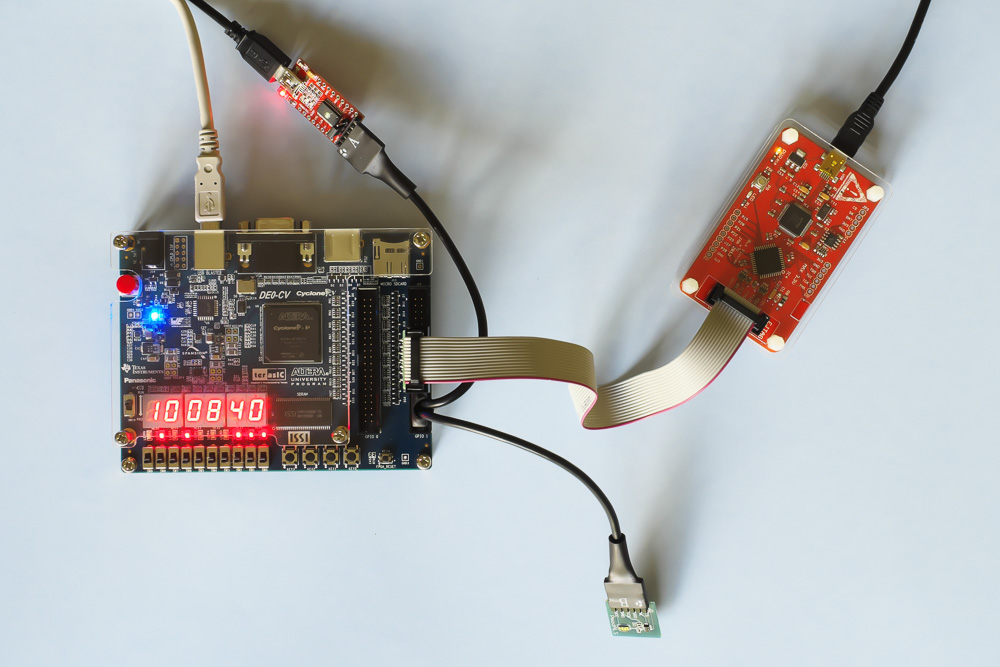

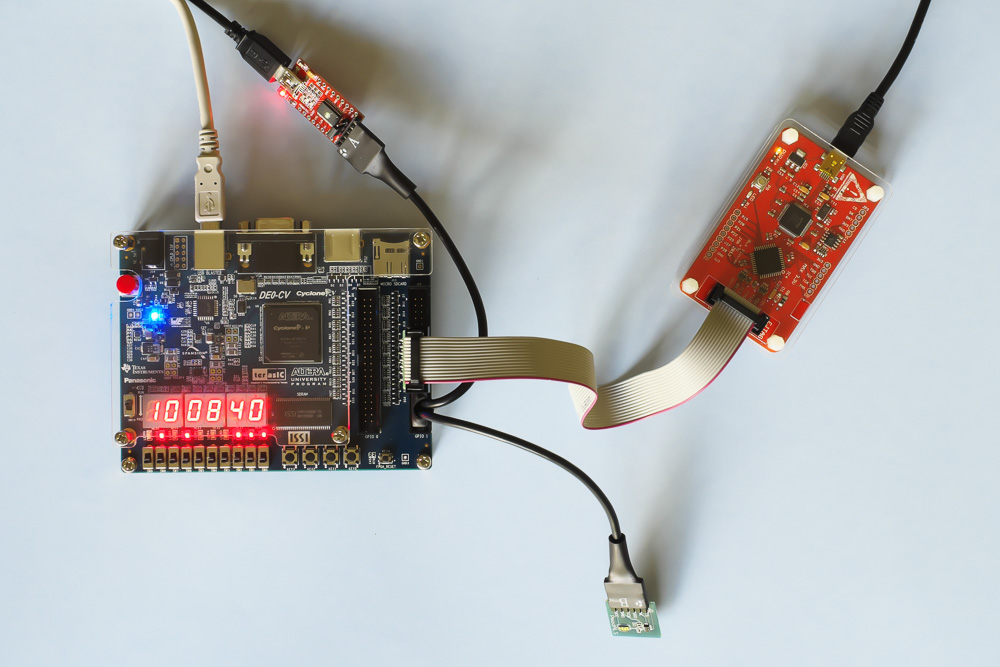

В частности, в честь Нового Года я в кооперации с Виталием Кравченко из univeda.ru планируем небольшую раздачу слонов, то бишь бесплатных плат Terasic DE0-CV с FPGA Altera Cyclone V. Так что вы сможете повторить подвиг Антона Павлова. Так как данная конкретная раздача делается _не_ на деньги Imagination Technologies, не на деньги Altera и не на деньги НПЦ «Элвис», а на деньги частных благотворителей, включая меня лично, то слоны будут раздаваться с довольно конкретными условиями, описанными ниже.

Цели мероприятия:

1. Повысить уровень вовлеченности российских вузов в мировые исследования в области микроархитектуры процессоров, проектирования СнК и гетерогенных многоядерных систем

2. Повысить количество русских текстов на MIPS Insider дабы посетители из международной электронной промышленности и academia начинали понимать, что русские идут

3. Изготовить, от лица коммьюнити, кучу учебных материалов вокруг MIPSfpga, которыми могли бы пользоваться как преподаватели российских вузов, так и преподаватели университетов в других странах — США, Японии, Китае и т.д.

Условия:

1. Желательно чтобы получатель платы был преподавателем, аспирантом или студентом российского вуза.

2. Желательно, чтобы этим вузом не был МГУ, МФТИ, МИФИ, МИЭТ и ИТМО, которые могут получить эти платы из других источников.

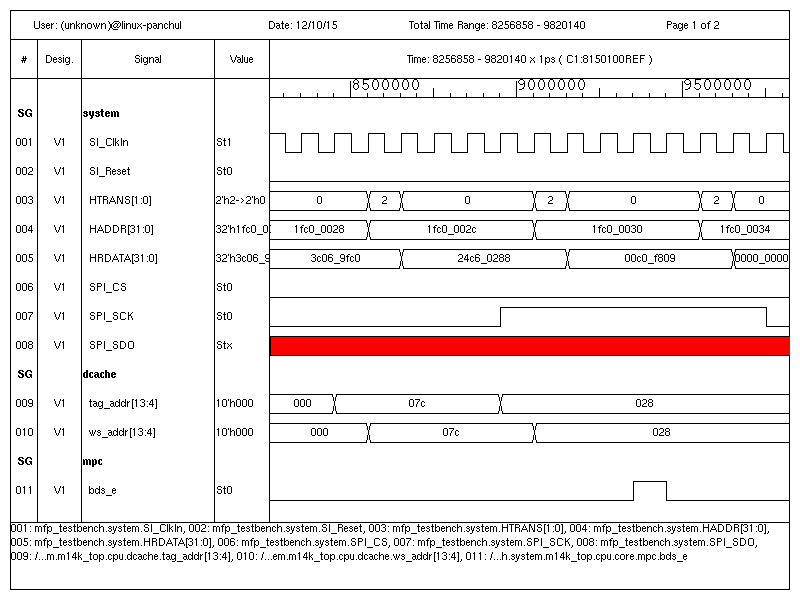

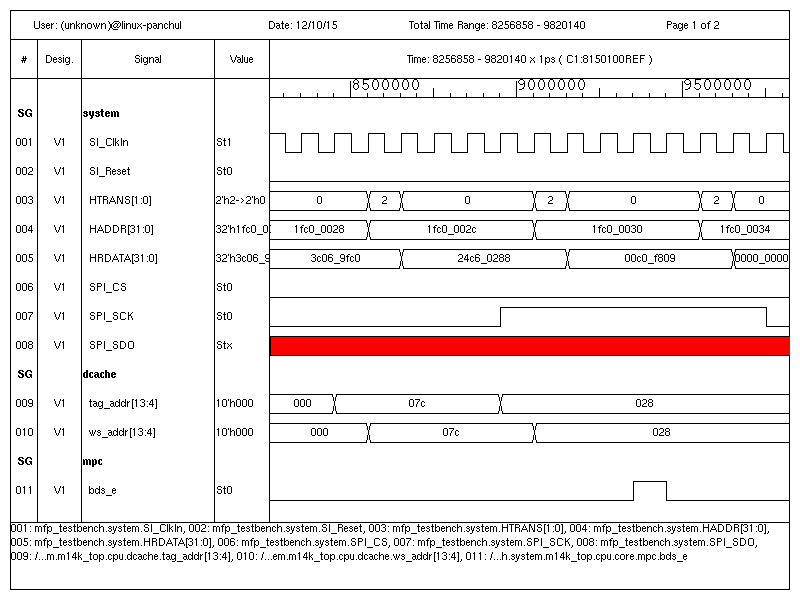

3. Очень желательно, чтобы перед получением платы креативный товарищ прислал бы мне не только описание проекта, но и код на Verilog или VHDL, C и/или ассемблере, с которым он симулировал прототип будущей синтезированной системы в среде ModelSim или Icarus. Временные диаграммы тоже приветствуются.

4. Код проекта по завершению выкладывается на http://github.com/MIPSfpga — см. в качестве примера http://github.com/MIPSfpga/mipsfpga-plus

5. Там же описывается в секции Wiki:

5.1. Что находится в каждом файле

5.2. Иерархия модулей хардверной части

5.3. Как симулировать — инструкция со скриншотами

5.4. Временные диаграммы симуляции

5.5. Как синтезировать — инструкция со скриншотами

5.6. Результаты синтеза — размер и максимальная частота

5.7. Описание софтверной части

5.8. Фотографии работающей платы FPGA

6. Это же выкладывается на http://geektimes.ru в форме статьи

7. Это же выкладывается на http://silicon-russia.com

8. Это же выкладывается на http://community.imgtec.com/forums/cat/mips-insider/mipsfpga

9. Язык (6), (7), (8) может быть русский или английский

10. Если вы ничего не делаете с платой месяц, она у вас изымается и передается кому-нибудь еще

11. Если мы (я и UnivEDA) будем делать какие-либо мероприятия в России типа конкурсов или трейнингов, мы у вас плату тоже на некоторое время заберем назад

Примеры проектов с платами:

1. Интерфейс между MIPSfpga и сенсорами с интефейсами SPI, I2C, UART и другими. Сенсоры влажности, температуры, звука, компасы, дальномерка и т.д.

2. Интерфейс между MIPSfpga и внешней по отношению к FPGA памяти — SDRAM, DDR и т.д. (в текущих примерах память системы строится из block memory внутри FPGA)

3. Интерфейс между MIPSfpga и более крупными устройствами — VGA дисплей, мышь, клавиатура, джойстик.

4. Визуализация работы кэша с помощью запуска процессора с частотой 1 такт в секунду и вывода сигналов, связанных с транзакцией (запрос, промах и т.д.).

5. Визуализация работы конвейера и арифметических устройств с помощью запуска процессора с частотой 1 такт в секунду и вывода сигналов контроля конвейера и т.д.

6. Добавление команд в процессор с помощью интерфейса CorExtend / User Defined Instructions (UDI). Пример — специальные команды для шифрования.

7. Лабораторные работы с демонстрацией работы прерываний в разных режимах и обработчика прерываний.

8. Мосты между шиной AHB-Lite и другими шинами — AXI, APB, OCP, Wishbone, PLB и т.д.

9. Многопрооцессорные системы без когерентности кэшей первого уровня и (для самых продвинутых) с когерентными кэшами и реализацией протоколов типа MESI.

10. Портирование на MIPSfpga разного рода программ и операционных систем — от простых RTOS до различных вариантов Linux (MIPSfpga поддерживает TLB MMU).

Прошу присылать предложения на yuri.panchul@imgtec.com с копией yuri@panchul.com

В частности, в честь Нового Года я в кооперации с Виталием Кравченко из univeda.ru планируем небольшую раздачу слонов, то бишь бесплатных плат Terasic DE0-CV с FPGA Altera Cyclone V. Так что вы сможете повторить подвиг Антона Павлова. Так как данная конкретная раздача делается _не_ на деньги Imagination Technologies, не на деньги Altera и не на деньги НПЦ «Элвис», а на деньги частных благотворителей, включая меня лично, то слоны будут раздаваться с довольно конкретными условиями, описанными ниже.

Цели мероприятия:

1. Повысить уровень вовлеченности российских вузов в мировые исследования в области микроархитектуры процессоров, проектирования СнК и гетерогенных многоядерных систем

2. Повысить количество русских текстов на MIPS Insider дабы посетители из международной электронной промышленности и academia начинали понимать, что русские идут

3. Изготовить, от лица коммьюнити, кучу учебных материалов вокруг MIPSfpga, которыми могли бы пользоваться как преподаватели российских вузов, так и преподаватели университетов в других странах — США, Японии, Китае и т.д.

Условия:

1. Желательно чтобы получатель платы был преподавателем, аспирантом или студентом российского вуза.

2. Желательно, чтобы этим вузом не был МГУ, МФТИ, МИФИ, МИЭТ и ИТМО, которые могут получить эти платы из других источников.

3. Очень желательно, чтобы перед получением платы креативный товарищ прислал бы мне не только описание проекта, но и код на Verilog или VHDL, C и/или ассемблере, с которым он симулировал прототип будущей синтезированной системы в среде ModelSim или Icarus. Временные диаграммы тоже приветствуются.

4. Код проекта по завершению выкладывается на http://github.com/MIPSfpga — см. в качестве примера http://github.com/MIPSfpga/mipsfpga-plus

5. Там же описывается в секции Wiki:

5.1. Что находится в каждом файле

5.2. Иерархия модулей хардверной части

5.3. Как симулировать — инструкция со скриншотами

5.4. Временные диаграммы симуляции

5.5. Как синтезировать — инструкция со скриншотами

5.6. Результаты синтеза — размер и максимальная частота

5.7. Описание софтверной части

5.8. Фотографии работающей платы FPGA

6. Это же выкладывается на http://geektimes.ru в форме статьи

7. Это же выкладывается на http://silicon-russia.com

8. Это же выкладывается на http://community.imgtec.com/forums/cat/mips-insider/mipsfpga

9. Язык (6), (7), (8) может быть русский или английский

10. Если вы ничего не делаете с платой месяц, она у вас изымается и передается кому-нибудь еще

11. Если мы (я и UnivEDA) будем делать какие-либо мероприятия в России типа конкурсов или трейнингов, мы у вас плату тоже на некоторое время заберем назад

Примеры проектов с платами:

1. Интерфейс между MIPSfpga и сенсорами с интефейсами SPI, I2C, UART и другими. Сенсоры влажности, температуры, звука, компасы, дальномерка и т.д.

2. Интерфейс между MIPSfpga и внешней по отношению к FPGA памяти — SDRAM, DDR и т.д. (в текущих примерах память системы строится из block memory внутри FPGA)

3. Интерфейс между MIPSfpga и более крупными устройствами — VGA дисплей, мышь, клавиатура, джойстик.

4. Визуализация работы кэша с помощью запуска процессора с частотой 1 такт в секунду и вывода сигналов, связанных с транзакцией (запрос, промах и т.д.).

5. Визуализация работы конвейера и арифметических устройств с помощью запуска процессора с частотой 1 такт в секунду и вывода сигналов контроля конвейера и т.д.

6. Добавление команд в процессор с помощью интерфейса CorExtend / User Defined Instructions (UDI). Пример — специальные команды для шифрования.

7. Лабораторные работы с демонстрацией работы прерываний в разных режимах и обработчика прерываний.

8. Мосты между шиной AHB-Lite и другими шинами — AXI, APB, OCP, Wishbone, PLB и т.д.

9. Многопрооцессорные системы без когерентности кэшей первого уровня и (для самых продвинутых) с когерентными кэшами и реализацией протоколов типа MESI.

10. Портирование на MIPSfpga разного рода программ и операционных систем — от простых RTOS до различных вариантов Linux (MIPSfpga поддерживает TLB MMU).

Прошу присылать предложения на yuri.panchul@imgtec.com с копией yuri@panchul.com

Только зарегистрированные пользователи могут участвовать в опросе. Войдите, пожалуйста.

Комментарии (3)

den1s1

11.12.2015 18:48месяца мало

YuriPanchul

11.12.2015 19:44Я не ожидаю, чтобы за месяц человек сделал полностью некий проект. Только что он начнет что-то делать. Чтобы не было так, что человек берет плату и на неопределенное время откладывает.

Khort

Спасибо! Разошлю знакомым преподам в других городах.