Всем привет! Надеюсь, все хорошо провели праздники и готовы с новыми силами покорять высоты FPGA разработки.

Сегодня я хочу написать небольшой гайд по запуску тестбенчей на Verilog/SystemVerilog в ModelSim без использования GUI.

План будет такой:

- Добавление пути к ModelSim в PATH.

- Написание скрипта с объяснением команд.

- Запуск ModelSim с исполнением написанного скрипта.

Поехали! Чтобы начать, на руках нужно иметь следующее:

- установленный ModelSim;

- готовый проект на Verilog/SystemVerilog;

- готовый тестбенч на Verilog/SystemVerilog;

В качестве примера будем рассматривать проект HappyNY

Итак, приступим.

1. Добавление пути к исполняемому файлу modelsim в PATH

Проверить, нужно ли это делать, можно легко: наберите в командной строке modelsim, если после этого запустится ModelSim, значит, текущий пункт можно пропустить. В противном случае, для Windows это делается следующим образом: открывается командная строка и пишется команда

set PATH=%PATH%; C:\Progs\ModelSim10_5\win64в которой указан путь к исполняемому файлу modelsim (после; вам нужно указать свой путь к исполняемому файлу). После выполнения команды проведите проверку, указанную в начале этого пункта, если что-то не так, то повторите пункт.

2. Написание скрипта для запуска

ModelSim имеет командую строку, в которой вы может набирать разнообразные команды для запуска и управления симуляцией. Довольно подробный гайд по командам можно посмотреть вот здесь или здесь. Для скриптов ModelSim принят формат файла *.do. Создаём файл с указанным расширением в любом текстовом редакторе (блокнот, sublime text, vim, notepad++, НО НЕ WORD!!!), и пишем туда следующие команды:

transcript on

vlib workРазберём этот кусочек скрипта.

Команда transcript с флагом on — это тоже самое что echo, т.е. после указания этой команды все последующие команды, указанные в скрипте, печатаются при выполнении в командной строке ModelSim, т.е. становится видно, какая команда когда исполнялась и после какой из них возникла ошибка (если возникла).

Команда vlib создаёт библиотеку проекта с именем work.

Продолжаем:

vlog -sv +incdir+./ ./happyNY.sv

vlog -sv +incdir+./ ./tb.svКоманда vlog с флагами — это вызов компилятора Verilog.

Флаг -sv, как вы уже догадались, указывает компилятору использовать стандарт SystemVerilog. Компилируются файлы все независимо, в отличие например от Quartus, поэтому если вы делаете, например, import каких-то частей package, то нужно делать их в каждом файле, где они используются, либо прямо внутри файла, содержащего package (Quartus, если не предусмотреть стражей включения, выкинет в этом случае ошибку).

Флаг +incdir+../ показывает, где компилятор должен искать включаемые файлы (т.е. файлы, указанные в коде с директивой `include).

Далее идёт имя компилируемого файла.

Продолжаем:

vsim -t 1ns -voptargs="+acc" tbКоманда vsim — это запуск симуляции.

Флаг -t задаёт точность временной сетки.

Флаг -voptargs получает аргументы для последующего автоматического вызова оптимизатора vopt, т.е. произойдёт вызов vopt +acc. Этот флаг включает оптимизации для разных объектов в проекте и включает видимость этих объектов в симуляторе. Подробнее прочитать про него можно здесь на стр. 154.

В конце идёт имя top-level тестбенча, в данном примере оно совпадает с именем файла.

И, наконец, последняя часть скрипта:

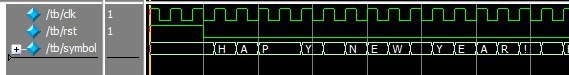

add wave /tb/clk

add wave /tb/rst

add wave -radix ASCII /tb/symbol

configure wave -timelineunits us

run -all

wave zoom fullСначала мы добавляем нужные нам сигналы на форму Wave Window командой add wave. Обратите внимание, что у одного из сигналов изменён формат отображения на символьный с помощью флага -radix ASCII.

Далее мы устанавливаем единицы шкалы временной сетки. Запускаем симуляцию по сценарию, написанному в тестбенче. Растягиваем (или сжимаем) картинку в Wave Window так, чтобы она поместилась точно в размер окна.

3. Запуск ModelSim с исполнением скрипта

Первым делом нужно открыть командную строку или терминал и перейти в директорию, где лежит ваш скрипт и файлы проекта. Затем нужно запустить исполняемый файл modelsim с ключом -do <script_name>, в нашем случае:

modelsim -do happyNY.doБольше ничего делать не нужно. Если по какой-то причине вы не смогли добавить путь к ModelSim в переменные среды, вместо modelsim можно указать полный путь к исполняемому файлу. Если и это не сработало, то, запустив ModelSim вручную, можно в командной строке ModelSim перейти в директорию проекта и запустить наш скрипт командой:

do happyNY.doПосле всех описанных процедур вы должны увидеть вот такую картинку:

Спасибо за внимание, удачи!

Только зарегистрированные пользователи могут участвовать в опросе. Войдите, пожалуйста.

Комментарии (14)

SparF

13.01.2017 18:52+1Похожий подход к отладке видел вот здесь :

— .bat создает и удаляет каталог для всего хлама, связанного с симуляцией;

— .tcl — оперирует компиляцией, сигналами и отладкой

Я у себя добавляю только формирование строки vlog по частям (чтобы не в одну линию).

Достаточно удобно, когда руками (в интерфейсе) делать влом, а с make-файлами связываться еще не хочется.

GREGOR_812

14.01.2017 16:22Мне посоветовали добавить опрос, прикрепил его, проголосуйте, пожалуйста) Если будут голоса за линукс, надо будет дополнить статью инструкциями, как то же самое делать в линуксе

Andruwkoo

15.01.2017 04:22+1на самом деле скриптинг запуска тестбенчей намного более мощная штука. можно при запуске устанавливать параметры в зависимости от который будет исполняться конкретный тест (набор тестов) из всего тестового окружения путем изменения в верхнем уровне тестбенча значений переменных, на основании выбранного теста можно выбирать различные времянки предварительно подготовленные (кстати, намного удобнее держать скрипт создания времянки в отдельном файле, особенно если много сигналов выведено), можно отключать некоторые элементы DUT, особенно если тестируемый модуль имеет множество блоков, что может ускорить симуляцию в некоторых случаях значительно)

GREGOR_812

15.01.2017 17:48Было бы здорово увидеть статью об этом)

Andruwkoo

16.01.2017 23:39не берусь обещаться) я не очень большой в этом специалист, и время не радует своим наличием, но постараюсь)

1an1

17.01.2017 12:20Подробней про команды ModelSim Command Reference Manual и User’s Manual.

GREGOR_812

17.01.2017 12:59Первую ссылку заменил, спасибо) В тексте был документ для более старой версии ModelSim. Вторая в тексте точно такая же

icyrock

18.01.2017 13:07+11. Добавим, что можно не только .do, но и .tcl

2. Вы напрасно затеваете папку rtl_work. Многие разработчики пользуются дефолтной папкой/библиотекой work и они вас не сразу поймут.

Строчки:

vlib rtl_work

vmap work rtl_work

можно заменить на:

vlib work

3. Кроме того удалять библиотеку не обязательно, можно создавать новую поверх старой. Он конечно напишет предупреждение что библиотека уже есть, но ничего плохого не случится.

4. Зачем брать имена компилируемых файлов в фигурные скобки? Если это coding style, то вы не сможете подставить переменную в путь файла. Например {$dir/your_file.sv} не сработает.

5. -L нужен при линковке сторонних (кроме work) библиотек. work линкуется по умолчанию.

6. В vlog -work work совершенно излишне. Это делается по умолчанию.

GREGOR_812

18.01.2017 16:20Спасибо, поправлю сегодня) изначально я ориентировался на скрипт, который генерит квартус при использовании NativeLink, поэтому о некоторых вещах узнаю сейчас впервые (пп. 4-6)

Tausinov

Добрый день! Недавно пытался сделать что-то похожее для VHDL и уперся в то, что в отличии от Verilog'a важен порядок компиляции файлов. Серьезные IDE справляются с этим играючи, но «выковырять» от туда, как они это делают — не вышло. В связи с этим вопрос — нет ли каких-то наработок подобного для VHDL?

Пы.Сы.Если честно, то получилось добраться до порядка файлов в компиляции через non-project mode Vivado, но это слишком уж костыльный вариант. Если при этом в проекте есть криптованные ядра, то наличие порядка файлов уже становится мало, а генерить скрипты для симуляции Vivado в этом режиме не может. Создавать каждый раз проект — то же не слишком удобно.

GREGOR_812

Приветствую!

С VHDL никогда не работал, так что ничего конкретного подсказать, к сожалению, не смогу. Есть мысль попробовать запустить симуляцию вашего проекта, используя NativeLink квартуса и посмотреть, какой скрипт он сгенерит, затем попробовать проанализировать его) Что касается наличия чип-зависимых IP, тут уже нужны библиотеки производителя, их надо использовать при указании библиотек в ModelSim.

Удачи!

ont0shko

А вы попробуйте для начала в ModelSim создать проект, добавить в него все необходимые файлы, а потом запустите Auto-Generating Compile Order. На основе расставленной очередности делайте базовый сценарий. Проектом можно больше не пользоваться, а организовывать все на tcl, sh или что вам нравиться. Входе работы делаем редакцию ручками это уже не так сложно.

Andruwkoo

некоторые IDE умеют автоматически компилировать исходники (синтезируемое описание) для симуляции. HDL Designer точно умеет сам все скомпилить для модельсима, остается только файлы тестбенча скомпилить, которых обычно намного меньше и не стоит больших трудов их в скрипт добавить. вроде вивада тоже умеет, но могу ошибаться, давно с ней не работал