Британский стартап UltraSoC представил on-chip-технологию для отслеживания характеристик микросхем без ущерба для производительности. Рассказываем, как устроено решение.

/ фото 83DegreesMedia CC BY

Гетерогенные устройства строятся из нескольких блоков. Ими могут выступать процессоры, сопроцессоры или интегральные схемы ASIC. Специализация вычислительных модулей повышает производительность всей системы, но «многокомпонентный состав» приводит к сложностям с оптимизацией — каждому аппаратному блоку требуется настройка.

Проблема усугубляется, если чипы используются крупным дата-центром. Мониторинг обширной инфраструктуры — задача не из легких. Специализированные программные решения зачастую наносят ущерб эффективности работы вычислительных систем. К примеру, утилита для измерения пропускной способности канала iPerf снижает производительность сети на 10–15%.

Для решения этой проблемы UltraSoC внедрили инструменты для мониторинга прямо на чип. Компания разработала ряд логических полупроводниковых модулей, каждый из которых отвечает за одну из задач — мониторинг, отладку, обеспечение безопасности. Производители чипов могут использовать эти модули и вытраливать их на одной схеме с процессорами, GPU, сетевыми интерфейсами. Это позволяет собирать данные со всех компонентов микросхемы «на месте» без инвазивных программных решений. Эта технология уже адаптирована для работы со стандартными архитектурами: от ARM и RISC-V до MIPS и Xtensa.

В UltraSoC предлагают порядка тридцати модулей, которые можно компоновать в зависимости от особенностей конкретной системы на кристалле (SoC). Модули делятся на три класса:

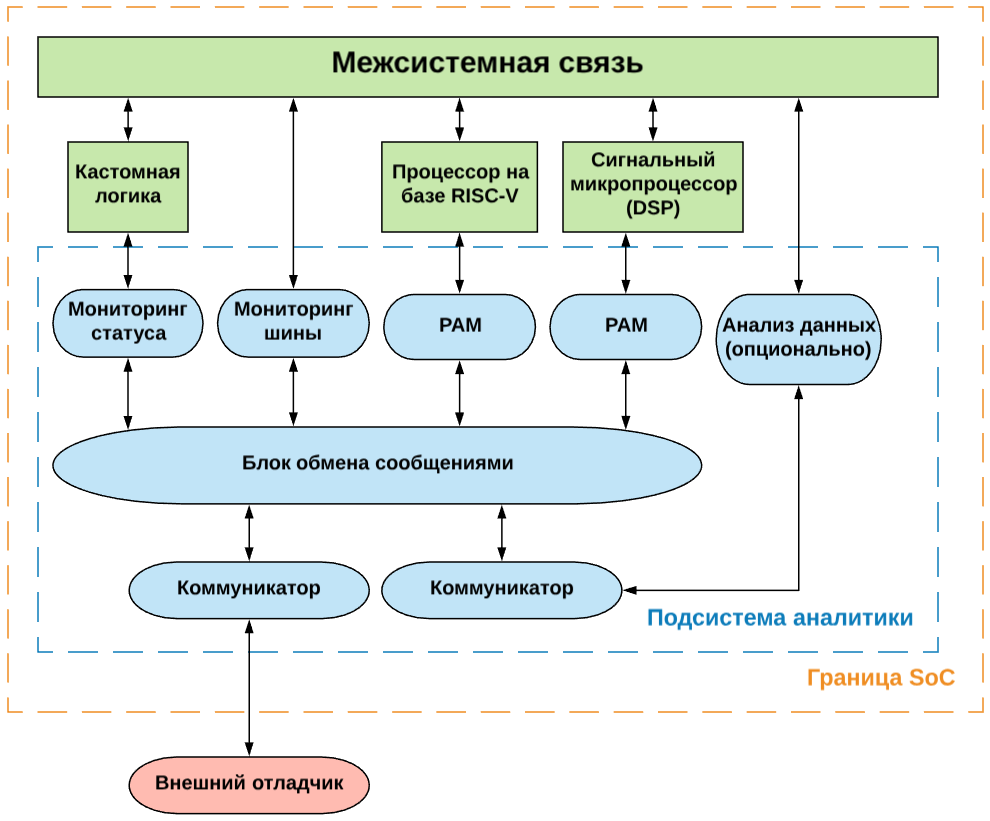

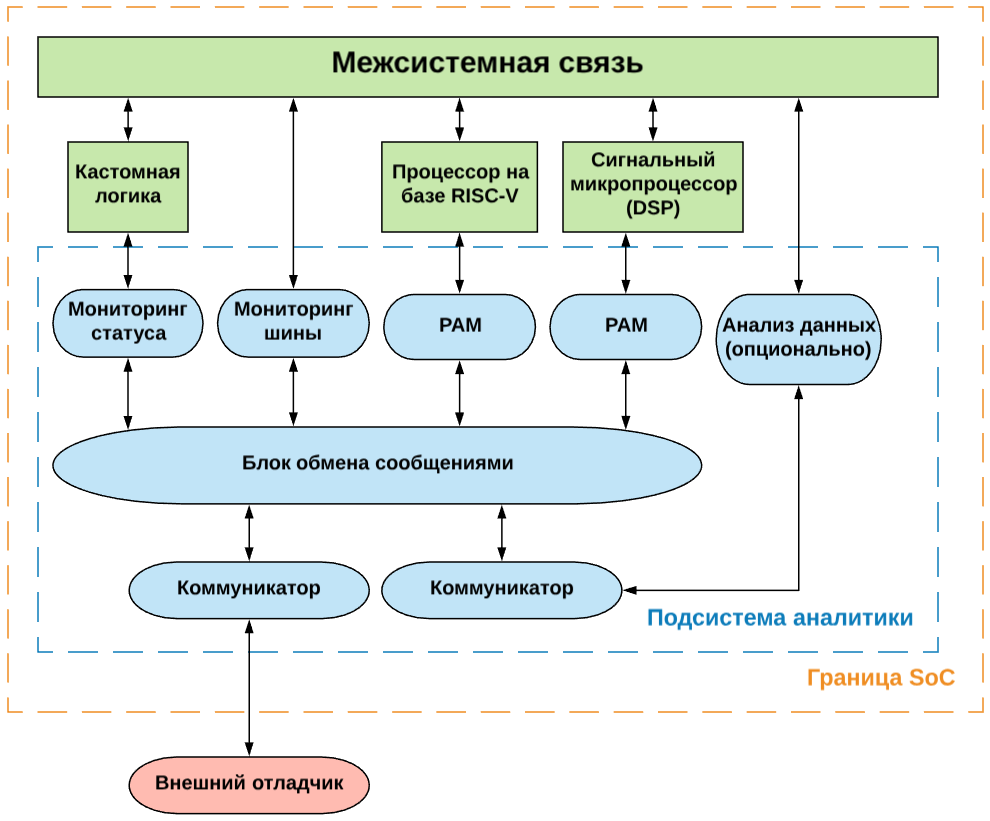

К примеру, для микропроцессоров на базе архитектуры RISC-V вся система может выглядеть следующим образом:

Полученные данные о состоянии компонентов чипа можно выводить через различные интерфейсы: USB, Ethernet, PCI-Express и даже Wi-Fi. После эту информацию можно загрузить в любую аналитическую систему для поиска аномалий в работе компонентов.

Разработчики из UltraSoC говорят, что их система найдет применение в дата-центрах и поможет облачным провайдерам мониторить масштабную облачную инфраструктуру. Так как параметры системы на кристалле отслеживаются с помощью аппаратных средств, которые (в отличие от программных) не оказывают влияние на производительность, операторы ЦОД смогут получать актуальные данные о состоянии серверов в реальном времени.

Но прежде чем технология найдет широкое применение, команде UltraSoC придется убедить производителей внедрить решение в свои чипы. Его реализация усложнит бизнес-процессы, приведет к удорожанию производства и увеличению цены микросхем. Поэтому многие компании могут отказаться, сославшись на то, что клиентам будет дешевле самостоятельно воспользоваться сторонним ПО для мониторинга.

Но ряд производителей все же хочет опробовать продукт. Например, в компании Esperanto собираются внедрить технологию UltraSoC в тысячу процессоров на базе RISC-V и ускорители AI/ML, чтобы отслеживать их производительность.

Другие организации тоже разрабатывают on-chip системы. В частности, специальные сенсоры для отслеживания напряжения и температуры (PVT — Process, Voltage, Temperature). Они заточены под работу в системах на кристалле и ASIC. В начале прошлого года Moortec заручились поддержкой производителя чипов TSMC и реализовали свою технологию в 12-нм микросхемах. В компании уверены, что процессоры с системами мониторинга «на борту» найдут применение в ЦОД, мобильных устройствах, системах ИИ, IoT и проч.

Еще один проект — «умные» PVT-сенсоры — стал результатом совместной работы компаний. Комбинация цифровых систем мониторинга и анализа UltraSoC и физических сенсоров Moortec позволяет комплексно отслеживать состояние SoC и оптимизировать нагрузку в режиме реального времени.

Разработчики из UltraSoC считают, что рост популярности высокотехнологичных решений (AI, ML, IoT), а также переход на гетерогенные системы сделают встроенные инструменты мониторинга незаменимыми.

В компании планируют сделать архитектуру решения более гибкой и настраиваемой. Для этого в UltraSoC начали разрабатывать UltraDevelop 2. Это — интегрированная среда разработки (IDE), с помощью которой можно конфигурировать, отлаживать и оптимизировать параметры компонентов чипа. Её релиз намечен на второй квартал 2019 года.

О чем мы пишем в корпоративном блоге:

Несколько постов из нашего Telegram-канала:

/ фото 83DegreesMedia CC BY

Зачем внедрять системы мониторинга в чип

Гетерогенные устройства строятся из нескольких блоков. Ими могут выступать процессоры, сопроцессоры или интегральные схемы ASIC. Специализация вычислительных модулей повышает производительность всей системы, но «многокомпонентный состав» приводит к сложностям с оптимизацией — каждому аппаратному блоку требуется настройка.

Проблема усугубляется, если чипы используются крупным дата-центром. Мониторинг обширной инфраструктуры — задача не из легких. Специализированные программные решения зачастую наносят ущерб эффективности работы вычислительных систем. К примеру, утилита для измерения пропускной способности канала iPerf снижает производительность сети на 10–15%.

Для решения этой проблемы UltraSoC внедрили инструменты для мониторинга прямо на чип. Компания разработала ряд логических полупроводниковых модулей, каждый из которых отвечает за одну из задач — мониторинг, отладку, обеспечение безопасности. Производители чипов могут использовать эти модули и вытраливать их на одной схеме с процессорами, GPU, сетевыми интерфейсами. Это позволяет собирать данные со всех компонентов микросхемы «на месте» без инвазивных программных решений. Эта технология уже адаптирована для работы со стандартными архитектурами: от ARM и RISC-V до MIPS и Xtensa.

Устройство системы

В UltraSoC предлагают порядка тридцати модулей, которые можно компоновать в зависимости от особенностей конкретной системы на кристалле (SoC). Модули делятся на три класса:

- Блоки аналитики — контролируют и мониторят компоненты микросхемы;

- Блоки обмена сообщениями — связывают модули UltraSoC между собой;

- Коммуникаторы — интерфейсы для связи с внешними системами и внутренними компонентами.

К примеру, для микропроцессоров на базе архитектуры RISC-V вся система может выглядеть следующим образом:

Полученные данные о состоянии компонентов чипа можно выводить через различные интерфейсы: USB, Ethernet, PCI-Express и даже Wi-Fi. После эту информацию можно загрузить в любую аналитическую систему для поиска аномалий в работе компонентов.

Потенциал и недостатки решения

Разработчики из UltraSoC говорят, что их система найдет применение в дата-центрах и поможет облачным провайдерам мониторить масштабную облачную инфраструктуру. Так как параметры системы на кристалле отслеживаются с помощью аппаратных средств, которые (в отличие от программных) не оказывают влияние на производительность, операторы ЦОД смогут получать актуальные данные о состоянии серверов в реальном времени.

Из-за того что технология оценивает работу низкоуровневых компонентов напрямую, она поможет быстрее определять причину так называемых гейзенбагов — «плавающих ошибок», которые сложно отловить из-за того, что они регулярно меняют свойства.

Но прежде чем технология найдет широкое применение, команде UltraSoC придется убедить производителей внедрить решение в свои чипы. Его реализация усложнит бизнес-процессы, приведет к удорожанию производства и увеличению цены микросхем. Поэтому многие компании могут отказаться, сославшись на то, что клиентам будет дешевле самостоятельно воспользоваться сторонним ПО для мониторинга.

Но ряд производителей все же хочет опробовать продукт. Например, в компании Esperanto собираются внедрить технологию UltraSoC в тысячу процессоров на базе RISC-V и ускорители AI/ML, чтобы отслеживать их производительность.

Альтернативные разработки

Другие организации тоже разрабатывают on-chip системы. В частности, специальные сенсоры для отслеживания напряжения и температуры (PVT — Process, Voltage, Temperature). Они заточены под работу в системах на кристалле и ASIC. В начале прошлого года Moortec заручились поддержкой производителя чипов TSMC и реализовали свою технологию в 12-нм микросхемах. В компании уверены, что процессоры с системами мониторинга «на борту» найдут применение в ЦОД, мобильных устройствах, системах ИИ, IoT и проч.

Еще один проект — «умные» PVT-сенсоры — стал результатом совместной работы компаний. Комбинация цифровых систем мониторинга и анализа UltraSoC и физических сенсоров Moortec позволяет комплексно отслеживать состояние SoC и оптимизировать нагрузку в режиме реального времени.

Что ждет технологию в будущем

Разработчики из UltraSoC считают, что рост популярности высокотехнологичных решений (AI, ML, IoT), а также переход на гетерогенные системы сделают встроенные инструменты мониторинга незаменимыми.

В компании планируют сделать архитектуру решения более гибкой и настраиваемой. Для этого в UltraSoC начали разрабатывать UltraDevelop 2. Это — интегрированная среда разработки (IDE), с помощью которой можно конфигурировать, отлаживать и оптимизировать параметры компонентов чипа. Её релиз намечен на второй квартал 2019 года.

О чем мы пишем в корпоративном блоге:

- Как разместить 100% инфраструктуры в облаке и не пожалеть об этом

- Бессерверные вычисления в облаке: тренд современности или необходимость?

- Почему компании используют виртуальные машины, а не контейнеры

Несколько постов из нашего Telegram-канала:

Комментарии (5)

andrey_aksamentov

07.03.2019 19:36+1Современные игры стали настолько реалистичны, что я в замешательстве.

Подскажите — это реальная фотография или рендер из игры?

dimonoid

07.03.2019 20:20У заклепок видна перспектива, значит реальное фото. В играх и даже рендерах такие мелкие детали почти никогда не детализируют в 3d, и оставляют в текстуре.

uncle_goga

Интересная разработка, правда сразу встает вопрос о безопасности таких решений, какое то левое устройство вмонтированное сразу в чип

Brak0del

На сайте производителя пишут

. Т.е. вроде как монтировать и выбирать, что и как мониторить, будут клиенты. По-моему, по уровню доверия/безопасности и модели использования это похоже на обычное IP-ядро.amartology

Это и есть обычное IP-ядро, полностью (наверное) понятное разработчику чипа и одобренное им. По сути — очень навороченный JTAG, который можно запускать, не отключая основную функциональность чипа. Собственно, вопрос безопасности использования — это вопрос к разработчику чипа. Так-то и трехногий линейный регулятор можно сделать так, что он опасен будет, дело не в использованных IP.