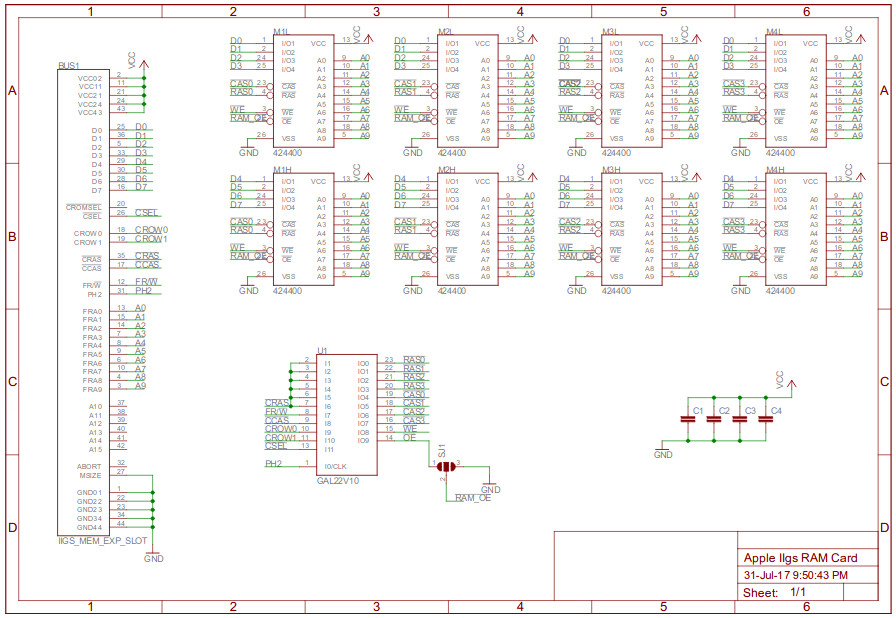

Предлагаемая плата расширения ОЗУ для компьютера Apple IIgs выполнена на микросхемах NEC uPD424400-70 от нескольких 1-мегабайтных SIMM-модулей. Каждая из таких микросхем хранит 1 М полубайт и размещена в 26-выводном корпусе типа SOJ.

Компьютер Apple IIgs выполнен на процессоре 65C816 — 16-битном, но с 8-битной шиной данных. Плата расширения содержит 4 МБ ОЗУ. Память поделена на четыре строки, по 1 МБ в каждой. Строка состоит из двух микросхем по 1 М полубайт, таким образом, всего потребовалось восемь микросхем.

Слот для платы расширения ОЗУ у компьютера уже есть. На него выведены все необходимые сигналы, регенерацию динамического ОЗУ компьютер также берёт на себя. Поэтому плата расширения получилась достаточно простой. Автор решил сделать плату малогабаритной, так как от этого зависит стоимость её изготовления, а также поместить всю логику в ПЛИС GAL22V10.

На слоте расширения ОЗУ присутствуют следующие сигналы:

FRA0-FRA9 — 10-битный мультиплексированный адрес ячейки, подаётся непосредственно на адресные входы микросхем динамического ОЗУ

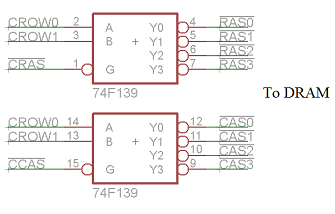

CROW0, 1 — два бита для выбора одной из четырёх строк

/CRAS — сигнал стробирования адреса строки динамического ОЗУ

/CCAS — сигнал стробирования адреса столбца динамического ОЗУ

FR/W — разрешение записи в ОЗУ, этот сигнал требует дополнительной обработки, см. ниже

D0-D7 — шина данных, соединяется непосредственно с линиями ввода-вывода микросхем ОЗУ

/CSEL — на этой линии при чтении из ОЗУ появляется логическая единица, его надо инвертировать и подать на входы /OE микросхем ОЗУ

MSIZE — сообщает компьютеру объём строки: единица — 256 кБ, нуль — 1 МБ, здесь эта линия соединена с общим проводом

14M, PH2CLK, A10-A15 — в предлагаемой плате не задействованы

Сигналы /CRAS и /CCAS нужно демультиплексировать, чтобы получить отдельные сигналы /RAS и /CAS для каждой из строк. Для этого подойдёт микросхема 74F139 (здесь и далее подразумевается, что отдельных микросхем на плате не будет, вместо них будет одна общая ПЛИС).

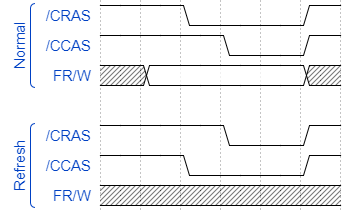

Сигнал FR/W нельзя подавать непосредственно на вход /WE микросхем динамического ОЗУ, и вот почему. При обычной операции чтения-записи вначале становится активной (что соответствует логическому нулю) линия /RAS, затем — линия /CAS. При цикле регенерации динамического ОЗУ, наоборот, сначала активной становится линия /CAS, затем /RAS. Но применённые микросхемы требуют, чтобы на линии /WE появлялась единица до того, как линия /RAS станет активной. А сигнал FR/W, поступающий от Apple IIgs, этому требованию не соответствует. Состояние FR/W во время цикла регенерации — неопределённое. Стало быть, требуется схема, обнаруживающая цикл регенерации и подающая единицу на /WE.

Первым делом надо выявить цикл регенерации. Ниже приведена временная диаграмма:

Идея автора состоит в применении «прозрачной» защёлки. Сигнал /CRAS для неё является входным, /CCAS — сигналом защёлкивания. Когда на /CCAS единица, устройство пропускает через себя входной сигнал насквозь: состояние выхода меняется вслед за состояние входа. В момент перехода /CCAS с единицы на нуль защёлка запоминает сигнал на входе, и теперь он на выходе не меняется. При обычной операции чтения-записи на /CRAS присутствует нуль в момент переключения /CCAS с единицы на нуль. А при цикле регенерации на /CRAS присутствует единица также в момент переключения /CCAS на нуль. Затем, когда /CCAS переключается обратно в единицу, защёлка снова становится «прозрачной». Напоминает фантастический цветок из «Тайны третьей планеты», который может быть и «зеркалом», и «фотоаппаратом».

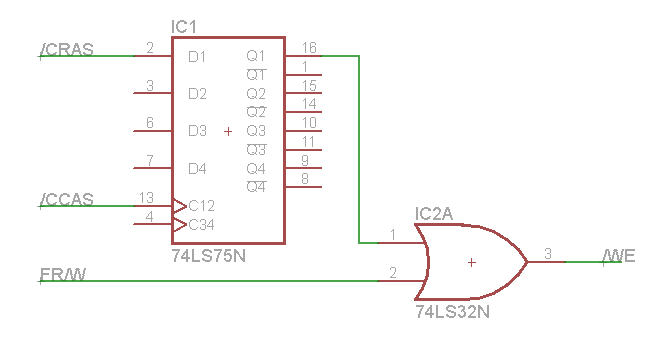

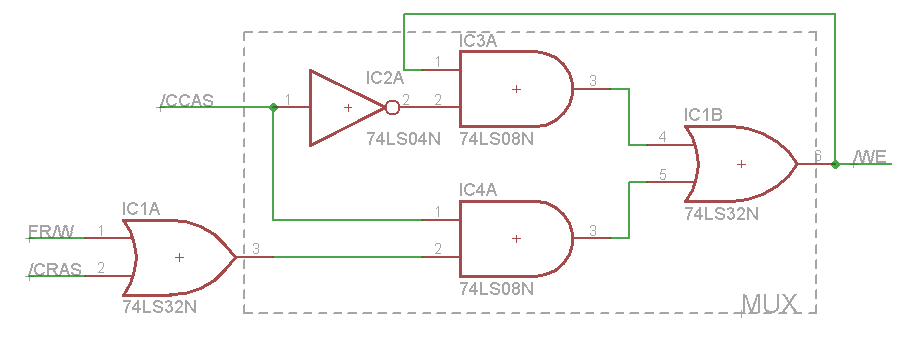

Вначале автор составил такую схему:

Но для её переноса в ПЛИС GAL22V10 потребуются два выходных вывода. Поэтому схему пришлось упростить. При нормальной работе сигнал FR/W принимает требуемое значение до защёлкивания, поэтому так тоже можно.

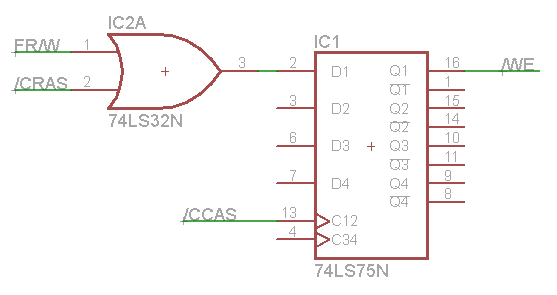

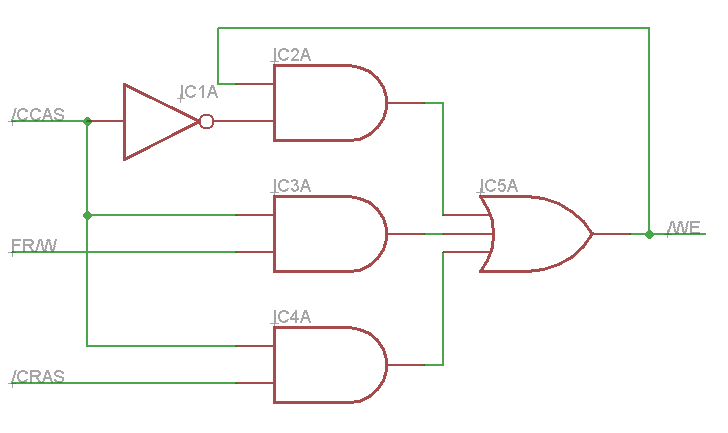

«Прозрачную» защёлку можно сделать из мультиплексора, а его, в свою очередь — из логических элементов. Схема становится такой:

А после упрощения — такой:

Этот вариант и перенесён в ПЛИС. Для компиляции автор применил WinCUPL. Эта программа лежит на сайте Atmel. Она сырая и постоянно вылетает, но с задачей справилась отлично. Программатор — Genius G540.

Перемычка SJ1 на плате действует так. Если соединены штырьки 1 и 2, сигнал /OE проходит через ПЛИС. Если соединены штырьки 2 и 3, он соединён с общим проводом. Автор не был уверен, что схема выявления цикла регенерации заработает. Поэтому он добавил данную перемычку на случай, если конфигурацию ПЛИС придётся переделать.

Поскольку оказалось, что всё работает, штырьки впаивать не надо, просто соедините выводы 1 и 2 каплей припоя.

Чтобы уменьшить размеры платы, автор применил по одному конденсатору по питанию на каждые четыре микросхемы ОЗУ, а сами микросхемы разместил с обеих сторон платы.

Микросхемы в корпусах SOJ трудно впаивать, а особенно — выпаивать паяльником. Автор рекомендует пользоваться феном.

Правильно разверните микросхемы. На нижней строке они перевёрнутые. Вывод 1 смотрит вниз.

Некоторые сквозные отверстия расположены слишком близко к площадкам. Не замкните их припоем между собой.

А площадки 1 и 2 для перемычки, наоборот, замкните.

Конденсаторы C1 — C3 имеют ёмкость в 0,1 мкФ, C4 — 10 мкФ.

Платы автор заказывал на OSH Park. Применено покрытие ENIG — золотое, но очень тонкое. Для игровых картриджей не годится — быстро сотрётся. А здесь плату поместили в слот один раз и больше оттуда не удаляют.

Автор благодарит GGLabs за схему аналогичной платы, она очень помогла, спасибо!

Готовая схема получилась такой:

Файлы:

Прошивка ПЛИС GAL22V10, применена программа WinCUPL версии 5.30.4

Плата, применена программа Eagle версии 7.1

Схема в PDF

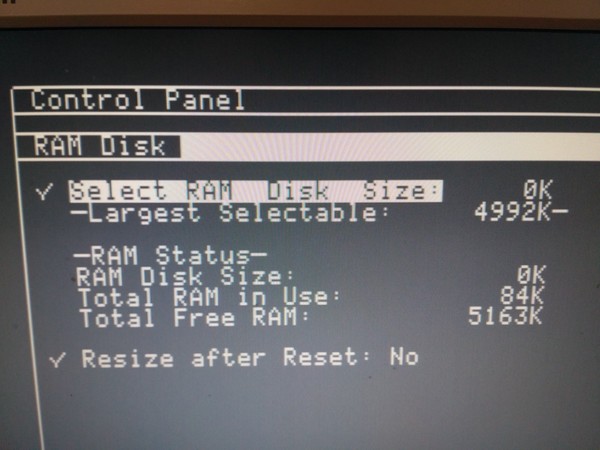

Заработало!

sim2q

ps в плате на распайку несколько GAL20VBA, вот думаю что же можно сделать аж на целых 8 OLMCs?:)