Очередная глава из официальной документации Cypress про управление тактированием и сбросом. Как уже упоминалось в первой статье этого цикла, этот модуль обеспечивает выбор и разрешение тактирования, а также выбор сброса внутри UDB. Подробнее — под катом.

Предыдущие статьи цикла:

UDB. Что же это такое? Часть 1. Введение. PLD.

UDB. Что же это такое? Часть 2. Datapath.

UDB. Что же это такое? Часть 3. Datapath FIFO.

UDB. Что же это такое? Часть 4. Datapath ALU.

UDB. Что же это такое? Часть 5. Datapath. Полезные мелочи.

UDB. Что же это такое? Часть 6. Модуль управления и статуса.

21.3.4 Модуль управления тактированием и сбросом (Reset and Clock Control Module)

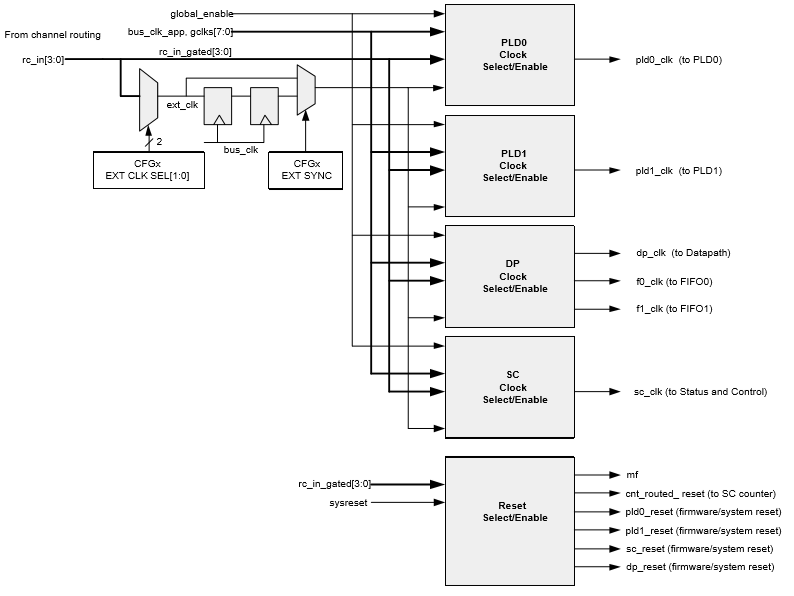

Основная функция этого модуля заключается в выборе тактовых сигналов из доступных глобальных тактовых сигналов или тактового сигнала шины для каждой PLD, Datapath и модуля управления и статуса. Модуль также поддерживает динамические и программные сбросы блоков UDB. Как показано на рисунке 21-38, имеется четыре блока управления тактированием и один блок управления сбросом. Четыре входа (RC_IN[3:0]) доступны для проброса из глобальной трассировочной матрицы. Каждый блок управления тактированием может выбрать источник для входа разрешения тактирования из этих трассировочных входов, а также имеется мультиплексор, позволяющий выбрать один из трассировочных входов для использования в качестве внешнего источника тактового сигнала. Как видно на рисунке, выбор внешнего источника тактирования может быть синхронизирован. Для каждого компонента UDB существует 10 тактовых сигналов на выбор: 8 глобальных цифровых тактовых сигналов, тактовый сигнал шины и выбранный внешний тактовый сигнал (ext clk). Любой из трассированных входных сигналов (rc_in) может быть использован либо в качестве активатора, чувствительного к уровню, либо в качестве активатора, чувствительного к перепаду. Функция сброса этого блока обеспечивает трассированный сброс блоков PLD и счетчика SC, а также возможность программного сброса каждого блока для поддержки реконфигурации.

Тактовый сигнал шины, подаваемый на вход модуля управления тактированием и сбросом отличается от тактового сигнала системной шины. Этот сигнал называется «bus_clk_app» и запирается так же, как прочие цифровые тактовые сигналы. Тактовый же сигнал системной шины используется только для операций ввода-вывода и автоматически отпирается для каждого доступа. Генератор тактовых сигналов Datapath вырабатывает три тактовых сигнала: один для Datapath и по одному сигналу для каждого FIFO.

Рисунок 21-38. Модуль управления тактированием и сбросом.

21.3.4.1 Управление тактированием

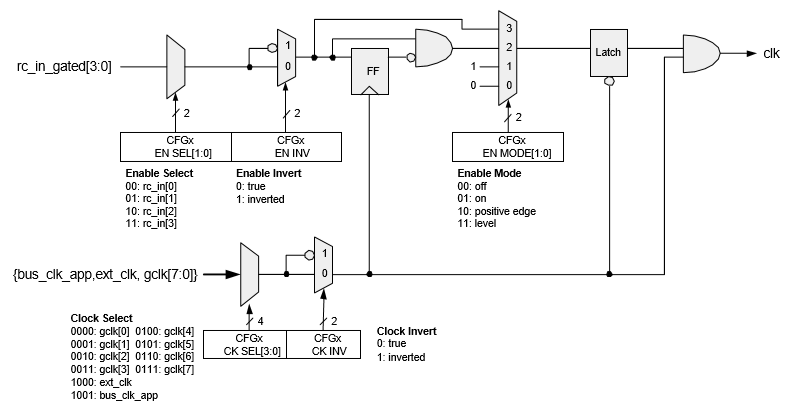

Рисунок 21-39 показывает пример схемы выбора и разрешения тактирования. В каждом UDB есть четыре таких схемы: по одной на каждый блок PLD, одна схема для Datapath и одна для блока управления и статуса. Основными компонентами этой схемы являются мультиплексор выбора глобального тактирования, инвертор тактирования, мультиплексор выбора разрешающего сигнала тактирования, инвертор разрешающего сигнала тактирования и логика обнаружения перепада.

Рисунок 21-39. Управление выбором/активацией тактирования.

Выбор тактирования (Clock Selection)

Существует восемь глобальных цифровых тактовых сигналов, проброшенных на все UDB. Любой из них может быть выбран. Глобальные цифровые тактовые сигналы являются выходами делителей частот, выбранных пользователем. См. «Система тактирования» на стр. 109 оригинала. Другим вариантом выбора является тактовый сигнал шины, который имеет наивысшую частоту в системе. Этот сигнал называется «bus_clk_app» и трассируется отдельно от тактового сигнала системной шины. Кроме того, для поддержки функций с прямым тактовым сигналом (например, SPI) внешняя трассировочная линия может быть выбрана в качестве входного тактового сигнала. Поскольку функции приложения привязаны к произвольным границам внутри UDB, выбор индивидуального тактового сигнала для каждого подкомпонента UDB способствует точной гранулярности при программировании.

?

Инверсия тактирования (Clock Inversion)

Выбранный тактовый сигнал может быть инвертирован. Это ограничит максимальную частоту работы из-за существования участков с тактом в половину периода. Одновременные запись шины и внутренние записи (например, программная запись нового значения счетчика во время его работы) не поддерживаются, когда внутреннее тактирование инвертировано и имеет такую же частоту, как и тактирование шины. Это ограничение затрагивает A0, A1, D0, D1, а также регистр управления в режиме счетчика.

Выбор разрешения тактирования (Clock Enable Selection)

Разрешающий сигнал тактирования может быть проброшен на любой синхронный сигнал и выбран на любом из четырех входов трассировочной матрицы, доступных этому блоку.

Инверсия разрешения тактирования (Clock Enable Inversion)

Сигнал разрешения тактирования может быть инвертирован. Благодаря этому, данный сигнал может вырабатываться в любой полярности.

Режимы разрешения тактирования (Clock Enable Mode)

По умолчанию режим работы разрешения тактирования имеет значение OFF. После настройки работы целевого блока программное обеспечение может установить один из описанных ниже режимов работы при помощи регистра CFGxEN MODE[1:0], показанного на рисунке 21-39.

Таблица 21-23. Режимы разрешения тактирования.

| Режимы разрешения тактирования | Описание |

|---|---|

| OFF | Тактирование отключено. |

| ON | Тактирование включено. Выбранное глобальное тактирование работает свободно. |

| Positive Edge | Пропускаемый тактовый импульс вырабатывается по каждому положительному перепаду на входе разрешения. Максимально допустимая частота на входе разрешения равна половине частоты тактового сигнала. |

| Level | Тактовые импульсы генерируются, пока вход разрешения тактирования имеет высокий уровень (‘1’). |

Использование разрешения тактирования

Существует два распространенных сценария использования разрешения тактирования.

Программное разрешение (Firmware Enable): предполагается, что большинство функций требуют программного разрешения тактирования для запуска и остановки функции. Так как граница функции, привязанной к массиву UDB, условна, функция может охватывать несколько UDB и/или частей UDB. Следовательно, необходим способ включения каждой функции атомарно. Обычно это реализовано при помощи бита в регистре управления, проброшенного на один или несколько входов разрешения тактирования. Этот сценарий также поддерживает случай, когда приложениям необходимо одновременно запустить несколько несвязанных блоков.

Эмуляция локальной выработки тактового сигнала (Emulated Local Clock Generation): эта функция позволяет UDB генерировать локальные тактовые сигналы и распределять их на другие UDB в массиве при помощи шаблона реализации активации синхронного тактирования, вместо того, чтобы напрямую тактировать каждый UDB отдельно. Использование функции Positive Edge для входа разрешения снимает ограничения на скважность сигнала разрешения.

Особое тактирование FIFO

Блоки FIFO Datapath имеют особенности тактирования. По умолчанию, тактирование FIFO имеет такую же конфигурацию, как и тактирование Datapath. Однако блоки FIFO имеют особые биты управления, которые меняют конфигурацию тактирования:

- каждый тактовый сигнал FIFO может быть инвертирован относительно полярности выбранного тактирования Datapath;

- когда выбран режим FIFO FAST, тактирование шины заменяет выбор тактирования Datapath, которое обычно использует FIFO.

21.3.4.2 Управление сбросом

Существует два режима управления сбросом: унаследованный и стандартный. Режим задается при помощи бита ALT RES в каждом регистре конфигурации UDB CFG31. По умолчанию бит имеет значение 0 (унаследованный режим); рекомендуется присвоить ему значение 1 (стандартный режим). Стандартный режим имеет большую степень детализации – отдельные блоки внутри UDB могут использовать трассируемые сбросы. Для информации об унаследованном режиме свяжитесь с Cypress.

Управление сбросом PLD (PLD Reset Control)

Рисунок 21-40 показывает систему сброса PLD.

Рисунок 21-40. Структура сброса PLD.

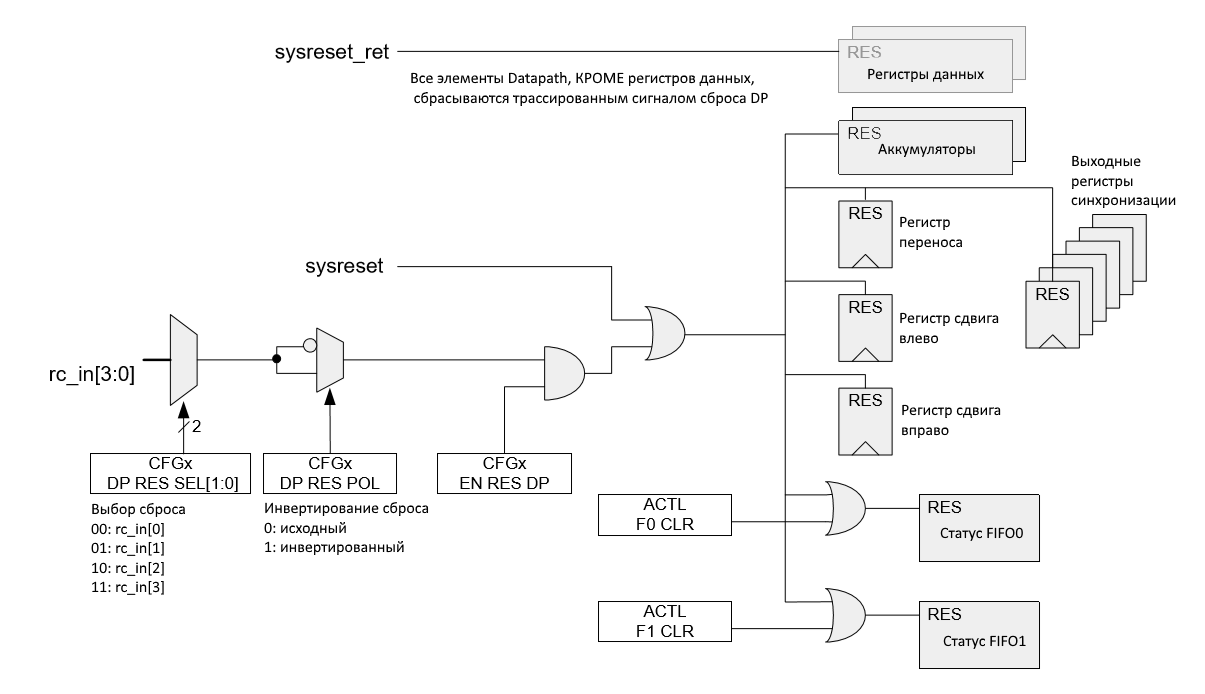

Управление сбросом Datapath (Datapath Reset Control)

Рисунок 21-41 показывает систему сброса Datapath. Трассированный сброс применяется ко всем регистрам и состояниям Datapath кроме регистров данных D0 и D1. Регистры данных являются сохраняющимися регистрами. Содержимое FIFO не определено после сброса, так как располагается в ОЗУ.

Рисунок 21-41. Структура сброса Datapath.

Управление сбросом управления и статуса (Status and Control Reset Control)

Рисунок 21-42 показывает систему сброса управления и статуса. Регистры управления/счетчика и статуса имеют общий трассированный сброс, однако включаются они отдельно. Регистры наложения маски/периода и вспомогательного управления являются регистрами сохранения.

Рисунок 21-42. Управление сбросом управления и статуса.

21.3.4.3 Инициализация UDB при включении (POR)

Инициализация регистров и состояний (Register and State Initialization)

Таблица 21-24. Инициализация состояний UDB при включении

| Элемент состояния | Расшифровка элемента состояния | Состояние при включении |

|---|---|---|

| CFG 0 – 31 | Конфигурационные защелки | 0 |

| Ax, Dx, CTL, ACTL, MSK | Аккумуляторы, регистры данных, вспомогательный регистр управления, регистр наложения маски | 0 |

| ST, MC | Регистры статуса и макроячейки (только для чтения) | 0 |

| DP CFG RAM & Fx (FIFO) | ОЗУ конфигурации Datapath и ОЗУ FIFO | Неизвестно |

| PLD RAM | ОЗУ конфигурации PLD | Неизвестно |

Инициализация трассировки

При включении состояние входов и выходов трассировки имеет следующие особенности:

- все выходы UDB, которые направляют данные на трассировочную матрицу удерживаются в состоянии ‘0’;

- все драйверы выходящие из трассировки и попадающие на входы UDB изначально занулены.

Такая инициализация позволяет избежать конфликтующих состояний при трассировке, и начальное конфигурирование происходит в последовательности, при которой порядок не играет роли.

Окончание следует. Мы готовим

vchs

Очень хороший цикл статей получился. И UDB хорошая задумка, позволяет помимо прочего замыкать разные модули друг на друга с организацией такого автономного конечного автомата. Сподвиг ваш цикл статей меня в нем разобраться. Но вот качество документации у Cypress после ST или TI просто убивает. Долго и нудно я пытался воспользоваться тригером DMA у 4 серии пока через 2 месяца шатаний по форумам мне не сказали что он, тригер, конечно есть, но работает не так как у 5 серии, а как не так в документации забыли указать. Ну а вы работу провели отличную, спасибо.

EasyLy Автор

Стиль документации Кипариса — отдельная грустная песня. Я выл от их стиля ещё когда FX2LP изучал. Причём в итоге оказалось, что про FX2LP у них написано всё, но как оно тяжело читалось! Тут же и описано не всё. И когда мы этот перевод делали — у нас целые дискуссии возникали, что именно имели в виду авторы в той или иной фразе. Так что частично наш перевод чуть отличается на уровне слов от оригинала. Но не на уровне мыслей. Где сохранить мысль в духе оригинала было невозможно — появлялись примечания переводчика…