Всем привет, меня зовут Вячеслав. Я занимаюсь разработкой печатных плат 5 лет, и за это время не только прочитал множество правил и рекомендаций по трассировке, но и находил первоисточники и работал с ними.

В сложных вычислительных системах, которые разрабатывает компания YADRO, высокоскоростные сигналы на пути от передатчика к приёмнику преодолевают значительные расстояния, проходя сквозь несколько плат и делая десяток межслойных переходов. В таких условиях, каждое небрежно спроектированное переходное отверстие будет вносить свой небольшой вклад в ухудшение сигнала, и в результате интерфейс может не заработать.

Целостность сигнала

Переходные отверстия (далее п/о, англ. via) представляют собой неоднородности в линии передачи. Как и другие неоднородности, они портят сигнал. Этот эффект слабо выражен на низких частотах, однако с увеличением частоты значительно возрастает. Часто разработчики уделяют незаслуженно мало внимания структуре переходных отверстий: они могут быть скопированы из «соседнего» проекта, взяты из даташита или вообще не заданы в САПР (настройка по умолчанию).

Перед тем как использовать рассчитанную структуру, необходимо понять, почему её сделали именно такой? Слепое повторение может только навредить.

На целостность сигнала в канале при прохождении через переходные отверстия главным образом влияют следующие факторы:

- отражения сигнала из-за изменения волнового сопротивления;

- деградация сигнала вследствие паразитной ёмкости и индуктивности;

- отражения от неиспользуемого отрезка п/о при переходе на внутренний слой (далее стаб от англ. via stub);

- перекрёстные помехи (англ. Cross talks);

- помехи в шинах питания.

Рассмотрим подробнее причины этих эффектов и методы их устранения.

Фактор 1. Волновое сопротивление п/о

В идеально спроектированной плате волновое сопротивление не меняется на всем протяжении трассы, в том числе и при переходе на другой слой. В реальности это обычно выглядит примерно так:

Рисунок 1. Изменение волнового сопротивления при переходе на другой слой.

Чем лучше согласованы волновые сопротивления, тем меньше будет отражение сигнала. Как же повлиять на это?

Рассмотрим структуру п/о на плате [1].

Рисунок 2. Структура п/о на плате.

| Слой | Элемент | Свойство |

|---|---|---|

| TOP | Площадка п/о | Паразитная ёмкость между площадкой и полигоном питания L2 |

| TOP-L2 | отрезок п/о | Индуктивность |

| L2 (полигон питания) | Антипад | Антипад образует краевую ёмкость – емкость между стенками п/о и полигоном питания |

| L2-L3 | Отрезок п/о | Индуктивность |

| L3 (полигон питания) | Антипад | Антипад образует краевую ёмкость – емкость между стенками п/о и полигоном питания |

| L3-L4 | Отрезок п/о | Индуктивность |

| L4 (сигнальный) | Площадка п/о | Паразитная ёмкость между площадкой п/о и полигоном питания L3 |

| L4-L5 | Стаб | Источник шума |

Изменяя элементы п/о, мы изменяем волновое сопротивление перехода. Наша цель – согласовать импеданс переходной структуры с импедансом проводников для минимизации отражений. Рассмотрим, как изменится импеданс при изменении элементов структуры п/о.

| Элемент | Действие | Электрическое свойство | Импеданс (результат) |

|---|---|---|---|

| Площадка п/о | v | Cv | ^ |

| Диаметр п/о | v | L^ | ^ |

| Антипад | ^ | Cv | ^ |

| Длина п/о | ^ | L^ | ^ |

| Количество полигонов питания на пути п/о | v | Cv | ^ |

| Шаг п/о | ^ | Cv | ^ |

| Расстояние до возвратных п/о | ^ | L^ | ^ |

| Количество возвратных п/о | ^ | Lv | v |

| Заполнение отверстий | Заполняем смолой (Dk^) | С^ | v |

Фактор 2. Паразитная индуктивность и ёмкость

Проводники на печатной плате можно изготовить с волновым сопротивлением, лежащим в широком диапазоне, однако чаще всего это 50 Ом. С одной стороны, это связано с исторической преемственностью: импеданс 50 Ом был стандартизирован для коаксиальных кабелей как компромисс между уровнем нагрузки драйвера и потерей энергии сигнала. С другой стороны, 50-Омный проводник легко изготовить на типовой плате.

Для разработчика важным является не столько конкретное значение волнового сопротивления, сколько его постоянство на всём протяжении линии передачи.

Для того, чтобы сделать линию передачи с фиксированным значением волнового сопротивления, разработчик подбирает ширину дорожки и расстояние до опорного слоя, т.е. меняет погонную ёмкость и индуктивность линии передачи до определённой величины.

В п/о индуктивная составляющая довольно значима. В первом приближении, мы должны, в рамках разумного, максимально снизить паразитную индуктивность, а затем менять параметры п/о для достижения заданной емкости, и соответственно импеданса.

Чрезмерное уменьшение ёмкости п/о будет причиной локального повышения импеданса и, как следствие, отражений сигнала.

Фактор 3. Via stub

Что происходит, когда сигнал проходит через переходное отверстие со стабом?

Рисунок 3. Переходное отверстие со стабом, резонанс на ? длины волны.

В нашем примере сигнал распространяется сверху вниз со слоя Top. Дойдя до внутреннего сигнального слоя, сигнал разделяется: часть движется вдоль трассы на внутреннем слое, а часть продолжает движение вниз по переходному отверстию, затем отражается от слоя Bottom. После того, как отражённый сигнал достиг внутреннего слоя, он снова разделяется, часть движется вдоль трассы, а часть возвращается к источнику.

Отражённый сигнал будет суммироваться с исходным и искажать его, что будет выражаться в сужении окна на глазковой диаграмме, и увеличении уровня вносимой потери (англ. Insertion Loss).

В худшем случае, отрезок TD окажется равным ? длины волны сигнала, тогда отражённый сигнал достигнет трассы на внутреннем слое с задержкой в половину периода, наложившись на исходный сигнал в противофазе.

При анализе целостности рекомендуется рассматривать полосу пропускания шириной 5 частот Найквиста. Хорошим приближением будет считать приемлемым стаб, дающий резонанс на 7 гармонике и выше [2].

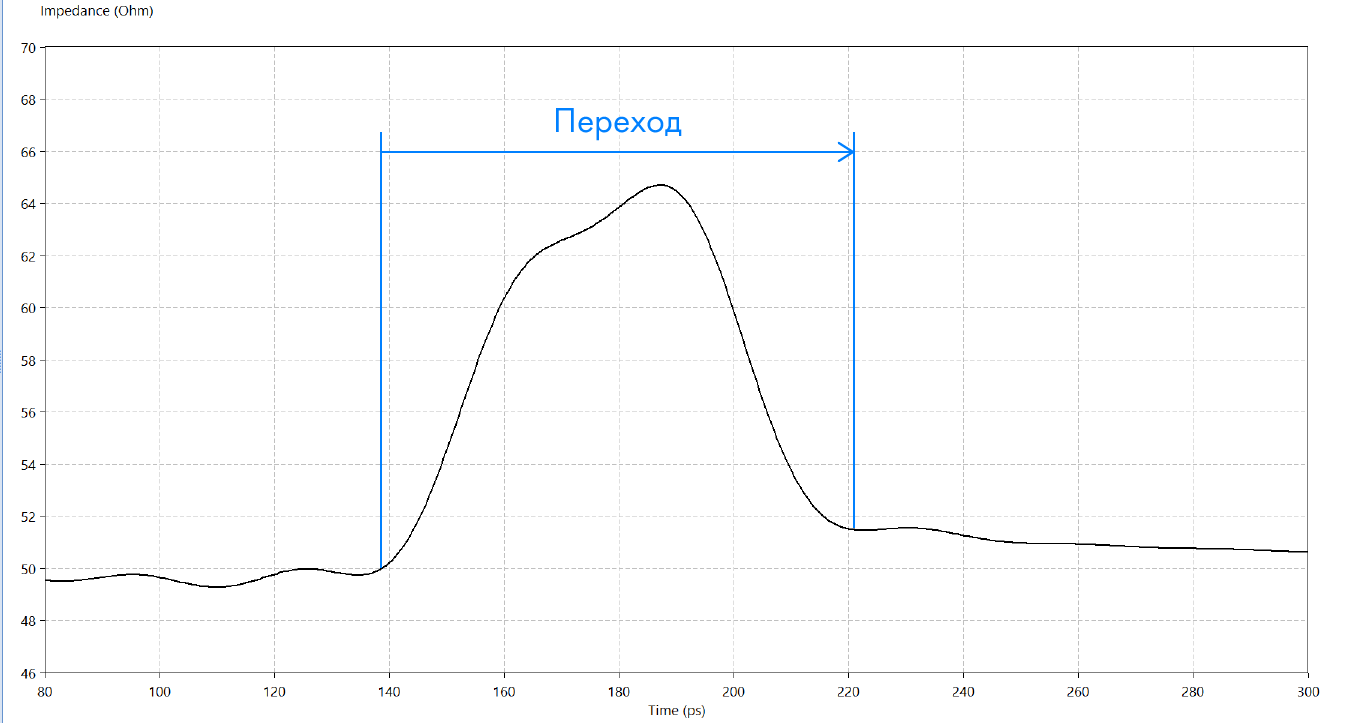

Рисунок 4. График уровня вносимых потерь для п/о со стабами 0, 0.65, 1.2 мм.

На рисунке 4 изображён огромный резонанс на частотах около 24 ГГц. Мы можем сделать вывод, что, если наш сигнал работает на частоте 2–3 ГГц, мы можем себе позволить не устранять стаб, поскольку в пределах 7 гармоник «всё спокойно».

Произвести быструю оценку критичности стаба можно в калькуляторе Polar:

Рисунок 5. Изображение с сайта polarinstruments.com. Длина стаба 2.5 мм допустима для сигналов с временем нарастания более 500 пс.

Чуть более точный результат дают формулы, приведённые в статье [2]. Они учитывают геометрию п/о и позволяют рассчитать поправку для диэлектрической проницаемости диэлектрика по оси Z.

Устранить стаб можно с помощью операции «обратное высверливание» (англ. Backdrilling), либо используя микропереходы (англ. blind and buried vias). Выбор зависит от особенностей проекта. Обратное высверливание проще и дешевле. После изготовления платы, сверлом большего диаметра стаб высверливается на заданную глубину. От разработчика требуется задать дополнительные отступы топологии в зоне высверливания, а также доступно для производителя указать требования по высверливанию в конструкторской документации. Современные САПР поддерживают данный функционал.

Микропереходы в первую очередь предназначены для плат высокой плотности (англ. HDI), однако в некоторых случаях их можно использовать, нивелировав дороговизну отказом от обратного высверливания и снижением количества слоёв на плате. При разработке плат HDI следует помнить некоторые особенности:

- каждый новый тип п/о увеличивает стоимость платы;

- для лазерного сверления используются специальные оптимизированные препреги, свойства которых могут отличаться;

- металлизация глухих отверстий увеличивает толщину меди на внутренних слоях.

Крайне рекомендуется заранее согласовать структуру платы с изготовителем.

Фактор 4. Перекрёстные помехи

Перекрёстные помехи – нежелательная передача сигнала из одной линии в соседнюю. Эта передача происходит, потому что два близко расположенных проводника имеют ёмкостную и индуктивную связь.

Характер перекрёстных помех сигнальных проводников и п/о немного отличается.

В п/о у сигнала нет опорного слоя, возвратные токи текут по соседним п/о, образуя большую петлю. Перекрёстные помехи сигналов в п/о обусловлены индуктивной составляющей.

Наибольшего эффекта по минимизации перекрёстных помех можно достичь, увеличив расстояние между п/о. Однако часто тополог не располагает большим пространством.

Сближение п/о в дифференциальной паре не только уменьшает занимаемую площадь, но и положительно сказывается на помехоустойчивости [3].

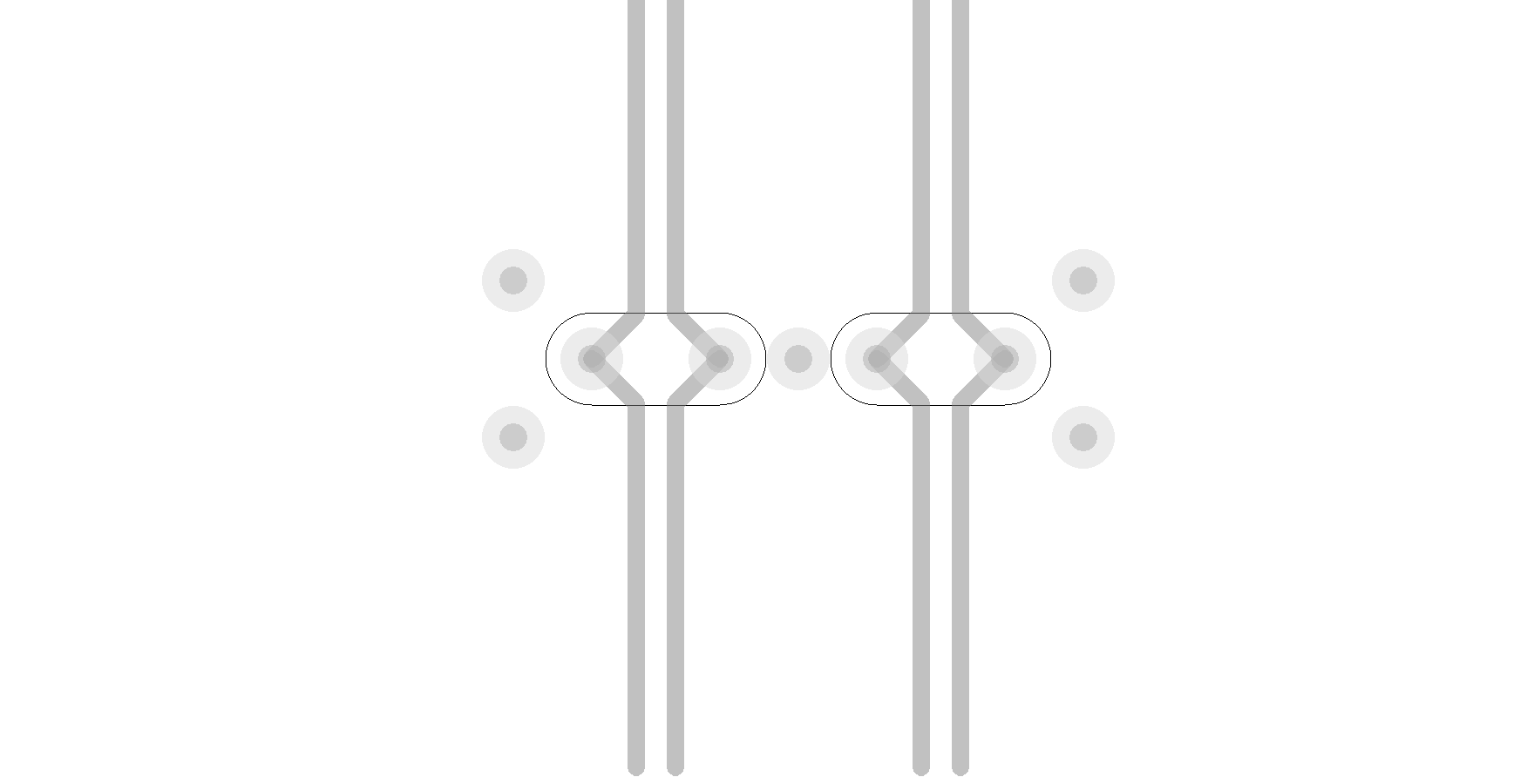

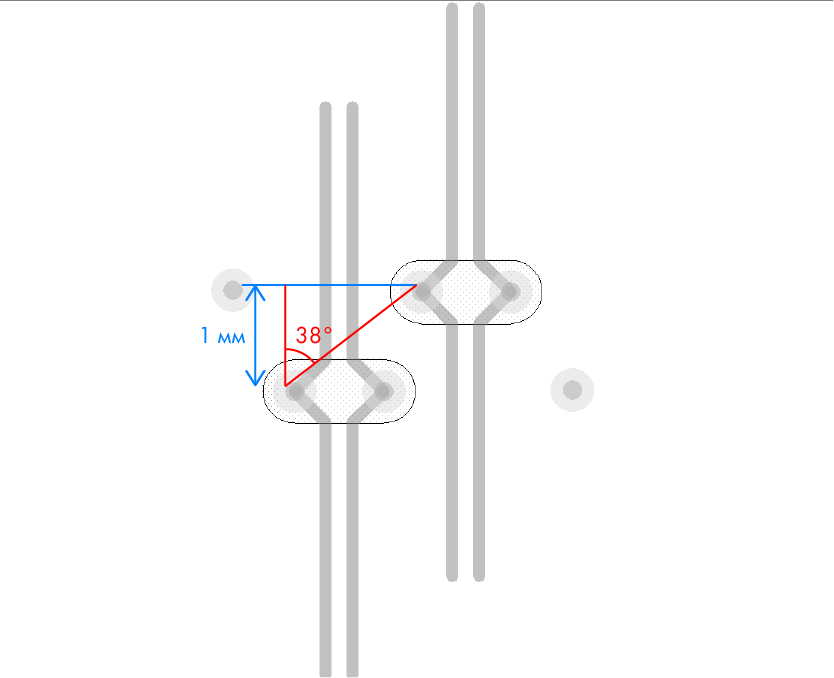

Общепринятый способ по минимизации перекрёстных помех между соседними сигнальными п/о — поместить экранирующее п/о между ними. При таком способе потребуется вести сигналы с шагом около 2 мм (Рисунок 6). Если места недостаточно, можно использовать меньший шаг со сдвигом (англ. Staggered pattern), как на рисунке 7. С помощью моделирования можно подобрать идеальный угол сдвига [4].

Рисунок 6. Минимизация перекрёстных помех с помощью экранирующего п/о.

Рисунок 7. Минимизацию перекрёстных помех с помощью диагонального «шахматного» сдвига.

Перекрёстные помехи можно также снизить экзотическими методами, например, длинным стабом (за счёт смещения индуктивно-ёмкостного баланса п/о) [5]. Также помехи можно уменьшить на стадии проектирования корпуса микросхемы [6].

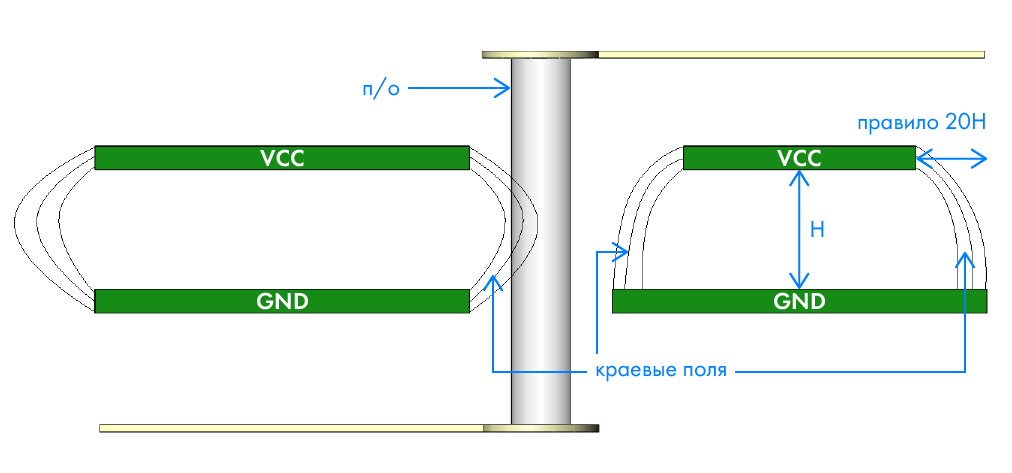

Фактор 5. Помехи в шинах питания

Помимо соседних сигнальных цепей, на качество сигнала могут оказывать помехи из внутренних слоёв.

По полигонам питания могут протекать большие токи. В силу увеличения индуктивности у краев полигонов, протекающие токи формируют краевые поля (англ. Fringing fields) по всем границам полигона, в том числе и в вырезах. Краевые поля являются источником электромагнитного излучения (англ. Edge-fired emission) в пространство. Для снижения эмиссии электромагнитного излучения, применяется правило 20H (Рисунок 8), который заключается в сужении полигона питания по отношению к полигону земли.

Рисунок 8. Краевые поля и правило 20H.

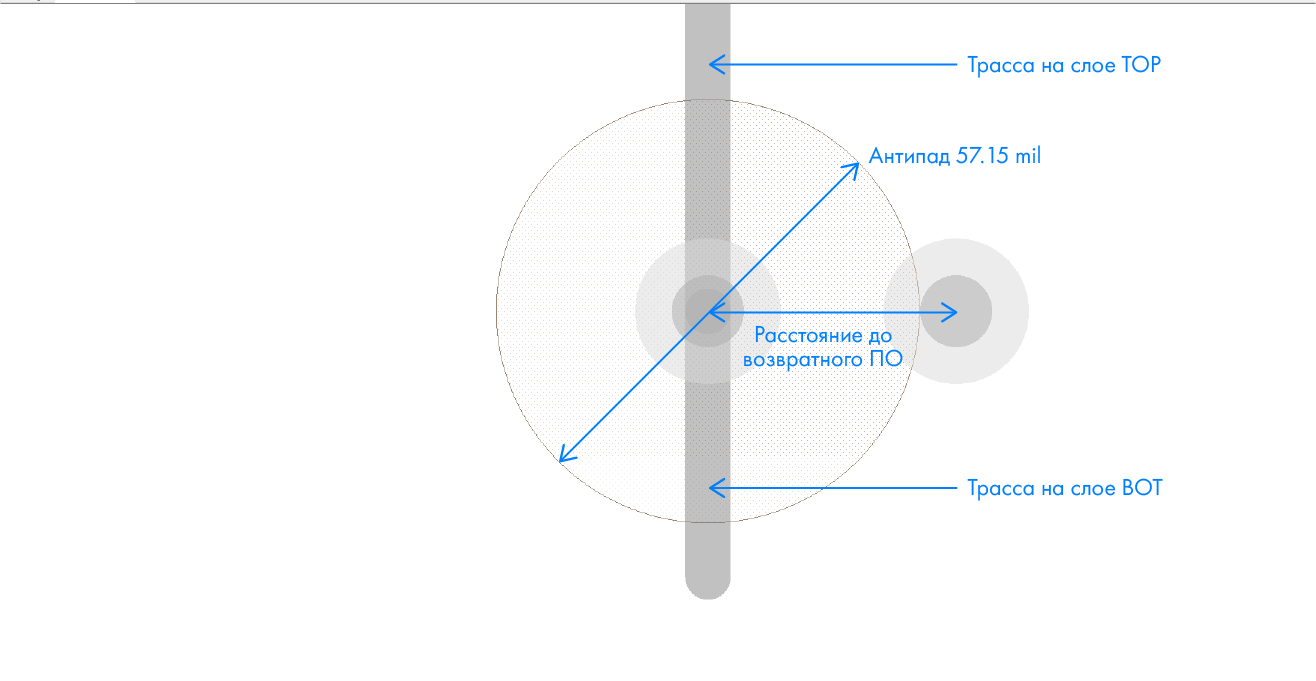

Для защиты п/о от помех, если есть возможность, необходимо увеличивать антипад на полигонах питания. Правило 20H для п/о обеспечить трудно, да и излишне, обычно рекомендуется антипад диаметром около 2 мм (Рисунок 9).

Рисунок 9. Увеличенный антипад на слоях питания

Расчёт импеданса одиночных переходных отверстий

Основываясь на знаниях о влиянии элементов п/о на импеданс, мы можем спроектировать своё идеальное п/о. Отличным стартом будет расчёт импеданса в калькуляторе.

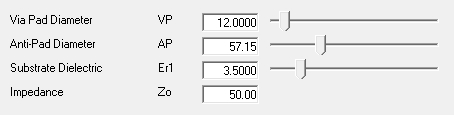

У инженеров, связанных с разработкой печатных плат, популярны такие калькуляторы как Saturn PCB Design Toolkit и Polar Instruments Si9000e. Оба они позволяют быстро рассчитать импеданс одиночного п/о.

Результат полученный в данных калькуляторах сильно отличается друг от друга. Это связано с тем, что у этих инструментов разный подход.

Polar cчитает импеданс в двухмерной плоскости, где п/о пересекает полигон питания. Формулы расчёта не приведено. Опытным путём было установлено, что расчёт производится по формуле импеданса коаксиального кабеля:

Рисунок 10. Изображение с сайта polarinstruments.com

На иллюстрации указано достаточно низкое значение диэлектрической проницаемости Er1, по сравнению со стандартным. Это связано с неоднородностью структуры диэлектрика: он состоит из смолы (Er 3.2) и нитей стекловолокна (Er 6.1), поэтому имеет среднюю диэлектрическую проницаемость около 4.1. Это значение может довольно сильно локально изменяться. Так, вблизи п/о преобладает смола, поэтому значение диэлектрической проницаемости пересчитано в сторону уменьшения [7].

Saturn PCB считает импеданс по формуле:

При изменении длины п/о, значения индуктивности и ёмкости изменяются непропорционально, импеданс изменяется. Импеданс точно такого же п/о длинной 1.6 мм, Saturn PCB рассчитывает, как 128 Ом! (Рисунок 11)

Рисунок 11. Расчёт п/о в программе Saturn PCB Design Toolkit.

Сразу возникает вопрос: кому верить?

Промоделируем в трёхмерном решателе электромагнитных полей (англ 3D Solver), как это будет выглядеть на реальной 8-слойной плате толщиной 1.6 мм (Рисунок 12)

Рисунок 12. Структура перехода между слоями с отверстием для возвратного тока.

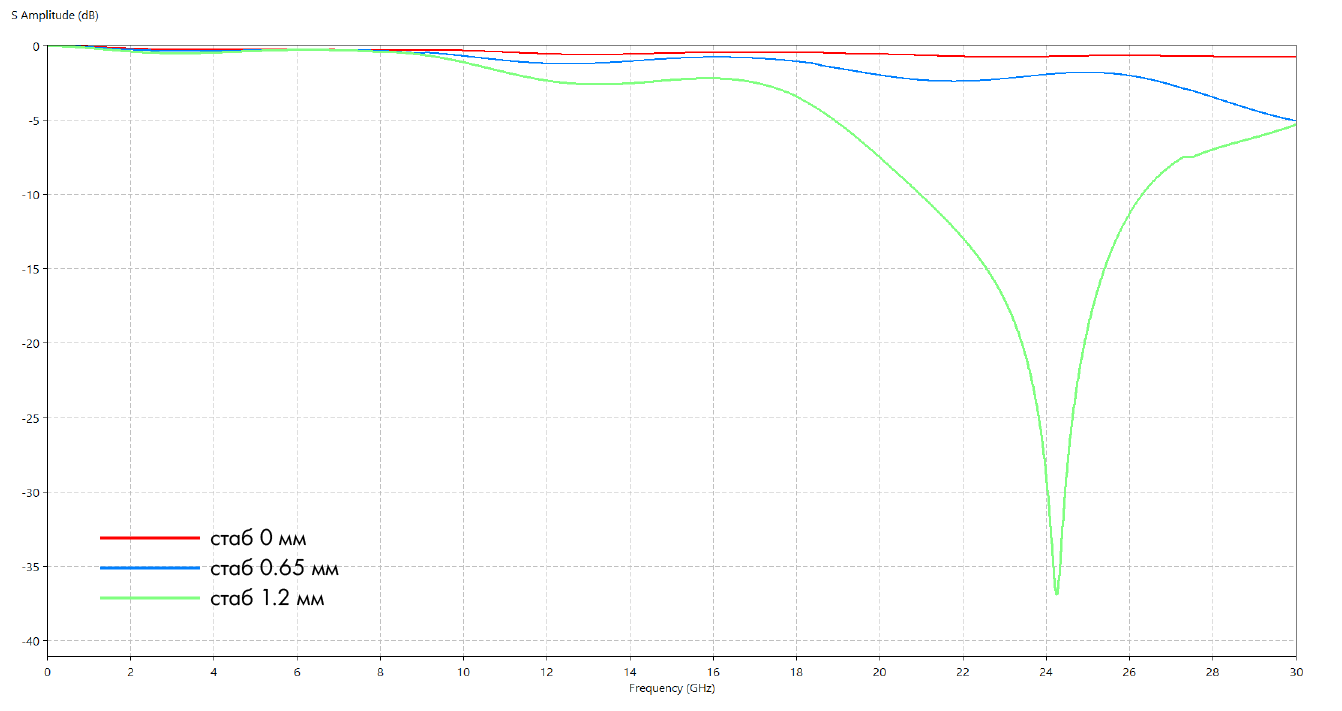

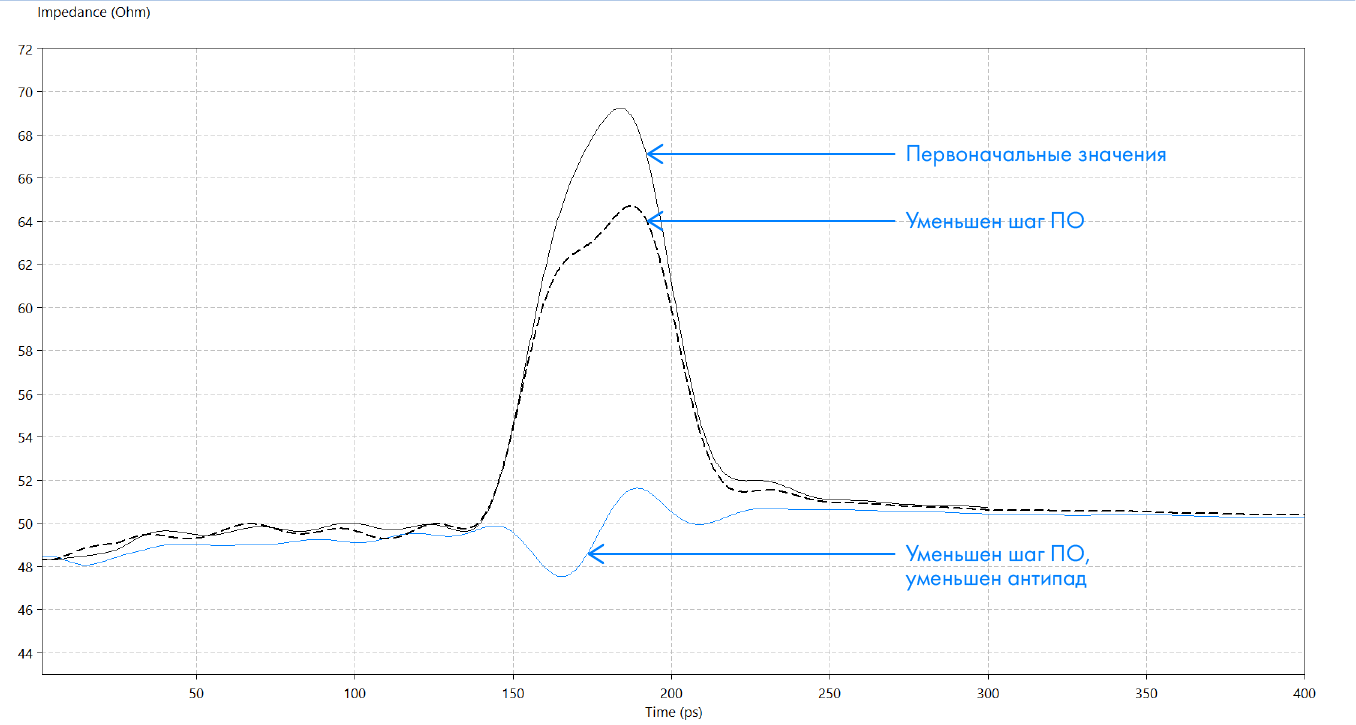

В нашем случае импеданс получился около 70 Ом. Приблизив возвратное п/о, можно добиться снижения ещё на 5 Ом. «Поиграв» с размером антипада, можно довольно точно подогнать импеданс к целевому значению (Рисунок 13).

Рисунок 13. Импеданс цепи с п/о на временной диаграмме.

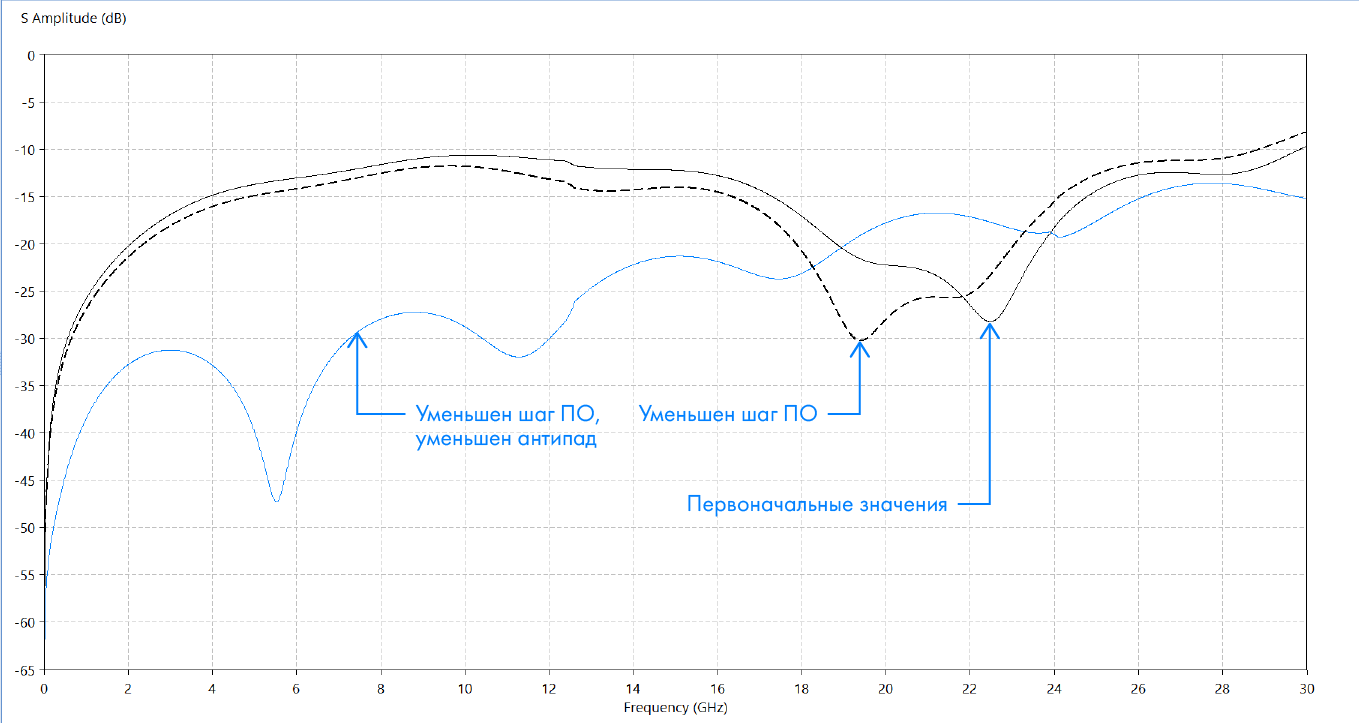

В частотной области «лучшие» параметры выражаются в меньшем значении коэффициента отражения от входа (Рисунок 14).

Рисунок 14. Параметры одиночных п/о в частотной области.

Расчёт Polar оказался ближе к полученному результату. Возможно, для получения адекватного результат в Saturn PCB, требуется ввести поправки. Если у кого-то есть положительный опыт расчёта импеданса в Saturn, поделитесь в комментариях!

Расчёт импеданса дифференциальных переходных отверстий

Расчёт дифференциальных п/о аналогичен одиночным, за исключением того, что теперь у нас нет калькулятора: указанные выше инструменты не считают дифференциальные п/о. Также, теперь мы можем дополнительно изменять шаг п/о в диф. паре.

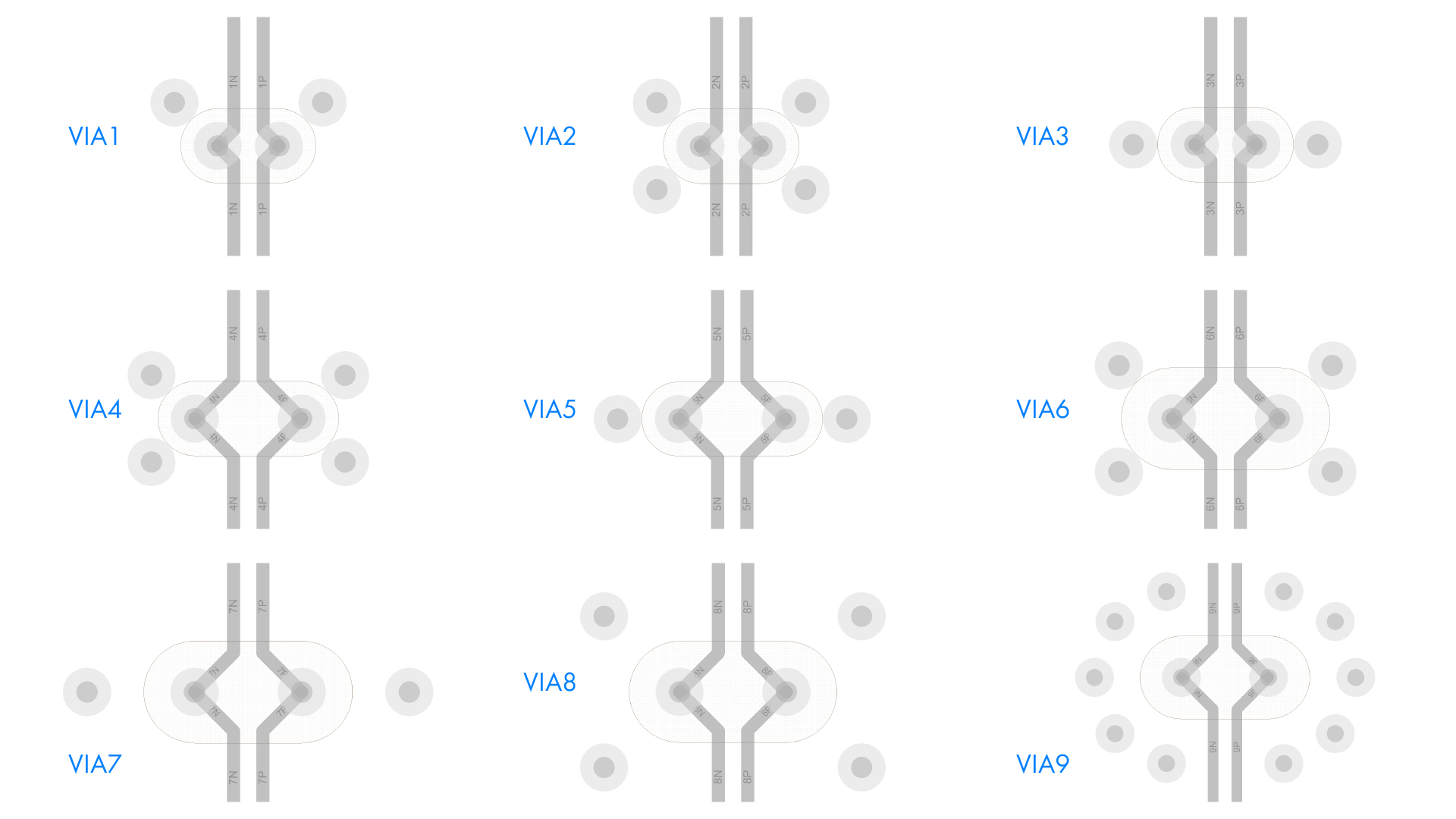

Структуру возьмём ту же: 8-слойную плату толщиной 1.6 мм. Рассмотрим 9 конфигураций п/о (Рисунок 15).

Первые 3 п/о имеют зазоры 0.125 мм и отличаются лишь расположением отверстий для возвратного тока. Все п/о с 4 и далее имеют шаг 1 мм. П/о с 6 и далее имеют увеличенный антипад (0.250 мм) и отличаются отступом отверстий для возвратного тока.

Рисунок 15. Переходные отверстия.

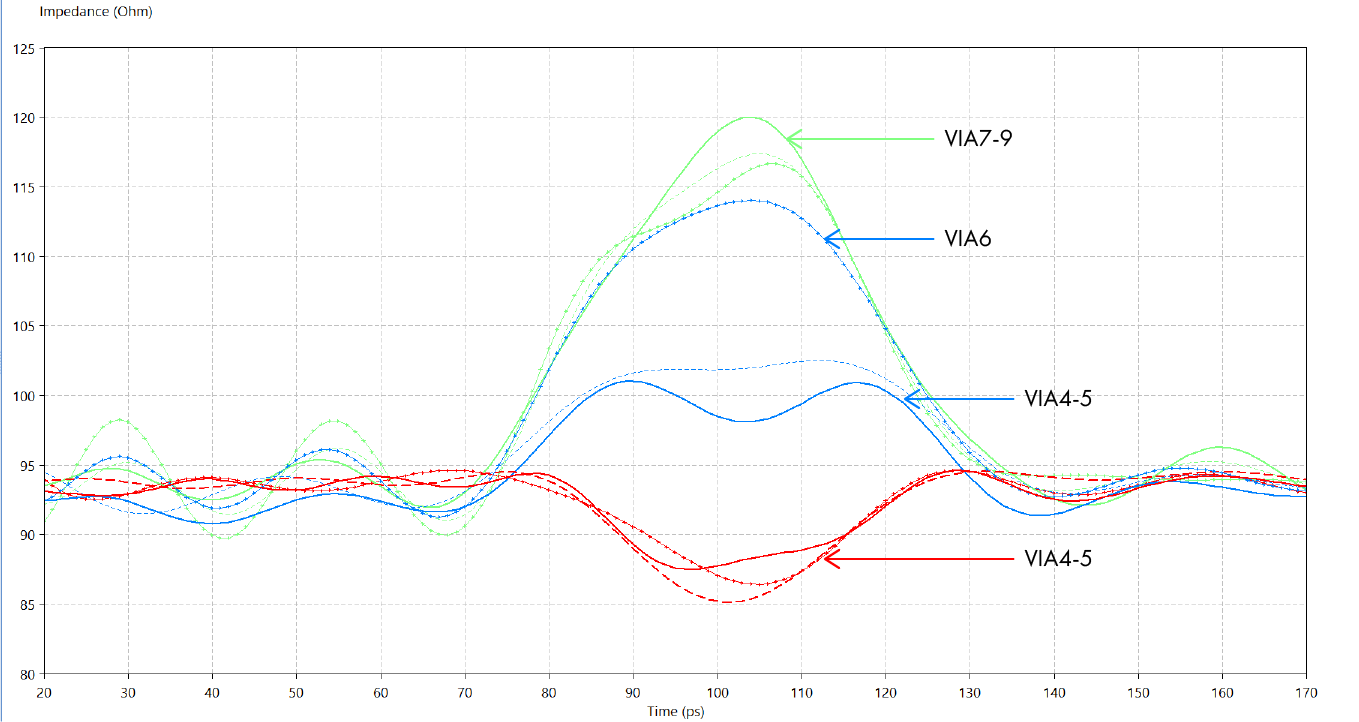

Рассмотрим график импеданса (Рисунок 16).

Рисунок 16. Импеданс п/о во временной области.

На графике хорошо виден «горб», который соответствует вертикальному отрезку п/о — «стакану» (англ. Via barrel).

Рассмотрев частотную зависимость коэффициента отражения VIA1-3 (Рисунок 17), видим, что несмотря на хорошие показатели на целевой частоте 6 ГГц, имеется резонанс на более низких частотах. Предпочтительней улучшить via7-9, а если не получится, то via4-5, чтобы уменьшить «горб» за счёт сдвига графиков вправо.

Рисунок 17. Коэффициент отражения от входа п/о.

Уменьшим антипад у VIA9, чтобы получить зазоры 0.125 мм. Для VIA4 уменьшим шаг п/о до 0.75 мм и рассмотрим полученный результат (Рисунок 18).

Рисунок 18. Сравнение импеданса модифицированных п/о.

В частотной области виден сдвиг графика коэффициента отражения от входа вправо (Рисунок 19).

Рисунок 19. Сравнение коэффициента отражения модифицированных п/о.

Заключительные рекомендации

Переходные отверстия в печатных платах — это сложная и неоднородная структура. Для корректного расчёта параметров необходимы дорогие 3D решатели, компетенции и значительные затраты времени.

Если нет возможности избежать использования переходов критических сигналов на другие слои, необходимо прежде всего оценить степень влияния возникших неоднородностей на целостность сигналов. Если неоднородность электрически короткая (время задержки менее 1/ 6 фронта), стаб резонирует на частотах, находящихся за пределами полосы пропускания — нет смысла тратить время и деньги на оптимизацию.

В первом приближении удобно использовать готовые структуры из даташитов или предыдущих плат, но помнить об особенностях текущего проекта.

Калькуляторы позволяют быстро оценить параметры п/о, однако используют сильно упрощённые модели, негативно влияющие на результат.

- Chin, T. Differential pairs: four things you need to know about vias. Retrieved from TI E2E Community: https://e2e.ti.com/blogs_/b/analogwire/archive/2015/06/10/differential-pairs-four-things-you-need-to-know-about-vias#

- Simonovich, B. Via Stubs Demystified. Retrieved from Bert Simonovich's Design Notes: https://blog.lamsimenterprises.com/2017/03/08/via-stubs-demystified/

- Demystifying Vias in High-Speed PCB Design. Retrieved from Keysight Technology: https://www.keysight.com

- K. Aihara, J. Buan, A. Nagao, T. Takada and C.C. Huang, “Minimizing differential crosstalk of vias for high-speed data transmission,” in Proc. 14th Elect. Perform. Electron. Packages and Systems, Portland, OR, Oct. 2014.

- C.M. Nieh and J. Park, “Far-end Crosstalk Cancellation using Via Stub for DDR4 Memory Channel,” in Proc. 63rd Electronics Components and Technology Conference, Las Vegas, NV, May 2013, pp. 2035-2040.

- H. Kanno, H. Ogura and K. Takahashi, “Surface-mountable Liquid Crystal Polymer Package with Vertical Via Transition Compensating Wire Inductance up to V-band,” in IEEE MTT-S Int. Microwave Symp. Dig., Philadelphia, PA, June 2003, pp. 1159-1162.

- Via Pad / Anti-Pad Impedance Calculation. Retrieved from Polar instruments https://www.polarinstruments.com/support/si/AP8178.html

Комментарии (49)

MaxxONE

20.06.2019 08:24А как понимать импеданс во временной области?

bazooka_easter

20.06.2019 10:14При этом довольно странно выглядит обозначенная во временном диапазоне область изменения импеданса. Вероятно, имеется ввиду переход от параметра отражения S11 ко входному сопротивлению с последующей трансформацией из частотной области во временную.

DenisHW

20.06.2019 10:53Возможно, имеется ввиду время распространия вдоль линии. То есть эквивалентно зависимости импеданса от расстояния вдоль линии.

asmolenskiy

20.06.2019 11:26TDR. Согласен, что формулировка не совсем корректна. Но имеется в виду именно TDR.

DenisHW

20.06.2019 12:01Возьмем рисунок 1. Он подписан «Изменение волнового сопротивления при переходе на другой слой». Но в реальности получается это то, что мы видим на входе линии при отражении от переходного отверстия? То есть графики от времени — это входное сопротивление линии, то есть отношение напряжения на входе к входному току от времени?

Chopr39 Автор

20.06.2019 12:22Спасибо за ответы!

Результаты были получены с помощью численного моделирования в частотной области. Затем значения коэффициента отражения S11 были пересчитаны во временную область c помощью обратного преобразования Фурье.

KonstantinSpb

20.06.2019 08:58+1Крайне интересная презентация от профессионала

www.altium.com/live-conference/altiumlive-2018-annual-pcb-design-summit#The-Extreme-importance-of-PC-Board-Stack-up

Очень классная книжка по «черной» магии сигналов на платах

High Speed Signal Propagation Advanced Black Magic

Ostrovv

20.06.2019 11:53«необходимы дорогие 3D решатели, компетенции и значительные затраты времени» не стоит путать академические задачи, и инженерное конструирование реального устройства, а то после статьи впечатление что прикоснулся к высшей магии, в реальности все намного проще

asmolenskiy

20.06.2019 12:19+2в реальности все намного проще

Пока Вы не ушли за 10GHz. Или пока не начали пилить структуру, в которой PCI Gen4 проходит через полуметровый бэкплейн и несколько коннекторов. Тут Вы уже и моделируете, и стеклотекстолит выбираете с правильным плетением, и на шероховатость смотрите и IBIS-AMI модели прикручивате и как верно написал автор — Вам нужен дорогой софт, специалист по SI и время.

В ситуациях когда Вам надо выйти из чипа и запрыгнуть в оптику — да, все намного проще. Хотя пару лет назад на 25G я на модели получил экстремум S11 в переходном отверстии прямо в Найквисте. А канал был FPGA — QSFP на расстоянии сантиметров 5. То есть в реальной жизни оно бы скорее всего не работало.

nkie

20.06.2019 16:41небольшой офтоп: какая частота подразумевается по частотой Найквиста например для PCIe 3.0 8.0 GT/s? Спасибо.

asmolenskiy

20.06.2019 16:43Когда говорят Найквист применительно к HS-шинам — имеют в виду частоту паттерна 1010101… То бишь для 8GT/s — это 4ГГц.

Хотя лично меня такое использование термина «частота Найквиста» несколько коробит. Но все привыкли уже.

nkie

20.06.2019 16:52А что подразумевается в иностранной литературе под понятием Nyquist rate? Насколько удалось понять это не то же самое что частота Найквиста. И Nyquist rate = 2*Baudrate. Т.е. для тех же 8GT/s Nyquist rate = 16GHz?

asmolenskiy

20.06.2019 16:53Ну классически Частота Найквиста — это половина от частоты с которой надо нарезать сигнал, чтобы восстановить его без искажений. Это единственное правильное и годное определение.

Когда говорят в контексте SI Найквистом обзывают частоту, для которой надо обеспечить Loss Budget. Обычно это половина от GT/s.

Учитывая что фронт PCIe по спецефикации 30пс — его полоса 16.7ГГц. Трушный Найквист. Но это не связано с Baud Rate — просто совпало.

Chopr39 Автор

20.06.2019 12:27В начале статьи, я упоминал, что в реальности обычно всё намного проще: посмотрел рефдизайн/почитал гайдлайны — повторил. Не заработало — выпустил новую ревизию…

maxbrsw

20.06.2019 14:42+1Хорошая статья, разрешите пару комментариев:

— самый быстрый и простой способ на данный момент решать такие задачи, это все же Keysight ADS:) Безусловно, мое мнение сильно предвзято(очень нравится этот софт), но связка VIA Designer + CILD + SIPRO + сам схематик конечно позволяет очень легко и удобно решать задачу комплексно, на уровне всего линка, с feasibility study и what if экспериментами.

— Помимо этого, отдельно стоит отметить Simbeor, а с ним же и Юрия Шлепнева, профессионала мирового уровня и имеющего канал на Youtube с отличным контентом по данной тематике.

— backdrilling важен не только в плане удаления subs, но и в том смысле что не для любого стекапа можно сделать differential via structure сквозь всю плату так, чтобы не получить «горы» на TDR.

— не последнюю роль играет и подвод сегментов пары в области антипада, он может быть в т.ч. полигональным. Причины подобных изысканий в конечном счете все так же сводятся к борьбе L vs C, и удержании их значений в рамках разумных компромиссов.

— совершенно отдельная тема, mode conversion в случае использования таких структур, просто поставить антипад и земляные переходные «где-то там»(как часто бывает) может оказаться не только недостаточно, но и опасно.

Польза от применения антипада не только в том, чтобы сделать адекватными S параметры перехода- тот же Юрий использует очень хорошее определение, localized structures, крайне рекомендую посмотреть соответствующие ролики на его канале.

Chopr39 Автор

20.06.2019 16:12Всё правильно пишете.

— самый быстрый и простой способ на данный момент решать такие задачи, это все же Keysight ADS:) Безусловно, мое мнение сильно предвзято(очень нравится этот софт), но связка VIA Designer + CILD + SIPRO + сам схематик конечно позволяет очень легко и удобно решать задачу комплексно, на уровне всего линка, с feasibility study и what if экспериментами.

Работаем с тем, что есть. Я как конструктор больше по трассировке, а при всех недостатках Sigrity, она хорошо интегрируется с редактором печатных плат. ADS не использовал, но какую статью не откроешь, всё сделано там. Это показатель.

— backdrilling важен не только в плане удаления subs, но и в том смысле что не для любого стекапа можно сделать differential via structure сквозь всю плату так, чтобы не получить «горы» на TDR.

Такого не встречал, но звучит логично, почему бы высверливанием не уменьшить индуктивность, если есть необходимость?

— не последнюю роль играет и подвод сегментов пары в области антипада, он может быть в т.ч. полигональным. Причины подобных изысканий в конечном счете все так же сводятся к борьбе L vs C, и удержании их значений в рамках разумных компромиссов.

В этой работе на завершающей стадии «тюнинга» я тоже поигрался с параметрами сегментов в области антипада. В моём случае, картина сильно не изменилась, поэтому решил не включать в статью.

DenisHW

20.06.2019 16:19при всех недостатках Sigrity, она хорошо интегрируется с редактором печатных плат

То есть все моделирование из вашей статьи сделано в Sigrity от Cadence?

Chopr39 Автор

20.06.2019 16:28Да. Power SI + Broadband SPICE

DenisHW

20.06.2019 16:43А это не то, что встроенно в Allegro, Sig Xplorer? Если нет, то не пробовали ли сравнивать результаты Sig Xplorer и powerSI?

Chopr39 Автор

20.06.2019 17:00В SigXplorer удобно задавать electrical constraints для сложных топологий. Для моделирования via не подходит, потому что не умеет в 3D.

maxbrsw

20.06.2019 16:25Работаем с тем, что есть. Я как конструктор больше по трассировке, а при всех недостатках Sigrity, она хорошо интегрируется с редактором печатных плат. ADS не использовал, но какую статью не откроешь, всё сделано там. Это показатель.

Одна из причин этому, помимо совершенно адекватного интерфейса и workflow как такового, это именно удобство и для PCB Designer-а, и для SI Engineer-а: скажем, на схеме легко можно сочетать как equation-based модели, так и реальные куски layout с платы- с учетом широких возможностей параметризации легко выработать шаблоны, которые покрывают вообще все задачи под конкретное направление. Тем более нет нужды в «готовой» плате, начинать можно с любого конца.

В этой работе на завершающей стадии «тюнинга» я тоже поигрался с параметрами сегментов в области антипада. В моём случае, картина сильно не изменилась, поэтому решил не включать в статью.

Оно себя, как правило, проявляет на очень серьезных скоростях, от 56G и далее- естественно не на всех стекапах.

asmolenskiy

20.06.2019 16:15— backdrilling важен не только в плане удаления subs, но и в том смысле что не для любого стекапа можно сделать differential via structure сквозь всю плату так, чтобы не получить «горы» на TDR.

Максим, висящий хвост работает как паразитная емкость. Бакдрил сдвигает баланс в сторону индуктивности.

Стаб превращает глаз в звезду, так как первое что видит сигнал, когда видит хвост — это провал импеданса.

maxbrsw

20.06.2019 16:28Антон, я в курсе:) просто хочу сказать что есть стекапы, в которых просто добавление антипада не решит проблему целиком, нужен еще и бэкдрил: условно говоря, емкость еще не убрали, а индуктивность уже дает о себе знать.

Chopr39 Автор

20.06.2019 16:35висящий хвост работает как паразитная емкость

Ты имеешь ввиду ёмкость между двумя стабами в diff via?

asmolenskiy

20.06.2019 16:36Нет. Это емкость между висящим стаканом и полигонами питания.

Стаб работает как если бы ты конденсатор в землю на линию повесил.

У него конечно есть какая-то индуктивность, но в данном включении она на тебя не влияет.

maxbrsw

20.06.2019 16:46Это емкость между висящим стаканом и полигонами питания.

Именно- есть скажем плата от 40 слоев, и нужно вести сигнал глубоко: антипадом конечно вырежешь емкость до плейнов питания/земли, но он будет немалым(больше слоев=больше резать), и тут как раз встанет момент с индуктивным участком в области подвода трассы к виа. Есть конечно случаи когда это полезно, и притом на гораздо более приземленных скоростях(тот же L-comp), но тут как раз нужно избавиться «от всего», что может оказаться непомерно сложной задачей при некоторых вводных.

Стаб работает как если бы ты конденсатор в землю на линию повесил.

Neglecting transmission line losses, the input impedance of the stub is purely reactive; either capacitive or inductive, depending on the electrical length of the stub, and on whether it is open or short circuit. Stubs may thus function as capacitors, inductors and resonant circuits at radio frequencies.

Ну и тем более, есть все-таки техники( в том числе топорные весьма) терминирования стабов, но тут речь чуть о другом.

pi_11_001001

20.06.2019 18:09+2отлично, однако забыты каплевидные сочленения контактных площадок и проводников

Chopr39 Автор

20.06.2019 19:14Эти сочленения, Teardrops, замечательны для DFM, они повышают надёжность платы, выход годных. Однако для целостности сигналов это скорее зло, особенно если вы долго «тюнинговали» свои переходки, а производитель без согласования добавил их на плату, тем самым увеличив ёмкость.

Dominikanez

20.06.2019 18:09Сорри за небольшой оффтоп, но может кто из здешних гуру подскажет: какими правилами регламентируется (и регламентируется ли вообще, может такого и нет) наличие на многослойной плате окон в верхних слоях текстолита? Скажем, если МПП состоит из трёх препрегов, то могу ли я без особых усилий договориться с технологом производства о том, что мне надо в верхнем слое текстолита сделать окошко, чтобы в дальнейшем в нем «спрятать» компонент, скажем, чип-резистор SMD 0402? Припаян такой резистор, конечно, будет к своим падам, но на внутреннем слое, а не как обычно, на верхнем.

asmolenskiy

20.06.2019 18:17У нас есть одна плата с окнами — но там фрезой просто их вырезают на контролируемую глубину. У фрезы есть допуск и с точностью до поверхности пэдов ей не выпилить.

Думается мне, хотя я не уверен — у меня нет такого опыта, что закопанные компоненты делают путем спрессовки двух отдельно изготовленных плат.

HiTechSpoon

20.06.2019 18:32Так вы спросите производителя. Начертите то, что вы хотите получить, да и передайте им. Как пример, Резонит всегда очень хорошо общается, причем связь можно получить напрямую с инженером-технологом и обсудить любую дичь. Не знаю, правда, не попадает ли это под определение «особые усилия».

Dominikanez

20.06.2019 18:34Я начертил подобное паре крупных российских производителей — мне даже не ответили. Пару попыток связаться по телефону потом предпринял и понял, что им сложно это всё и воспринимать и готовить и производить. Потому до сих пор озадачен прологом всей этой истории.

HiTechSpoon

21.06.2019 13:21Возможно, если вы писали от физического лица, стоит попробовать написать от организации, которая является постоянным клиентом производителя. Видимо этот фактор может играть роль. Если хотите, я могу вам с этим помочь, особенно, если проект научный или опенсорсный, напишите мне личное сообщение и мы обо всем договоримся.

Есть еще вариант — запостить вопрос на форуме www.rezonit.ru/forum.

QwertyOFF

20.06.2019 19:39Попробуйте спросить в Электроконнекте (Новосибирск, учитывайте, когда звоните). Помимо этого видел в рекламе какого-то контрактного производства возможность делать компоненты внутри платы, но это, я подозреваю, за очень неприятную цену.

Chopr39 Автор

20.06.2019 20:05У вас спортивный интерес или какие-то узкоспециализированные потребности? Сходу даже сложно представить кейс, где бы это могло понадобиться.

Регламентируется это всё стандартом IPC-7092 Design and Assembly Process Implementation for Embedded Components.

LampTester

21.06.2019 12:21Хорошая статья, спасибо!

Для себя понял, что, по всей видимости, где-то до 5 ГГц можно особенно не заморачиваться.

В принципе, самое скоростное, что есть в моей практике — это трансиверы на 2.4 ГГц. Как-то так сложилось, что я больше занимаюсь низкопотребляющими решениями.

asmolenskiy

21.06.2019 12:24где-то до 5 ГГц

Зависит от длины канала и его топологии. Убить можно и гигабит.

Я даже по молодости I2C убивал по SI.

LampTester

21.06.2019 12:48Ооо, хехе, вот у нас на работе как раз любимое развлечение — протаскивать SPI, IIC, UART и похожее через кабели длиной метров пять. :) При этом конвертеры в какой-нибудь RS-485 в силу специфики не поставить.

А что до гигагерц, то, как я говорил, для меня это трансиверы. Топология там простая — трансивер, симметрирующий узел (aka balun) и дальше SMA-разьем, все. :)

asmolenskiy

21.06.2019 12:50Ооо, хехе, вот у нас на работе как раз любимое развлечение — протаскивать SPI, IIC, UART и похожее через кабели длиной метров пять. :) При этом конвертеры в какой-нибудь RS-485 в силу специфики не поставить.

У меня просто была очень длинная I2C по всему устройству из нескольких плат, которая в какой-то момент еще и звездой разошлась в все стороны на достаточно большие расстояния.

Так я в первый раз узнал что такое отражения и стоячая волна.

GAYVER

21.06.2019 16:20материал из смежной области. прочитал с удовольствием — для общего развития самое то

a_freeman

Спасибо! Пишите еще, такие статьи находят своих читателей.

По среде моделирования статьи / материалы публиковать будете?

Или что можете порекомендовать? :)

asmolenskiy

Сегодня стандартом считается связка HFSS и Keysight ADS.

Мы используем Sigrity. Но это не то, что я бы стал рекомендовать. Этому инструменту (как и всем остальным, которые Cadence купил и интегрировал в себя) не хватает целостности и дружелюбности к пользователю.

Chopr39 Автор

Спасибо за интерес к статье! Если вас интересует моделирование в среде Allegro/Sigrity, хорошие материалы есть у PCB Soft, на сайте и YouTube канале.