Через неделю будет выставка ChipEXPO, на которой для будет школа проектирования железа для начинающих с упражнениями на FPGA платах, а для более продвинутых - конференция Микроархитектура, верификация и физическое проектирование микросхем.

И на секции для школьников, и на секции для взрослых будут выступать проектировщики RISC-V процессора из Syntacore / Yadro Станислав Жельнио и Никита Поляков. Сегодня Коммерсантъ сравнил этот проект с полетом на Луну.

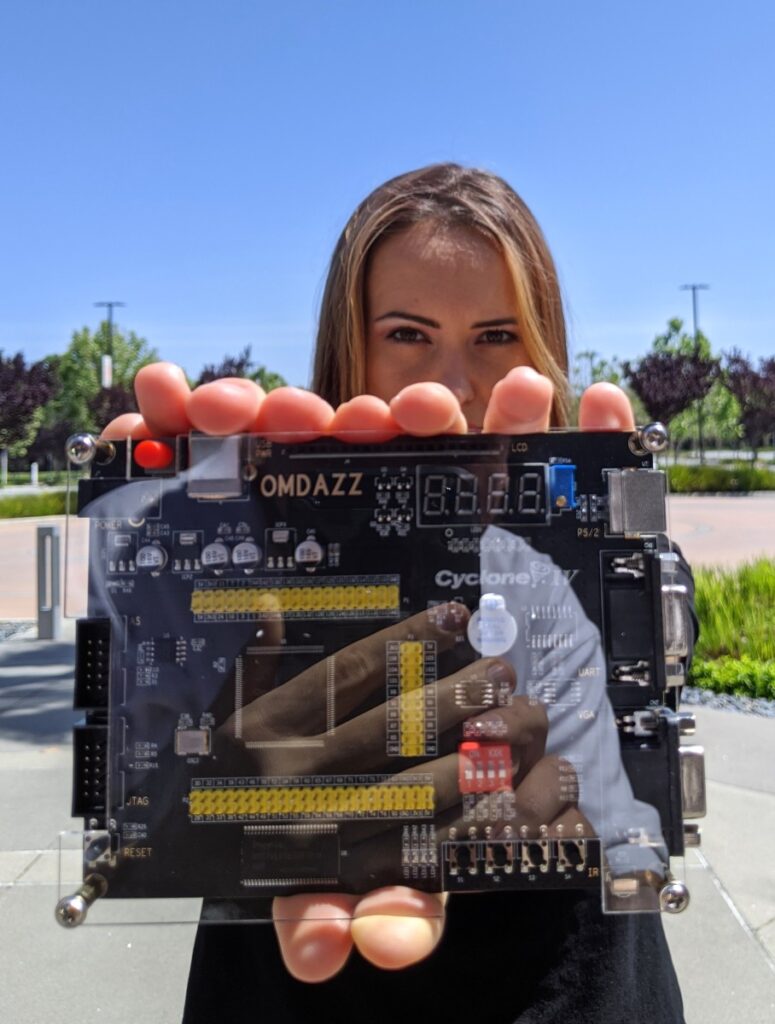

Количество заявок на школу существенно превысило количество посадочных мест, но у нас еще остался небольшой резерв FPGA плат, с бесплатной их раздачей школьникам и преподавателям из далеких от Москвы городов, которые могут принять участие в школе онлайн. В начале этой заметке мы опишем как получить плату и установить софтвер, нужный для упражнений.

Далее мы расскажем про новые упражнения в школе этого года - распознавание и генерацию музыки с помощью FPGA и приведем забавные сведения из советской физматшкольной книжки 1963 года как Бах изменил гаммы.

В конце поста мы покажем, как эта деятельность поможет получить в будущем интересные и высокооплачиваемые работы в Apple, Intel, SpaceX, как и самом в модном в этом сезоне российском микроэлектронном проекте - Syntacore / Yadro (в конце поста скриншоты их объявлений).

Прежде всего, так как количество заявок вдвое (а сейчас уже может и втрое) превысило количество мест офлайн, мы решили отдавать приоритет на посадочные места для тех, кто прошел три небольших онлайн-курса от Роснано «От транзистора до микросхемы», «Логическая сторона цифровой схемотехники» и «Физическая сторона цифровой схемотехники».

Этот курс гарантирует, что человек, который садится за стол с FPGA платой, по крайней мере не впервые в жизни слышит слова D-триггер и неблокирующее присваивание. Без этого человек будет переносить на код на языке описания аппаратуры Verilog свои ассоциации с программированием, и происходящее на плате будет казаться бредом. Также без курса может быть непонятно как упражнения с лампочками и кнопочками приводит к позиции проектирощика на уровне регистровых передач (Register Transfer Level (RTL) Desigfn Engineer) в тоp-20 электронных компаниях или в купленном Ядром стартапе Syntacore, который теоретически может превратить Россию в великую электронную державу лет через 10-20, аккурат к творческим вершинам карьеры современных школьников.

Прохождение этого курса также нужно, если вы не можете приехать в Сколково, но вы хотели бы получить плату, чтобы практиковаться удаленно. Эта опция доступна школьникам и преподавателям школ, вузов и кружков. Помимо платы вы получите микрофон и усилитель для упражнений со звуком. Вам нужно показать серфитикат после прохождения роснановского онлайн-курса и договориться с Михаилом Коробковым (Команда проекта FPGA-Systems.ru, fpga-systems@yandex.ru) чтобы он выслал вам плату.

Если у вас нет платы, вы не школьник и просто хотите посмотреть, вы можете присоединиться к занятиям Школы через интернет, на онлайн платформе eventwallet, на которую будут вестить прямые трансляции всех лекций и практических занятий Школы. Для этого нужно зайти на платформу, зарегистрироваться и перейти на вкладку ПРОГРАММА в левом меню. Там увидите виртуальный конференц-зал, в котором будет идти трансляция.Можно задавать вопросы спикерам в режиме чата.

Деньги на платы, перевод и трансляцию мероприятия дали: Cadence Design Systems, Siemens EDA / МЕГРАТЕК (Megratec - Mentor Graphics Technologies), Наносемантика, Alchemical Music Box, Максим Маслов (сооснователь Eltechs и автор шумящего сейчас поста "Легенды и мифы процессора Эльбрус в примерах") и ваш покорный слуга Юрий Панчул.

Примеры которые используются в этой части семинара работают со всеми версиями Quartus начиная с 13.0sp1. Желательно конечно использовать последнюю из бесплатных (Lite) версий, но текущая бесплатная версия Quartus Prime Lite Edition 20.1.1 не работает сразу после скачивания ни на текущей версии Windows 10, ни на текущей версии Linux Ubuntu 20.04 LTS. Для Windows у нее истекла дата сертификата драйвера, а для Linux она использует устаревшую библиотеку.

Обе проблемы можно решить: для Windows - c помощью скачивания patch, а для Linux - с помощью "sudo ln -sf /lib/x86_64-linux-gnu/libudev.so.1 /lib/x86_64-linux-gnu/libudev.so.0".

Для проверки, что ваша FPGA плата и установка Quartus работает, вы можете скачать минимальный пакет "before" по следующей ссылке:

ChipEXPO 2021 Digital Design School before package v2.0 https://bit.ly/chipexpo2021ddsbefore20

Прямая ссылка

В качестве инструкций можно использовать видео Сергея Иванца с прошлого года, но применять их для нового пакета, а также использовать новые версии Quartus для Linux и Windows.

Теперь насчет упражнений по распознаванию и генерации звуков на верилоге с помощью FPGA платы. Сначала мы думали использовать синтетический звук из телефона, но потом решили, что это неспортивно - нужен живой звук, на котором можно тренировать техническую смекалку, требуемую для решения задач на распознавание.

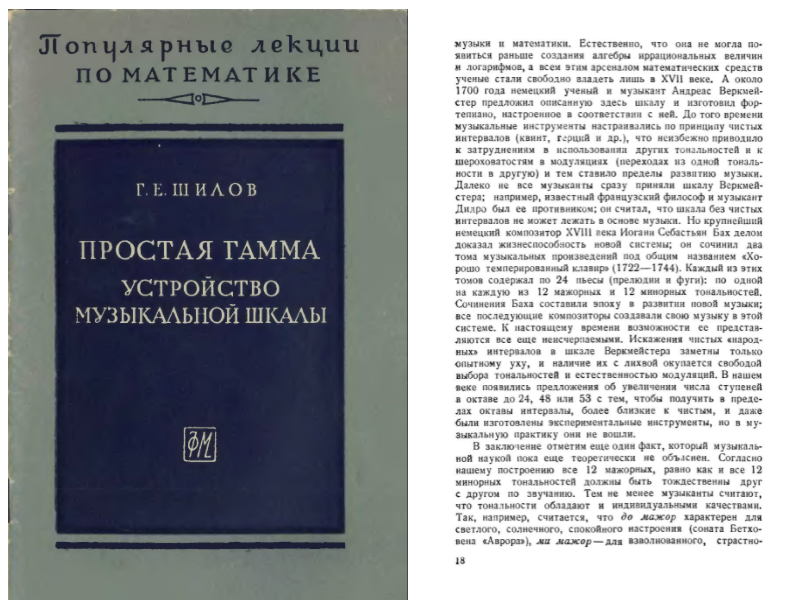

В процессе подготовки упражнений с музыкой на FPGA я узнал из советской книжки для детей 1963 года удивительный факт:

Оказывается, современные гаммы отличаются по частотам нот от гамм, которые были до Баха. В современных гаммах полутона находятся в геометрической прогрессии, на расстоянии корня 12-той степени из двойки друг от друга. А в 17 веке клавесины и арфы настраивали по другому, так, чтобы частоты образовывали кратные отношения (так называемый "чистый строй"). Из-за этого мелодии нельзя было транспонировать в другие тональности - они начинали звучать криво. Собственно именно Бах пропиарил новую систему в "Хорошо темперированном клавире" и доказал что с корнем 12-й степени из двойки сочинять можно. До этого эстеты лет 20 считали новую систему ("равномерно темперированный строй") немного варварской.

В упрямой России нововведение критиковали даже в 19 веке, согласно википедии: "Русский простолюдин с музыкальным дарованием, у которого ухо ещё не испорчено ни уличными шарманками, ни итальянскою оперою, поет весьма верно; и по собственному чутью берет интервал весьма отчетливо, разумеется, не в нашей уродливой темперированной гамме" Владимир Одоевский

Более реально чем теплый ламповый звук между прочим!

Каким образом FPGA плата может распознать какую-нюбудь простую мелодию, например из фильма "Крестный отец" (эта мелодия также звучит в советском мультфильме "Контакт")?

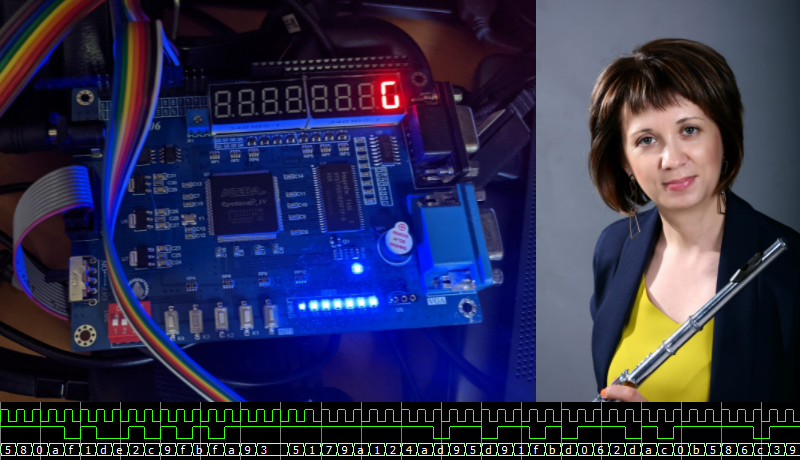

Если звук достаточно чистый, то можно распознать и без Фурье-преобразования, просто подсчетом тактов (но не музыкальных, а тактового сигнала 50 MHz на FPGA плате) между моментами, когда синусоида уровня сигнала пересекает его среднее значение. Этот метод называется zero crossing, и он вполне работает для звуков флейты. Флейту принесет преподавательница Мария Беличенко . Вот как zero-crossing выглядит на языке описания аппаратуры Verilog:

https://github.com/DigitalDesignSchool/ce2020labs/blob/master/day_2/piswords/lab_5_mic/top.v

reg [15:0] prev_value;

reg [19:0] counter;

reg [19:0] distance;

localparam [15:0] threshold = 16'h1000;

always @ (posedge clk or posedge reset)

if (reset)

begin

prev_value <= 16'h0;

counter <= 20'h0;

distance <= 20'h0;

end

else

begin

prev_value <= value;

if ( value > threshold

& prev_value < threshold)

begin

distance <= counter;

counter <= 20'h0;

end

else if (counter != ~ 20'h0) // To prevent overflow

begin

counter <= counter + 20'h1;

end

end

// Теперь в distance у нас лежит период нижней гармоники ноты

// выраженный в тактах 50-мегагерцового тактового сигнала

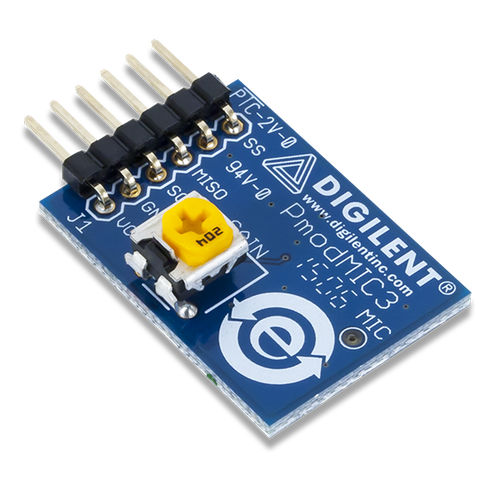

Уровень звукового сигнала снимается вот таким микрофоном, который мы выдадим:

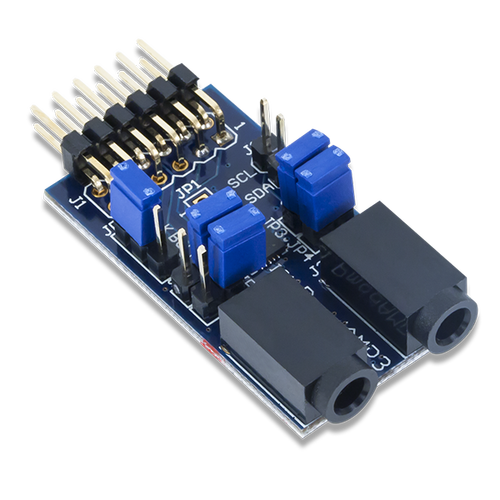

Также с помощью вот такого усилителя можно сгенерировать звук. Если все хорошо отладить, то после распознавания мелодии ее можно продолжить из усилителя:

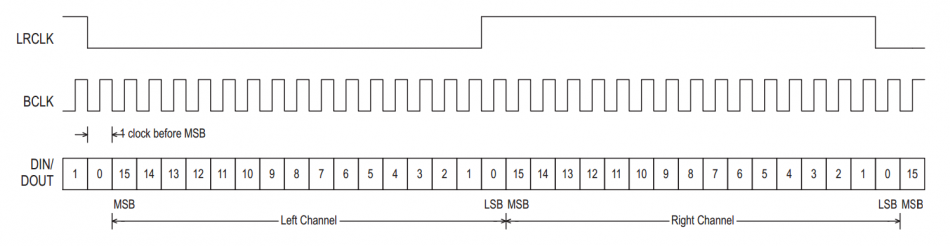

Микрофон передает уровень сигнала в FPGA с помощью протокола SPI, а усилитель использует протокол I2S.

Оба протокола реализуются простым сдвиговым регистром, см. код для I2S Виктора Прутьянова:

module i2s

(

input clk, // CLK - 50 MHz

input reset,

input [2:0] octave,

input [3:0] note,

output mclk, // MCLK - 12.5 MHz

output bclk, // BCLK - 3.125 MHz serial clock - for a 48 KHz Sample Rate

output lrclk, // LRCLK - 32-bit L, 32-bit R

output sdata

);

reg [9:0] clk_div;

reg [31:0] shift;

reg [7:0] cnt;

wire [15:0] value;

wire [7:0] cnt_max;

always @ (posedge clk or posedge reset)

if (reset)

clk_div <= 0;

else

clk_div <= clk_div + 10'b1;

assign mclk = clk_div [1];

assign bclk = clk_div [3];

assign lrclk = clk_div [9];

always @ (posedge clk or posedge reset)

if (reset)

cnt <= 0;

else if (clk_div [9:0] == 10'b11_1111_1111)

cnt <= (cnt == cnt_max) ? 8'b0 : cnt + 8'b1;

assign sdata = shift [31];

always @ (posedge clk or posedge reset)

if (reset)

shift <= 0;

else

begin

if (clk_div [8:0] == 9'b1_1111_1111)

shift <= value << 16;

else if (clk_div [3:0] == 4'b1111)

shift <= shift << 1;

end

lut lut

(

.octave ( octave ),

.note ( note ),

.x ( cnt ),

.x_max ( cnt_max ),

.y ( value )

);

endmoduleДля усилителя вам нужны будут наушники, а если хотите генерировать стерео звуки, то вот такой кабель:

Может вы сможете повторить сцену из мультфильма Контакт с помощью FPGA платы:

Кроме лаб со звуком, лаб с процессором schoolRISCV еще будут лабы с VGA играми. Они были очень популярны на школе в Зеленограде:

Для этих упражнений вам понадобится дополнительный монитор с VGA входом, чтобы воткнуть его в FPGA плату. Этих мониторов у нас дефицит, так как в Сколково будуь стоять только 25 моноблоков, которые нам организовал Евгений Певцов из МИРЭА. Если можете принести свой мониторчик, будет хорошо (если вы делаете упражнения удаленно, у вас наверняка есть старый монитор или вы можете одолжить).

Теперь зачем все это нужно. Упражнения с FPGA - это путь в проектирование на уровне регистровых передач. Он на уровне верилога и микроархитектуры более-менее общий и для FPGA и для ASIC - микросхем которые стоят в сматрфонах и других массовых устройствах. Причем работы в крутых компаниях есть и на FPGA, и для интернов. Это интересно и хорошо оплачивается. Причем и на школе для начинающих, и на школе для продолжающих (секции 2 и 3) у нас будут задачки по мотивам реальных вопросов на собеседованиях :-)

Комментарии (50)

asmolenskiy

07.09.2021 11:00+2Юрий, я смотрю, прислушался к совету ))))

YuriPanchul Автор

07.09.2021 11:22+4Что-то мало комментариев. Поменять заголовок на "Не только Силиконовая Долина: Проектировщики RISC-V из Yadro покажут школьникам как проектировать процессоры" ?

BrennendeHerz

07.09.2021 11:58+2Лучше так:

"Пока Билл Гейтс планирует заблокировать солнце, проектировщики RISC-V из Yadro покажут школьникам как проектировать процессоры"

Шутки шутками, но очень приятно знать, что изучение проектирования RISC-V востребовано среди учащихся школ. Это даже важнее, чем востребованность среди студентов ВУЗов. Именно в школе загораются идеи, куда свернуть на пути образования. В ВУЗе поменять направление уже сложнее. Вероятно кому-то это позволит сделать правильный выбор на следующие 5-6 лет жизни, а компании работающие "в долгую" получат не только репутацию, но и заинтересованных сотрудников.

erthink

07.09.2021 12:00+4Знакомить школьников с Verilog-ом и вариантами болден-RISC-а в целом на пользу, кто-то научится да пойдет делом заниматься (в МЦСТ).

Но (цитата) "Сегодня Коммерсантъ сравнил этот проект с полетом на Луну." - это уже перебор, ибо Луна была упомянута в негативной коннотации при оценке рисков связанных с боден-RISC-ом, и сделал это Константин Трушкин из МЦСТ, а не "Коммерсантъ".

Armmaster

07.09.2021 15:17+1Ага, как раз к тому времени у МЦСТ возникнет большой набор вакансий для специалистов, знакомых с RISC-V ))

YuriPanchul Автор

07.09.2021 17:20Что такое болден-RISC? Вообще на ChipEXPO по RISC-V будет много докладов - нетолько schoolRISCV, но и от Imagination, и от Redwood Design

tommy_lee

07.09.2021 12:15+3Verilog - самая привлекательная штука: пока твои сокурсники хвастаются крутыми сайтами и приложениями, ты можешь показать только результаты тестов и временные диаграммы. От отсутствия осязаемых результатов быстро выгораешь

asmolenskiy

07.09.2021 14:01+1Нет - на самом деле HDL-кодинг достаточно интересен и увлекателен. Я сам этим занимался 6 лет. Но это как бы - не профессия, а просто один из навыков.

Беда в том что не очень то в РФ за это платят. Ну то есть чипмейкеры-то платят, но на одного чипмейкера приходится пара десятков разработчиков FPGA в разных около-военных лавках.

Mox

07.09.2021 14:42Это определенный настрой ума. Кто-то думает в категориях продукта и решения задач пользователей, кто-то решает логические задачи и строит схемы по спецификации.

Это ближе к системному программированию или программированию движков БД.

YuriPanchul Автор

07.09.2021 17:28+2Да уж, я вот сейчас пишу верилог для после-после-следующего телефона Самсунг Галакси, пока он дойдет до миллиардов пользователей, прийдется немного повыгорать, пока бывшие однокурсники хвастаются своими домашними страничками на джаве.

tommy_lee

07.09.2021 22:43телефона Самсунг Галакси

О, они до сих пор не обанкротились?

YuriPanchul Автор

08.09.2021 01:48Самый большой производитель телефонов в мире?

tommy_lee

08.09.2021 13:45Конкретно топовые самсунги не особо продаются, продажи больше за счёт дешевого сегмента

YuriPanchul Автор

08.09.2021 17:16Это ваши субъективные ощущения или вы готовы привести табличку сравнений продаж worldwide с разбивкой по классам моделей и производителям?

YuriPanchul Автор

07.09.2021 17:29+1Вы вообще прочитали пост? Упражнения на ChipEXPO как раз привязывают Verilog к быстро осязаемым результатам, с музыкой и графикой.

Guul

09.09.2021 22:09В качестве хобби плис хорошо заходит. Вместо вноилога можно использовать няшные nmigen, chisel и тд.

neonkainside

11.09.2021 12:58Конечно не самая. Пишите на VHDL :) Но если серьёзно, то именно нудно писать на RTL сейчас мало что надо, только самые оригинальные части дизайна. Есть и библиотеки богатейшие и кодогенерация и всякие модные заходы типа chisel. Если разработчик пишет сам проект от и до, то это либо странный проект либо странный разработчик ИМХО.

YuriPanchul Автор

11.09.2021 17:36+2Обоже, оказывается все компании, в которых я работал последние 10 лет (MIPS, Imagination Technologies, Juniper Networks, Samsung и партнёр Samsung AMD) - "странные". А кто "нестранный", помимо SiFive с Chisel?

Какая-то кодогенеоация существует повсеместно - у одной компании внутренний препроцессор верилога, чтобы не писать длинные списки сигналов при инстанциациях, у других встроенный перл в верилоговскмй год, ещё много у кого специальный язык для описания регистров, который транслируется в верилог. Но все это - вещи довольно косметические и по их поводу говорить что якобы "на RTL пишутся только самые оригинальные части дизайна" - это просто не так, это видение не соответствует действительности в большинстве промышленных компаний.

Высокоуровневый синтез за 30 лет так и не пошел, кодогенеоация применяется ограниченно (регистры), мышкой на экране дизайны строятся только в презентациях на выставках от xilinx , а в реальном мире рисуют только микроархитектурные спецификации, а потом руками пишут много RTL-а родимого.

Блоки лицезируют, это да, но дизайны в компаниях где я работал за последние 10 лет, _не _ состоят из лицензируемых блоков - все свой RTL. Конечно у каждой компании есть своя библиотека из базовых компонент типа разнообразных FIFO и арбитров, но инстанциация их - это не бОльшая часть кода. Это просто как у программиста скажем на Си вызов библиотеки ввода-вывода типа printf - это не делает код "неоригинальным'.

neonkainside

11.09.2021 20:20Вы видимо не так меня поняли. Я говорил именно о сборке из своих блоков. И такой RTL пишется довольно быстро т.к. у всех все уже аккуратно обернуто.

YuriPanchul Автор

11.09.2021 20:35Ну хорошо, а то я уже подумал, что вы из тех, кто говорит "напишите просто формулы в mathlab, он сгенерит RTL, а потом объедините их мышкой на экране" :-)

neonkainside

11.09.2021 20:39Нет, я видел, как плохо это работает :) Единственный реальный хороший юзкейс для HLS ИМХО DSP. Там Vivado и правда неплохо себя показывала в тех примерах что я видел. Под кодогенерацией я имел ввиду не интерпретацию в RTL высокоуровневых языков, а скриптование работ с обертками библиотечных блоков.

YuriPanchul Автор

11.09.2021 20:40При этом кода custom компонент (не входящих в компанейские библиотеки) все равно довольно много, особенно для out-of-order процессирования транзакций, всякого sharing-а данных, fifo c опциями undo или вталкивания/выталкивания нескольких данных, custom математических операций c нетривиальным конвейером итд

neonkainside

11.09.2021 20:52Ну так такой RTL писать ИМХО совсем не нудно, не выгораешь :) Хотя и таких странных блоков со временем набирается порядочная библиотека.

3263927

08.09.2021 14:37вот интересное видео про процессоры кстати

amartology

08.09.2021 15:41+2engineer.yadro.com/events/semiconductors-shift

Вот видео про процессоры чуть получше вашего, от профессионального разработчика, а не от блдогера-недоучки, не отличающего систему команд от микроархитектуры, зато очеь любящего хайп.

rdevjke

08.09.2021 18:47-3Это когда директор синтакора обзавелся титулом "профессионального разработчика" ? Я уж лучше блогера хайпожора посмотрю, у него подача интересная.

amartology

08.09.2021 19:44+3Это когда директор синтакора обзавелся титулом «профессионального разработчика» ?

Полагаю, что еще когда в Intel работал. Человек получает зарплату за разработку микросхем, а значит по определению является разработчиком микросхем.у него подача интересная.

Интересно поданная смесь говна и вранья не становится от этого более осмысленной.

godlikebasic

08.09.2021 22:54-2Не понимаю, с чего вдруг "Генеральный директор" стал получать "зарплату за разработку микросхем"? Обычно директор руководит компанией и создаёт условия, чтобы (в данном случае) инженеры могли получать зарплату за разработку микросхем. Если он занимается разработкой сам, то он не директор, а просто инженер, не так ли?

К тому же, чем его мнение весомее инженеров из МЦСТ и Эльбруса? Именно они в основном преподносят техническую информацию в том видео, на которое вы совершенно беспардонно пытаетесь навешать ярлыки.

amartology

08.09.2021 23:08+5инженеров из МЦСТ и Эльбруса? Именно они в основном преподносят техническую информацию

Техническую информацию о том, что Джордж Лукас назвал приказ 66 в честь приказа Совмина СССР о копировании иностранных микросхем? Ну такое, ярлык некомпетентного хайпожорства это видео заслуживает на все 100%. Особенно те части, где говорит сам горе-блогер.Не понимаю, с чего вдруг «Генеральный директор» стал получать «зарплату за разработку микросхем»?

Нуууу я немного знаю, что умеет господин Редькин. Да и вы сами можете посмотреть видео и убедиться в его компетенциях.Если он занимается разработкой сам, то он не директор, а просто инженер, не так ли?

Основатели стартапов часто имеют инженерный бэкграунд и продолжают заниматься разработкой, скажем на уровне архитектуры, а не только ходят по встречам и перекладывают бумажки.

asmolenskiy

08.09.2021 15:44И это все?

Давайте поможем Юрию вывести тему в топ - зовите друганов своих.

gameplayer55055

08.09.2021 17:03Школьникам? Что это за школа такая? Может это всё-таки институт?

У нас в школе максимум что учили так это как рисовать в пеинте, и ворд

YuriPanchul Автор

08.09.2021 17:19На школу в Зеленограде приходили школьники из московских физматшкол и прекрасно со всем справлялись

trak

Мне кажется голосовалка так себе. Кроме пафосных топ-20 есть еще тесячи галер, где тоже можно работать. А за то что есть Syntacore / Yadro прям отдельное спасибо!

Mox

Я когда-то работал в Verilog галере (правда писал им софт на подобии lint, только для Verillog, на основе этой книжки - https://www.amazon.com/Reuse-Methodology-Manual-System-Designs/dp/0792381750), но у меня cложилось впечатление что аутсорс разработки микрохсем гораздо менее развит и все работают в продуктовых компаниях.

amartology

Продуктовые компании делают самостоятельно только то, что составляет их core competence, а все остальные блоки покупают. Объем рынка аутсорса IP-блоков — четыре миллиарда долларов.

Вот посмотрите на большой маркетплейс.

YuriPanchul Автор

$4B - это меньше 1% от всей semiconductor industry

amartology

Зато намного больше, чем весь российский рынок.

Mox

Делать свои IP Core на продажу - это совершенно не тоже самое что аутсорс галера, где инженеров сдают на проект заказчику.

Ну то есть ARM в моем понимании - не галера, а продуктовая компания.

order227

А вы не путаете аутсорс и аутстаффинговые компании?)

Было бы странным утверждать обратное. ARM разрабатывают и продают ядра, а точнее лицензию на них, то есть продукт в явном виде.

Аутсорс же компании продают не ядра и лицензии, а услуги по их разработке, по сути человеко-часы и компетенции. Их прибыль это RnD, а не продажа разработанных ядер.