30 октября прошло первое занятие Сколковской Школы Синтеза Цифровых Схем. Из-за Ковида его пришлось провести в онлайн-формате. Трансляция первого занятия:

Возможно онлайн-формат - это и к лучшему, так как в офлайне в Технопарке Сколково есть только 25 посадочных мест, и мы приготовили только 25 FPGA плат, а количество заявок привысило 300. Теперь мы на спонсорские деньги от компании Ядро Микропроцессоры и Максима Маслова @Armmaster заказали еще 100 плат и собираемся их раздать бесплатно для занятий дома, преподавателям вузов и руководителям кружков в других городах.

Чтобы быть уверенным, что получатели плат смогут их использовать, мы поставили в качестве пререквизита их получения прохождение короткого онлайн-курса от Роснано (см. детали в хабрапосте Готовимся к Сколковской Школе Синтеза Цифровых Схем: литература, FPGA платы и сенсоры). 40 с чем-то участников школы прошли этот курс и им будут высланы платы, как только заказанные платы прибудут из Китая.

При этом, так как школа уже началась, а до следующего занятия 13 ноября еще есть время, мы решили попробовать другой пререквизит - решение последовательности коротких задач на верилоге, используя не плату, а бесплатный симулятор Icarus Verilog. Всем участникам, которые собираются дойти в курсе до проектирования процессоров, все равно нужно будет освоить механику кодирования на верилоге, а для этого симулятор просто быстрее, чем учить это на FPGA платах.

Учить верилог в симуляторе Icarus так же просто, как учить программирование на питоне, за исключением того, что у верилога есть синтезируемое подмножество. То есть не все что вы можете сделать в симуляторе вы можете превратить в схему на фабрике или в прошивку в ПЛИС. Кроме этого в верилоге, в отличие от питона, есть физический тайминг, задержки в пикосекундах и максимальная тактовая частота, которые выясняются во время синтеза, то бишь одной симуляцией для обучения не обойтись. Тем не менее, упражнения на симуляторе - это оптимальный способ набить руку на многих вещах.

Идея та же, что научиться игре в шахматы или игре Го с помощью решения большого количества задач в несколько ходов. В качестве справочника для решения верилоговских задач можно использовать учебник Харрис & Харрис (планшетная версия, краткие слайды для лекций), лабник Цифровой Синтез и книгу Дональда Томаса (PDF начала к ней).

Пререквизит для получения плат будет состоять из двух групп упражнений. Первую группу мы уже выложили в составе пакета упражнений для школы:

ChipEXPO 2021 Digital Design School package v2.3

Ссылка через bit.ly - https://bit.ly/chipexpo2021dds23

Прямая ссылка

Если вы хотите не скачивать готовый пакет, а клонировать его из GitHub с некоторой настройкой, см. в конце поста инструкцию Приложение. Как клонировать пакет упражнений из GitHub и наcтроить его после этого.

Упражнения находятся в директории ce2020labs/quizes/problems_001_011. Это 11 файлов на верилоге. В каждом из них вначале пример модуля, потом незаконченный модуль, который вам нужно изменить (с комментарием TODO), а потом тест (модуль testbench). Как работает тест, вам понимать необязательно, про тесты объяснит Александр Силантьев из МИЭТ и Илья Кудрявцев из Самарского Университета на следующем занятии. Пока все что вам нужно сделать - это:

Установить Icarus Verilog по инструкциям ниже. Для него есть версии для Линукса, Windows и MacOS.

Прочитать модуль в начале файла.

Проконсультироваться со слайдами Александра Силантьева с первого занятия, а также возможно с книгами Харрис & Харрис, лабником Цифровой Синтез и книжкой Дональда Томаса, что все это значит.

Прочитать задание под комментарием TODO. Задание я написал на английском, если вы учили в школе другой язык, спросите на телеграм-канале DigitalDesignSchool объяснение задания.

Написать код из нескольких строчек под заданием.

Под Линуксом или MacOS: запустить скрипт run_all_using_iverilog_under_linux_or_macos_brew.sh . Его можно запустить из командной строки в терминале (на Apple тоже есть приложение Terminal если вы не знали) или просто кликнуть на него из менеджера файлов.

Под Windows: запустить пакетный файл run_all_using_iverilog_under_windows.bat . Его можно запустить из командной строки в терминале (на Apple тоже есть приложение Terminal если вы не знали) или просто кликнуть на него из менеджера файлов.

Скрипт или пакетный файл создаст файл log.txt с результатами компиляции и симуляции всех 11 файлов. Если что-то не скомпилировалось, там будет сообщение об ошибке syntax error. Если тест не прошел, там будет сообщение FAIL и информация об ожидаемом значении.

Когда все тесты пройдут, зазипуйте все что вы написали в один файл и пришлите в емейле мне ( yuri@panchul.com с копией yuri.panchul@gmail.com ), с копией Александру Силантьеву в МИЭТ ( olmer.aod@gmail.com ), Илье Кудрявцеву в Самарский Университет ( rtf@ssau.ru ) и Сергею Иванцу ( sergey.ivanets@gmail.com ) в Черниговский НПУ.

Если что-то непонятно, задавайте вопросы в телеграм-канал.

Задачи можно решать с любым симулятором верилога, который поддерживает SystemVerilog. А также c бесплатным симулятором Icarus Verilog, который хотя и не поддерживает весь SystemVerilog, но поддерживает Verilog 2005 с некоторыми элементами SystemVerilog, достаточных для решения наших задач.

.

Icarus Verilog чаcто используют с GTKWave, программой для работы с временными диаграммами. Для первых десяти задач GTKWave нам не понадобится, но его стоит установить вместе с Icarus Verilog на будущее.

Под Linux Icarus Verilog и GTKWave ставится "sudo apt-get install verilog gtkwave".

Версия Icarus Verilog и GTKWave для Windows здесь. !!! Важно !!! Нужно брать свежую версию iverilog-v11-20210204-x64_setup.exe [44.1MB] в которой есть поддержка некоторых конструкций SystemVerilog которые мы используем в примерах.

Icarus можно поставить даже на Apple Mac, что необычно для EDA tools (EDA - Electronic Design Automation). Это можно сделать в консоли с помощью программы brew: brew install icarus-verilog.

Видео установки Icarus Verilog для Windows

Примечание: если видео рекомендует старую версию, нужно скачивать новую (см. выше).

Видео установки Icarus Verilog для MacOS

Примечание: если видео рекомендует старую версию, нужно скачивать новую (см. выше).

Теперь про первые 11 задачек. Общая тема - мультиплексор - блок выбора. Если селектор стоит в 0, на выход идет значение из входа d0, иначе - значение из входа d1. Но даже такую незамысловатую функциональность в верилоге можно выразить минимум пятью способами:

Через операцию "?" и непрерывное присваивание (continuous assignment) - s001_mux_question.v

Через оператор "if" и блокирующее присваивание внутри комбинационного always-блока - s002_mux_if.v

Через оператор "case" и блокирующее присваивание внутри комбинационного always-блокаs - 003_mux_case.v

Через индекс двумерного массива типа logic - s004_mux_index.v

И даже просто через логические операции и/или/не, вместе с операцией размножения последовательности битов { n { m } } - что значит "построй последовательность состоящую из n копий последовательности m - s005_mux_gates.v

Можно строить большие мультиплексоры с многими входами из мультиплексоров с небольшим количеством входов. Этому посвящено упражнение s006_mux_2n_using_muxes_n.v, которое также вводит иерархию экземпляров модулей:

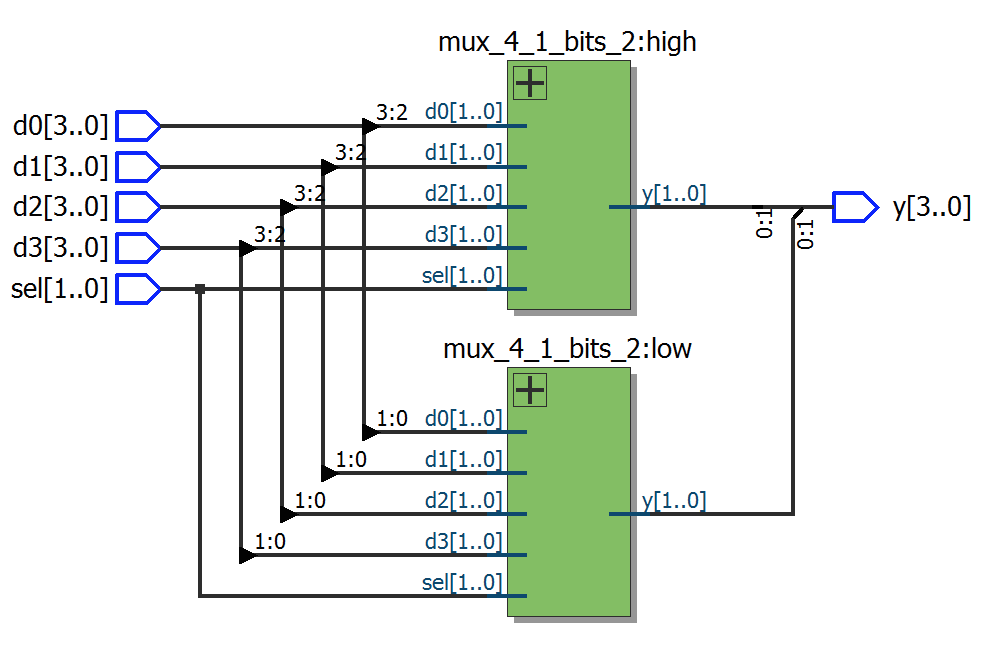

Также можно строить мультиплексоры для широких данных из мультиплексоров для узких данных - про это упражнение s007_mux_using_narrow_data_muxes.v.

Выше мы строили мультиплексоры из логических элементов И, ИЛИ, НЕ. А можно ли строить логические элементы И, ИЛИ, НЕ из мультиплексоров? Это посвящены четыре задачки, в которых нужно построить модули, реализующие комбинационную логику И, ИЛИ, НЕ и ИСКЛЮЧАЮЩЕЕ-ИЛИ (xor) только из мультиплексоров, констант 0 и 1, а также соединений между ними:

s008_not_gate_using_mux.v

s009_and_gate_using_mux.v

s010_or_gate_using_mux.v

s011_xor_gate_using_mux.v

Я не обещаю, что мы дойдем до задачи номер 999 (наверное это будет алгоритм Томасуло, который показывает девушка Ирина на рисунке 7.71 на фотографии ниже, и про который любят спрашивать недавних студентов на собеседованиях в электронные компании) но мы будем работать в этом направлении. Загружаем, приступаем и ждем вас на занятии 13 ноября, которое по-видимому начнется с разбора этих задачек.

Приложение. Как клонировать пакет упражнений из GitHub и наcтроить его после этого

Вместо использования готового пакета упражнений (и для симуляции, и для синтеза) вы можете клонировать его код из двух репозиторий GitHub-а:

https://github.com/DigitalDesignSchool/ce2020labs

https://github.com/zhelnio/schoolRISCV

После клонирования вам нужно запустить башевский скрипт ce2020labs/scripts/create_run_directories.bash, находясь при этом в директории ce2020labs/scripts. Этот скрипт создает временные директории run с копиями скриптов для синтеза и симуляции в каждой поддиректории, в которой есть файл top.v. В директориях run потом скапливаются все временные файлы, которые создает Intel FPGA Quartus и другие программы. Сами run директории игнорируются в .gitinfo чтобы случайно не занести временные файлы в github.

Под Линуксом и MacOS скрипт запускается прямолинейно:

cd ce2020labs/scripts

./create_run_directories.bash

Под Windows это тоже будет работать, так как если вы установили Git для Windows то у него внутри есть встроенный интерпретатор bash в директории "C:\Program Files\Git\usr\bin", а также другие нужные для скрипта утилиты: sed и линуксный вариант find. Вам нужно будет точно так же пойти в директорию скрипта и запустить его, используя bash:

cd ce2020labs\scripts

bash create_run_directories.bash

Если у вас под Windows что-то не работает, проверьте, какие директории стоят у вас в path. Вот что стоит у меня:

C:\Program Files (x86)\Common Files\Oracle\Java\javapath

Java понадобиться на занятии про архитектуру RISC-V, так как ее использует симулятор RARSC:\Program Files\Git\cmd

C:\Program Files\Git\mingw64\bin

C:\Program Files\Git\usr\binC:\intelFPGA_lite\20.1\quartus\bin64

C:\intelFPGA_lite\20.1\modelsim_ase\win32aloem

ModelSim внутри пакета intelFPGA - это симулятор Verilog, мощнее и быстрее чем Icarus. Однако версия ModelSim в последнем бесплатном пакете intelFPGA не поддерживает черты SystemVerilog, которые мы используем в задачах, например тип logic.C:\Program Files (x86)\GnuWin32\bin

Здесь установлены GNU утилита make.exe, которая нужна для занятий про микроархитектуру RISC-V, а также линуксная версия zip.exe для формирования пакета скриптом create_ce2020labs_zip.bashC:\iverilog\bin

C:\iverilog\gtkwave\bin

forthuser

Интересно, а в какой степени и для каких задач можно сделать и применить решения на

Verilog, VHDL ресурса rosettacode.org?

Так, к примеру, на этом ресурсе:

21 решённая задача на Verilog

и 11 решённых задач на VHDL

+ 12 решённых задач на SystemVerilog

P.S. Или задачи, представленные для решения на этом ресурсе больше подходят для Софт-процессоров реализованных в составе FPGA?

Сводная подборка информации по проектам Софт процессоров

Но, есть же к примеру проект и сообщество ПО FlProg

где даже в рамках логических элементов делают ПО под контроллеры Ардуино.

(не видно, вроде, проектов где для контроллеров общего применения был бы применён VHDL, Verilog ...)

YuriPanchul Автор

Я ткнул в несколько примеров в rosettacode и к сожалению эти примеры не имеют вообще никакого отношения к дизайну микросхем на верилоге и просто используют верилог как язык программирования. ну это как использовать автомобиль жигули для занятия любовью на парковке. Ну то есть так можно, диван в нем есть, но это не то, для чего он предназначен.

Например http://rosettacode.org/wiki/100_doors#Verilog

Где здесь сигналы, логика, регистры, стадии конвейера, иерархия модулей итд? Что это вообще демонстрирует? Что в нем можно делать аналог printf для написания тестов.

Еще хуже сложение http://rosettacode.org/wiki/A%2BB#Verilog

В GrayCode приведено использование как выше и модуль с логикой. Второе можно использовать, но так как оно приведено вместе с первым, то для начинающего не понятно что с этим делать - писать как в первом варианте или во втором? При том что первый вариант не имеет никакого отношения к реальному использованию Verilog http://rosettacode.org/wiki/Gray_code#Verilog

Вот это вообще не пример, просто ошметки конструкций написанный человеком не в теме (command? он что, думает что верилог - это скриптовый язык?) http://rosettacode.org/wiki/Conditional_structures#Verilog

C VHDL и SystemVerilog то же самое - люди не в теме взяли справочник по языку, выдернули из него понятное лично для них по аналогии с другими языками и написали нечто, что уводит от реального использования. Если увидите там хоть один реальноподобный пример, кроме модульной версии gray counter я привел выше - покажите, мне интересно что там еще можно нарыть. Половина примера из 10 случайно ткнутых.

YuriPanchul Автор

*** Сводная подборка информации по проектам Софт процессоров ***

Анализировать код софт-процессора для новичка, который не знает что такое последовательностная логика, как она выражается в верилоге (always @ (posedge clock)) и во что превращается (D-триггеры) так же бесполезно, как анализировать код Си-компилятора, даже простого типа LCC или PCC - человеку, который не знает что такое указатель, стек, дерево выражения или парсирование. И не умеет писать на Си.

YuriPanchul Автор

Более того, софт-процессор софт-процессору рознь.

Прежде всего, софт-процессор используется в двух контекстах:

Чтобы противопоставить процессор реализованный в FPGA, процессору, реализованному в ASIC, например стоящему рядом с FPGA ядру ARM в Zynq. Проблема в том, что и для первого и для второго процессоры пишутся на верилоге, то есть между ними нет приниципиальной разницы, только всякие мелочи типа использование специального макро DSP48 в Xilinx FPGA для оптимизации ALU.

В компаниях процессорного IP, например MIPS Technologies где я работал, одно и то же ядро (например MIPS 4K используемое в микроконтроллерах Microchip PIC32) могло продаваться и как soft core, и hardened core (то есть не с исходниками а в виде "черного ящика" инстанциируемого в системе на кристалле заказчика на этапе физического проектирования). Принципиальной разницы тут нет - это как продавать программу либо в исходниках на Си, либо в виде скопилированной библиотеки - .lib, .dll, .so.

Так вот возвращаясь к вашей табличке, софт-процессор софт-процессору рознь. На одних (schoolRISCV) который мы используем в курсе, можно понять идею процессора, потому что он очень маленький (300 строк на верилоге). Если же вы возмете например процессорное ядро с конвейером используемое в микроконтроллерах, или не дай бог ядро T1 выпущенное на волю Sun-ом, то там для новичка, который вообще не знает концепции конвейера - это просто темная масса кода в десятки тысяч строк (есть в тысячи и в сотни тысяч, но идея понятна)

YuriPanchul Автор

*** Но, есть же к примеру проект и сообщество ПО FlProg

где даже в рамках логических элементов делают ПО под контроллеры Ардуино. (не видно, вроде, проектов где для контроллеров общего применения был бы применён VHDL, Verilog ...) ***

Я не разбирал, что это, похоже что-то очередное no-code программирование. Если это так, это не имеет вообще никакого отношения к вопросу. Программирование микроконтроллера - это написание программы, кода, который превращается в цепочку инструкций, которые процессор вытаскивает из памяти и изменяет по этому поводу свое состояние. Проектирование на верилоге на уровне регистровых передач - это в частности конструирование самого процессора.

Разница как между умением водить автомобиль (программирование) и умением проектировать его двигатель (проектирование на уровне регистровых передач).

Я нарисовал для этого вот такие поясняющие картинки: