Глубокие нейронные сети (DNN) способны решать сложные задачи в областях, связанных со встроенными системами, таких как обработка изображений и естественного языка. Чтобы эффективно реализовать DNN на конкретной платформе ПЛИС для заданного критерия стоимости, например, энергоэффективности, необходимо учитывать огромное количество параметров проектирования, начиная с топологии и заканчивая конечной аппаратной реализацией. Необходимо учитывать и эффективно исследовать взаимозависимости между различными уровнями проектирования, что делает поиск оптимизированных решений вручную едва ли возможным.

Автоматический, целостный подход к проектированию может значительно улучшить качество реализации DNN на ПЛИС. С этой целью мы представляем метод исследования межслойного пространства проектирования. Методика включает в себя оптимизацию, начиная с поиска топологии DNN c учетом аппаратного обеспечения и заканчивая окончательной оптимизированной реализацией для данной платформы ПЛИС. Методология реализована в нашей системе комплексного автоматического машинного обучения на ПЛИС (Holistic Auto machine Learning for FPGAs – HALF), которая объединяет алгоритм эволюционного поиска, различные этапы оптимизации и библиотеку параметризуемых аппаратных модулей DNN. HALF автоматизирует как процесс поиска, так и реализацию оптимизированных решений на целевой платформе ПЛИС для различных приложений. Мы демонстрируем работу HALF на примере медицинского применения с целью обнаружения аритмии для трех различных целей проектирования, т.е. низкое энергопотребление, низкая мощность и высокая производительность. Наша реализация на ПЛИС превосходит оптимизированную модель TensorRT на платформе Nvidia Jetson как по пропускной способности, так и по энергопотреблению.

I. Введение

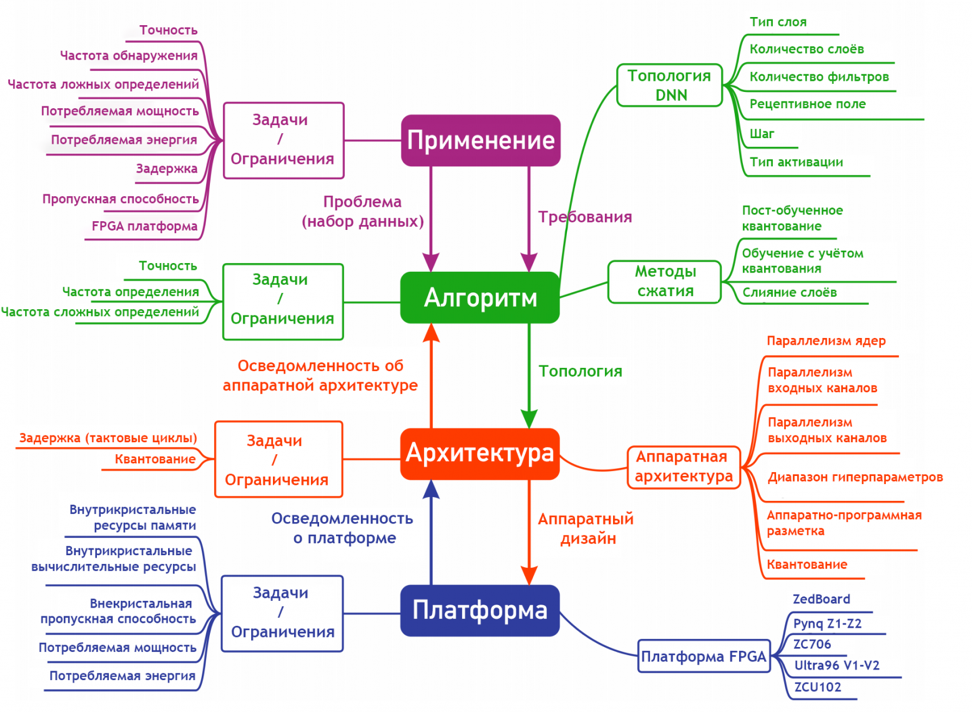

Эффективная реализация глубоких нейронных сетей (DNN) в аппаратном обеспечении требует тщательного исследования пространства проектирования на различных уровнях абстракции, включая алгоритмический, архитектурный и платформенный уровни, как показано на рис. 1.

Во-первых, приложение определяется набором данных и требованиями с точки зрения ограничений и целей, например точность, задержка и т.д. На самом высоком уровне иерархии проектирования находится алгоритм, который представляет собой наиболее абстрактное описание потока данных и управления в виде топологии DNN. Архитектурный уровень отображает топологию на аппаратное проектирование, которое реализуется на платформе. На самом низком уровне находится платформа, которая описывает аппаратное обеспечение и его физические свойства. Все уровни проектирования предусматривают большое количество вариантов проектирования и взаимозависимости (см. рис. 1).

В нашей методологии архитектурный уровень представлен высокопараметризируемым шаблоном архитектуры, который используется для создания различных топологий DNN в аппаратном обеспечении. Мы формулируем аппаратные модели для задержки, мощности и энергии, полученные из шаблона архитектуры, выраженные в терминах гиперпараметров топологии, чтобы включить осведомленность об оборудовании в алгоритм. Аппаратные модели вместе с шаблоном архитектуры описывают связь между алгоритмическим уровнем и уровнем платформ. Однако одной связи недостаточно, поскольку зависимость приложения от архитектурного уровня не может быть формализована. Для этого мы используем нейронный поиск архитектуры (NAS) в алгоритмическом слое и дополняем его моделями аппаратной осведомленности архитектурного уровня.

NAS выполняет полную межуровневую оптимизацию, которая руководствуется целями оптимизации, направленными как на требования приложений, так и на производительность оборудования. В итоге аппаратно-осведомленный NAS в тесной связи с архитектурным шаблоном и его моделированием прокладывает мост от приложения до уровня платформы, что позволяет полностью автоматизировать процесс проектирования для оптимизированных реализаций.

Методология реализована в рамках фреймворка HALF, который включает в себя аппаратно-ориентированный эволюционный NAS и среду реализации для ПЛИС (Field-Programmable Gate Array – FPGA), а также библиотеку аппаратного обеспечения. Мы демонстрируем эффективность нашего подхода на примере энергоэффективного внедрения ПЛИС для обнаружения фибрилляции предсердий в реальном сценарии применения, используя набор данных, предоставленный клиникой Charite´ в Берлине. Новаторский вклад этой статьи заключается в следующем:

Методология исследования пространства проектирования, позволяющая межуровневую оптимизацию DNN для эффективной аппаратной реализации;

Платформа, автоматически создающая решения для ПЛИС с низким энергопотреблением, малой мощностью или высокой пропускной способностью;

Библиотека параметризуемых аппаратных архитектур слоев DNN с низким энергопотреблением и сверхнизкой задержкой;

Мы демонстрируем реализацию ПЛИС для обнаружения аритмии в различных сценариях применения, которая превосходит встроенный GPU по пропускной способности, мощности и энергоэффективности.

II. Соответствующая работа

A. Поиск нейронной архитектуры

Для задачи обнаружения аномалий в данных электрокардиограммы (ЭКГ) в [1, 2, 3, 4] показано, что 1D-сверточные нейронные сети (1D-CNNs) могут использоваться с необработанными образцами ЭКГ без ручного извлечения признаков. Вместо того чтобы вручную разрабатывать топологии DNN для конкретной задачи обнаружения, NAS описывает методы, которые автоматически исследуют пространство поиска, охватываемое архитектурами DNN.

Среди наиболее успешных методов – градиентные и эволюционные методы. В последнее время наблюдается меньшая активность вокруг подходов, основанных на обучении с подкреплением (RL), поскольку и градиентные, и эволюционные методы могут дать схожие результаты за зачастую значительно меньшее время [5, 6]. Тем не менее, методы RL исследуются в сочетании с аппаратным обеспечением для аппаратных ускорителей [7] и ПЛИС [8]. Наиболее известным градиентным методом является поиск дифференцируемой архитектуры (DARTS) [9], который ищет подграфы в большем дифференцируемом суперграфе. В [5] DARTS была введена аппаратная поддержка в виде минимизации задержки для мобильных телефонов. Авторы работы [10] использовали очень похожую на [5], установку DARTS, но для ПЛИС, а задержки слоев моделировались в качестве функций гиперпараметров топологии вместо таблиц поиска. Хотя DARTS работает очень быстро, структура суперграфа, разработанного вручную, может привести к сильному смещению.

В свою очередь, эволюционные алгоритмы не требуют суперграфа. Генетические алгоритмы используют кодировку для описания структуры DNN, что позволяет использовать такие вдохновленные биологией понятия, как кроссинговер [11] и старение [6], для реализации. Морфизмы сети представляют собой класс операторов структуры графа, которые изменяют DNN таким образом, что переобучение с нуля не требуется [12, 13]. В [13] морфизмы сети используются в алгоритме LEMONADE, который использует байесовский метод для генерации DNN в многоцелевом поиске, хотя и не является аппаратно-ориентированным. Оба [13] и [8] различают «дешевые» и «дорогостоящие» задачи и пропускают ненужные, «дорогие» вычисления плохих кандидатов. Позже [14] LEMONADE была дополнена аппаратной ориентированностью и устойчивостью к ошибкам.

B. Автоматическая генерация аппаратного обеспечения и аппаратные архитектуры для DNN

Среди наиболее используемых фреймворков для автоматической генерации аппаратных средств – FINN [15], Xilinx ML Suite [16], который представляет собой инструментарий для разработки движка общей обработки xDNN [17], и набор для разработки глубоких нейросетей (Deep Neural Network Development Kit – DNNDK) [18], представляющий собой SDK для процессорного блока глубокого обучения (DPU) [19] программируемого движка. Однако ни одна из них не является полностью автоматическим подходом, а скорее наборами инструментов, которые помогают преобразовать DNN в пользовательский ускоритель ПЛИС, например FINN, или скомпилировать их в последовательность инструкций, выполняемых на программируемом движке. Все фреймворки предоставляют инструменты для сжатия и оптимизации DNN и поддержку времени выполнения.

И Xilinx ML Suite, и DNNDK нацелены на реализацию DNN на программируемых движках, которые предназначены для поддержки широкого спектра топологий DNN. Они жертвуют гибкостью взамен на универсальность. Напротив, FINN использует библиотеку аппаратного обеспечения высокоуровневого синтеза (HLS) [20] аппаратных слоев и компонентов, которые используются для создания потоковых архитектур, адаптированных для каждой сети. Другие инструменты для автоматической генерации аппаратного обеспечения – FlexCNN [21], интегрирующий структуру реализации ПЛИС в Tensorflow, и DNNBuilder [22], который использует совместное проектирование программного и аппаратного обеспечения для выполнения сквозной оптимизации приложений глубокого обучения.

Наш подход похож на FINN. В частности, он отображает DNN в наборе высоко оптимизированных аппаратных компонентов. Концептуально система HALF отличается от всех предыдущих подходов, поскольку включает в себя NAS для топологий, оптимизированных для аппаратного обеспечения. Кроме того, мы нацелены на полностью автоматическое решение.

Существуют публикации по дополнению NAS аппаратной осведомленностью для ПЛИС. В [10] предлагается NAS для их ускорителя, способного обрабатывать CNN послойно, подобно xDNN и DPU. Что касается аппаратной осведомленности, их подход оптимизирует DNN только для низкой задержки. В [8] предложена схема совместной разработки аппаратного и программного обеспечения, которая использует NAS для оптимизации DNN для реализации на нескольких ПЛИС, однако без особого внимания к оптимизации на уровне отдельных ПЛИС. Их подход в первую очередь ориентирован на оптимизацию для обеспечения высокой пропускной способности.

Наша система отличается тем, что мы используем аппаратно-ориентированное сетевое хранилище данных для архитектуры в стиле потока данных, полностью построенной на кристалле, настроенной для каждой сети и оптимизированной для различных целей, а именно: низкая задержка, низкая мощность и низкое энергопотребление.

III. Платформа HALF

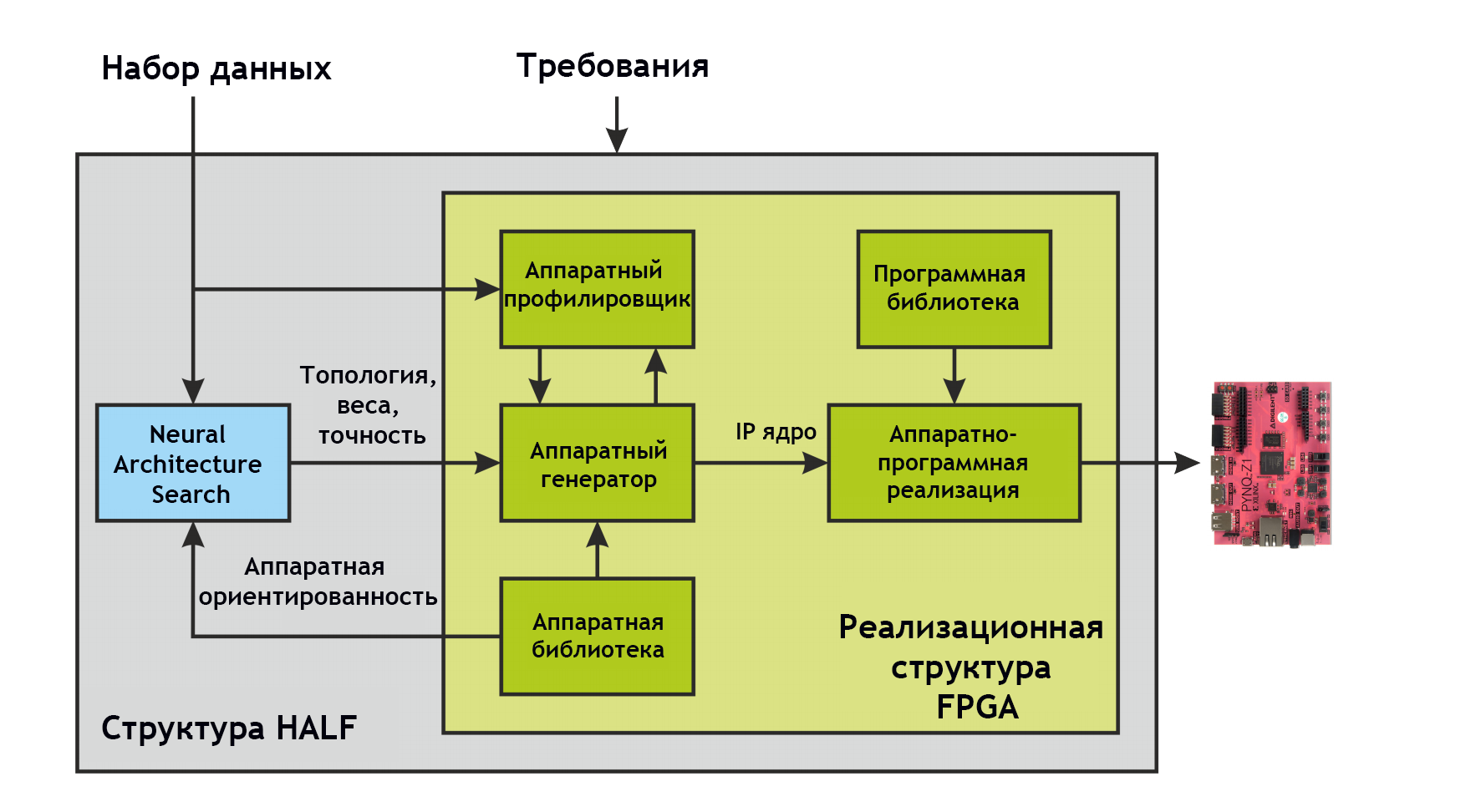

Платформа HALF состоит из двух основных компонентов – аппаратно-ориентированной системы NAS и системы реализации на ПЛИС (см. рис. 2). Входными данными являются набор данных и требования, заданные в виде ограничений и целей оптимизации на уровне приложения и аппаратного обеспечения. На выходе получается аппаратная конфигурация для выбранной платформы ПЛИС, которая удовлетворяет требованиям.

HALF генерирует вывод автоматически и поэтому значительно ускоряет развертывание DNN на ПЛИС. NAS занимает около двух дней, в зависимости от сложности основного пространства поиска и набора данных, в то время как ручной поиск занял бы недели, даже без учета аппаратной ориентированности. Включение аппаратной ориентированности в NAS сокращает трудоемкий ручной цикл проектирования и оценки различных реализаций ПЛИС для выявления кандидатов с наилучшими компромиссами. Автоматическая генерация и реализация аппаратуры занимает всего несколько часов, в отличие от ручного процесса проектирования аппаратуры, который может занять несколько дней или даже недель, особенно если аппаратные компоненты должны быть разработаны с нуля.

A. Поиск нейронной архитектуры

NAS является первым шагом системы и находит оптимальные топологии для структуры реализации. Он основан на очень гибком эволюционном алгоритме, который не накладывает сильных ограничений на пространство поиска или объективные функции, особенно последние не обязательно должны быть дифференцируемыми. Мы используем генетический алгоритм, предложенный в [23], который ускоряет поиск с помощью концепции спящих генов.

Для стратегии выбора мы используем аналогичный метод, основанный на байесовском подходе, как в [13], который эффективно исследует границу Парето кандидатов DNN в двухэтапной процедуре, предварительно отбирая кандидатов на основе вычислительно недорогих целей. В дополнение к этой двухэтапной процедуре в [13] используются сетевые морфизмы для увеличения пропускной способности полностью оцененных DNN. Мы не используем сетевые морфизмы, это ограничивает диапазон операций мутации, а также плохо подходит для нашего генетического кодирования. Вместо этого мы справляемся с большой обучающей нагрузкой, реализуя динамический планировщик нагрузки, который использует параллельную обработку в высокопроизводительных вычислительных системах (HPC).

Аппаратная осведомленность включается дважды, т.е. через пространство поиска и цели оптимизации. Пространство поиска ограничено слоями, которые включены в библиотеку оборудования, таким образом, модели из NAS гарантированно сопоставимы с устройством. Это включает в себя такие аспекты, как типы слоев и допустимые комбинации гиперпараметров, а также квантование входов, весов и карт признаков. Вторая составляющая аппаратной ориентированности определяется целями оптимизации, описанными в разделе IV. Перед передачей найденной топологии с обученными весами в систему аппаратной реализации для дальнейшего сжатия модели применяются методы предварительной обработки и настройки, такие как пакетная обработка.

B. Структура реализации ПЛИС

Схема реализации ПЛИС включает в себя генератор аппаратного обеспечения, пользовательскую библиотеку аппаратного обеспечения, профилировщик, библиотеку программного обеспечения и этап реализации аппаратно-программного обеспечения. Генератор аппаратного обеспечения создает аппаратную архитектуру нейронной сети, используя компоненты из аппаратной библиотеки, описанной в разделе V. Используя Xilinx Vivado HLS, платформа генерирует ядро интеллектуальной собственности (IP) из топологии DNN, которое основано на слоях библиотеки аппаратного обеспечения. На данный момент веса моделей также интегрированы в IP-ядро, поскольку аппаратная архитектура использует только встроенную память для хранения моделей. Кроме того, она создает экземпляры интерфейсов для связи с внешней памятью и буферов FIFO для подключения элементов. Генератор аппаратного обеспечения также вычисляет коэффициенты распараллеливания для каждого уровня, которые основаны на требуемой пропускной способности и в основном определяются целевой платформой, т.е. количеством ресурсов, доступной пропускной способностью памяти и моделью ПЛИС. В то время как квантование весов и активаций обеспечивается NAS, квантование для внутренних накопителей определяется путем профилирования. Профилировщик определяет оптимальный диапазон и точность для всех накопителей в аппаратном обеспечении и соответственно устанавливает ширину битов. На последнем этапе аппаратно-программной реализации Xilinx Vivado Design Suite используется для создания битового потока для ПЛИС. Программное обеспечение компилируется для запуска на процессорных ядрах платы, которая используется для передачи входных и выходных данных в ПЛИС и для управления IP-ядром.

IV. Аппаратно-ориентированные целевые функции

Мы выбираем энергию, мощность и задержку в качестве целей, учитывающих аппаратное обеспечение, и моделируем их в качестве функций топологии и параметров ПЛИС. Задержка определяется как

где N-количество слоев, nin,j – количество значений для первоначального заполнения входного буфера (например, размер ядра в случае слоев с преобразованием), σj−1 – скорость вывода предыдущего слоя в тактах, а lj-задержка слоя для получения своего вывода. Обратите внимание, что σi = max(li , σi−1) вычисляется рекурсивно и описывает конвейерную природу аппаратной архитектуры. Задержки li зависят от типа слоя и гиперпараметров, таких как шаги и размер ядра, а также от факторов развертывания цикла αi реализации ПЛИС. В разделе VI представлены результаты с использованием пропускной способности вместо задержки, которая включает в себя вклад параллелизма данных и представляет собой размер пакета, деленный на общую задержку ttotal

Мы моделируем эффективную мощность, так что энергия может быть просто описана как произведение времени работы и эффективной мощности. Общая потребляемая мощность составляет

Pmem – это мощность от операций с памятью и в основном не зависит от топологии, поскольку в нашей архитектуре все веса и активации хранятся на чипе. Размер входной выборки, однако, влияет на Pmem, но, поскольку входные данные всегда должны считываться и не могут быть оптимизированы, их вклад в модель мощности исключается. Однако модель для Pmem может быть легко добавлена в структуру. Pboard относится к другим периферийным компонентам аппаратной платформы, но, поскольку на него не могут влиять параметры топологии, он не моделируется. Pstat и Pdyn – это статическое и динамическое энергопотребление архитектуры, которое мы моделируем в общей мощности с помощью

Мы предполагаем, что мощность линейно зависит от коэффициента разворачивания цикла αi. P*idle,i и P*calc,i являются энергопотреблением, когда слой простаивает и вычисляет, соответственно, для коэффициента разворачивания, равного единице, который можно оценить с помощью аппаратного профилировщика среды реализации ПЛИС. ta,i – это время, в течение которого слой активно вычисляет, и оно является произведением общего числа выходов, которые производит слой, умноженное на задержку для получения одного такого вывода. Мощность может быть сведена к минимуму за счет отсутствия развертки (min α) и увеличения общего времени выполнения с соблюдением ограничений по задержке.

Общая энергия – это произведение эффективной общей мощности на общее время выполнения

Глядя на уравнение (4), кажется, что минимизация αi – лучшая стратегия минимизации энергии. Однако, поскольку высокий αi уменьшает как ttotal, так и ta,i суперлинейно, именно высокие коэффициенты разворачивания снижают общее потребление энергии. Кроме того, энергия, потребляемая всей платформой, равна произведению Pboard и ttotal. Поскольку Pboard может быть намного больше, чем другие вклады в Ptotal, минимизация ttotal является наиболее эффективным способом снижения измеряемого энергопотребления.

V. Аппаратная библиотека

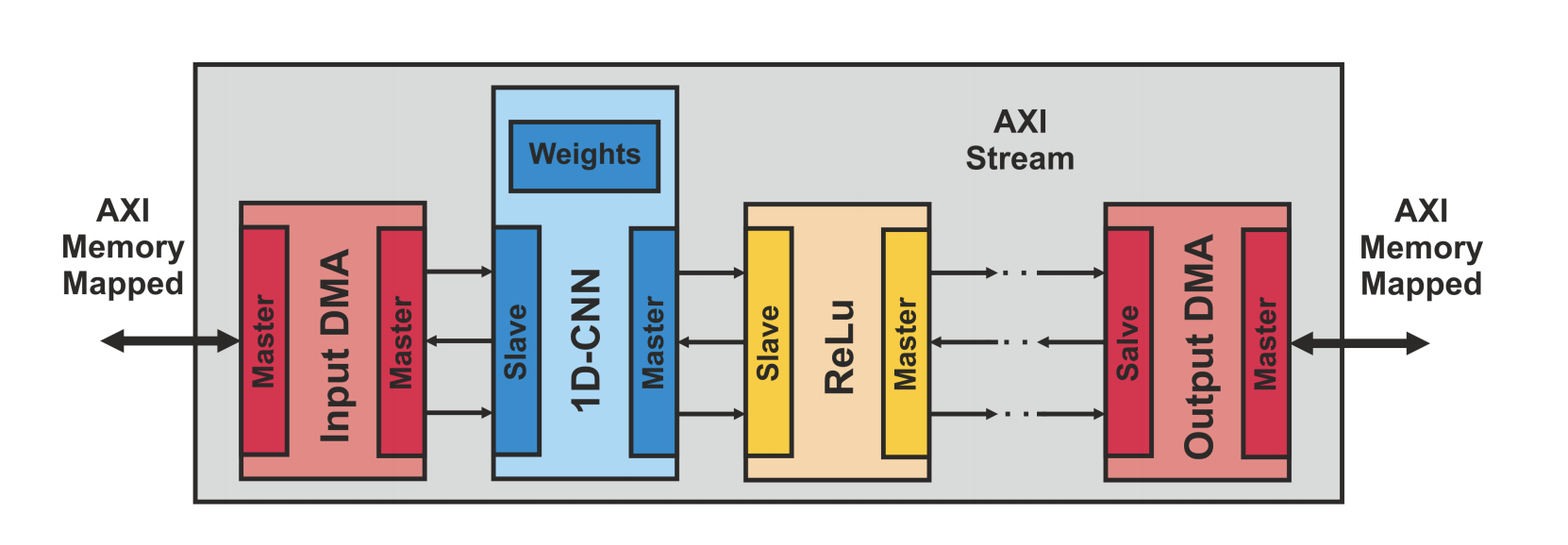

Мы представляем аппаратную библиотеку HLS, состоящую из пользовательских аппаратных архитектур для стандартных 1D-DNNs, разделяемых по глубине 1D-DNNs и различных других слоев и компонентов DNNs. Аппаратные архитектуры хорошо настраиваются, что позволяет реализовать различные нейронные топологии. Библиотека аппаратного обеспечения написана как набор шаблонных функций C++ с аннотациями HLS и модульной структурой, что позволяет легко расширять ее за счет новых слоев.

Архитектура аппаратного обеспечения разработана с учетом низкого энергопотребления и сверхнизкой задержки. В первую очередь, это достигается за счет хранения всех весов и промежуточных результатов в памяти на кристалле, поскольку передача данных за пределы кристалла потребляет больше энергии и вносит дополнительные задержки. Внешняя память используется только для чтения входных данных и записи результатов, сокращая доступ к памяти до абсолютного минимума. Архитектура полностью конвейерная, что позволяет всем уровням работать одновременно и начинать вычисления, как только входные данные готовы, чтобы уменьшить задержки и энергопотребление. Библиотека основана на архитектуре потока данных, которая может быть легко настроена для каждой сети. Аппаратные модули разработаны с потоковыми интерфейсами для быстрого проектирования, отладки, совместимости и простоты интеграции. Отдельные аппаратные модули, предназначенные для каждого уровня, соединяются с помощью потоков данных на кристалле в единый модуль верхнего уровня под названием Deep Neural Network Unit (DNNU), как показано на рис. 3. Модуль верхнего уровня оснащен компонентами прямого доступа к памяти (DMA), которые обеспечивают доступ к внешней памяти независимо от процессора с помощью интерфейсов AXI-Master.

В конвейерной архитектуре всегда существует стадия «бутылочного горлышка», которая определяет задержку всего конвейера. Задержка данного этапа может быть уменьшена за счет пространственного параллелизма, который мы называем развертыванием (от англ. от loop unrolling). Аппаратная библиотека разработана с параметризуемым разветыванием, которое эффективно распараллеливает узкие места. Параметризация позволяет осуществлять крупнозернистое распараллеливание на уровне фильтров для слоев CNN и нейронов для полносвязанных слоев, и мелкозернистое распараллеливание на уровне точечных произведений, различая параллелизм на уровне ядра и входных каналов.

VI. Результаты

Эффективность нашей методики оценивается на задаче бинарной классификации для обнаружения аритмии на основе ЭКГ. Набор данных, предоставленный университетской клиникой Charite´ в Берлине, содержит 16000 образцов, с 2 каналами и длиной 60000 каждый. Набор данных содержит равное количество положительных и отрицательных образцов. Производительность задачи измеряется в частоте обнаружения и ложных тревог, где мы определяем жесткие границы в 90 % и 20 % для принятия соответственно.

NAS выполняется на четырех графических процессорах Nvidia Titan X для 100 поколений с 20 детьми в каждом поколении, что занимает два дня. Пространство поиска состоит из разделяемых по глубине сверток и 60 различных конфигураций гиперпараметров и максимальным объединением с 4 различными шагами. Все DNNs заканчиваются слоем глобального среднего пулинга, за которым следует полносвязный слой. Глубина топологии выбирается NAS, но ограничена между 2 и 15 слоями (конечные слои не включены). Целями оптимизации являются мощность, энергия и задержка с разворачиванием и без него, а также количество параметров, частота обнаружения и ложных тревог. Все цели рассматриваются одновременно на границе Парето.

A. Влияние целей NAS на топологию

Топология сети сама по себе оказывает большое влияние на конечную производительность с точки зрения мощности и энергии, что мы показываем, сравнивая модели, оптимизированные для трех различных целей: низкая мощность с минимальным распараллеливанием (low P, min α NAS), низкое энергопотребление с минимальным распараллеливанием (low E, min α NAS) и низкое энергопотребление с максимальным распараллеливанием (low E, max α NAS). Случай min αNAS применяется, когда аппаратные ресурсы относительно малы по сравнению с размером модели DNN, поэтому полное разворачивание невозможно. Случай (low P, max α NAS) исключается, так как цель низкого энергопотребления и максимального разворачивания приводит к неразумным топологиям, которые вряд ли могут быть развернуты при проектировании. Модели, оптимизированные для высокой пропускной способности, такие же, как и для энергии, поэтому в явном виде здесь не рассматриваются. Для стратегии реализации мы устанавливаем коэффициент распараллеливания α Impl либо равным единице, либо максимальным, сохраняя остальные параметры, связанные с аппаратным обеспечением, фиксированными.

Таблица I показывает, что лучшие результаты по энергии и мощности получаются, если цель оптимизации совпадает со стратегией реализации. Это демонстрирует эффективность подхода межуровневой оптимизации, когда факторы распараллеливания, связанные с аппаратным обеспечением, влияют на поиск топологии, что приводит к лучшим решениям. Три топологии, использованные в таблице I, имеют значимые различия в своей структуре, как показано на рис. 4. Для первых двух моделей, обе оптимизированные по энергии, поиск сходится к очень похожему решению. Особенно первые слои идентичны и положение слоев с шагом идентичны. Связь между родителями и детьми с точки зрения эволюции исключена, поскольку мы выбрали обе модели из двух разных экспериментов.

ТАБЛИЦА I: Измерения мощности и энергии с использованием различных целей и полученных топологий.

Задача NAS |

Стратегия реализации |

Пропускная способность [samples/s] |

Ptotal [Вт] |

Etotal [мкДж] |

low E, max α NAS |

min α Impl. |

4.4 · 103 |

4.42 |

1010 |

low E, min α NAS |

min α Impl. |

5.3 · 103 |

4.46 |

841 |

low P, min α NAS |

min α Impl. |

1.4 · 103 |

4.40 |

3120 |

low E, max α NAS |

max α Impl. |

4.8 · 105 |

8.22 |

1.7 |

low E, min α NAS |

max α Impl. |

3.7 · 105 |

7.16 |

2.0 |

low P, min α NAS |

max α Impl. |

8.3 · 104 |

6.10 |

73.8 |

![Рис. 4. Сравнение топологий для различных целей оптимизации. Синий – разделяемая по глубине свертка, зеленый – размер ядра 1. В полях: [#параметры], (ширина вывода, каналы). Рис. 4. Сравнение топологий для различных целей оптимизации. Синий – разделяемая по глубине свертка, зеленый – размер ядра 1. В полях: [#параметры], (ширина вывода, каналы).](https://habrastorage.org/getpro/habr/upload_files/a2b/5da/6fe/a2b5da6fec36da4f84d6aaba1133776d.png)

Ключевое различие исходит от 3-го слоя свертки, который становится узким местом в случае min α Impl, чего не происходит в случае max α Impl. Во 2-й модели используется размер ядра, равный единице, что значительно снижает латентность всего конвейера. Это приводит к более высокой энергоэффективности, хотя параметров в два раза больше. Для случая max α Impl 1-я модель имеет меньшее энергопотребление, так как ей требуется меньше ресурсов, поэтому можно реализовать больше параллельных экземпляров и увеличить пропускную способность. 3-я топология на рис. 4 менее глубокая, чем оптимизированные по энергии модели. Без разворачивания более мелкая топология требует меньше аппаратных ресурсов. Узким местом является 3-й сверточный слой, который вычисляется в два раза дольше, чем следующий по скорости слой. Это накладывает большое время простоя на слои, не являющиеся узким местом, что приводит к снижению энергопотребления, хотя они имеют почти в три раза больше параметров, чем 1-я модель.

Таким образом, не размер модели, а ее структура определяет производительность оборудования. Модель NAS способна находить значительные структурные особенности в моделях DNN, основываясь на целях оптимизации.

B. Эффективность целостной методологии

Чтобы продемонстрировать эффективность нашего целостного подхода, мы представляем решения для трех различных областей, а именно для малой мощности, низкого энергопотребления и высокой пропускной способности, с оптимизацией, применяемой на всех уровнях проектирования, от NAS до платформы ПЛИС, см. таблицу II. В каждом случае целевая платформа была выбрана в соответствии с целью оптимизации, Pynq-Z1, Ultra96-V2 и ZCU102 для каждой цели соответственно. Кроме того, мы показываем результаты для топологии с низким энергопотреблением, реализованной на встроенном графическом процессоре Nvidia Jetson AGX Xavier, оптимизированном с использованием TensorRT.

Для цели низкого энергопотребления NAS искал топологию, которая демонстрирует наименьшую мощность с коэффициентом разворачивания, ограниченным единицей (low P, min α). В свою очередь, механизм аппаратной реализации позволил применить только один полностью свернутый DNNU, реализованный с наименьшей частотой, который, однако, все же превосходит требования реального времени. Хотя NAS включает в себя отдельные цели для низкого энергопотребления и высокой пропускной способности, мы наблюдаем, что лучшей моделью для обоих случаев является одна и та же, которая оптимизируется с учетом максимального коэффициента разворачивания (низкое E, низкое L, максимальное α). Следующий этап аппаратной реализации был нацелен на разные платформы, но использовал идентичные стратегии для достижения наивысшей частоты и максимального использования доступных ресурсов путем создания максимального количества экземпляров с максимальным коэффициентом разворачивания (α = 40). Таблица II демонстрирует, что каждая реализация достигает наилучших результатов в целевой области. Проекты на ПЛИС превосходят встроенную реализацию на GPU по всем показанным метрикам, хотя GPU имеет более высокую частоту, больший размер пакета и модель, оптимизированную с помощью TensorRT.

ТАБЛИЦА II: Сравнение реализаций ПЛИС для различных доменов.

Устройство |

Частота [Мгц] |

Размер партии |

Пропускная способность [samples/s] |

Ptotal [Вт] |

Etotal [Дж] |

Pynq-Z1 |

0.5 |

1 |

2.1 |

1.9 |

9.1·10−1 |

Ultra96-V2 |

333 |

4 |

4.8·105 |

8.22 |

1.7·10−5 |

ZCU102 |

322 |

16 |

1.6·106 |

33.9 |

2.1·10−5 |

Jetson AGX |

1377 |

1024 |

7.7·104 |

21.1 |

2.7·10−4 |

VII. Заключение

Мы представляем методику межуровневой оптимизации, которая позволяет подбирать DNNs, оптимизированные для аппаратного обеспечения. Методология основана на аппаратно-ориентированном NAS в сочетании с параметризуемым аппаратным шаблоном. Мы реализовали этот подход в автоматической среде и продемонстрировали его эффективность, сравнив мощность и энергию для моделей DNNs, оптимизированных для различных целей. Цели значимо влияют на структуру генерируемых сетей, так что реализации моделей превосходят друг друга по соответствующим целям оптимизации. Кроме того, мы используем весь потенциал нашего механизма, автоматически применяя оптимизации, связанные с аппаратным обеспечением, которые дополнительно настраивают модель в зависимости от целевой платформы. Учитывая все аспекты проектирования аппаратной реализации, мы ориентируемся на различные домены и показываем значительные различия в аппаратных показателях для реального сценария применения обнаружения фибрилляции предсердий, превосходя Nvidia Jetson AGX по пропускной способности, мощности и энергопотреблению.