Презентации использовавшиеся во время доклады от Imagination: panchul.com/dropbox/2014_10_26/presentations

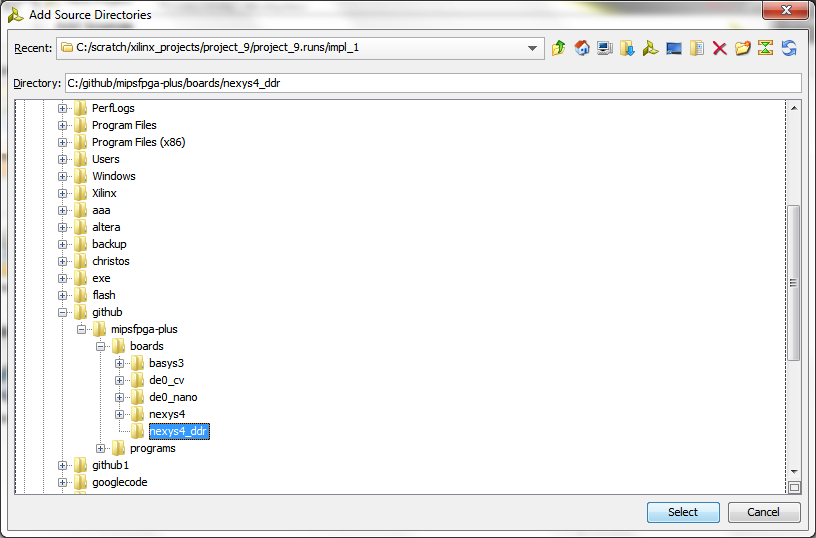

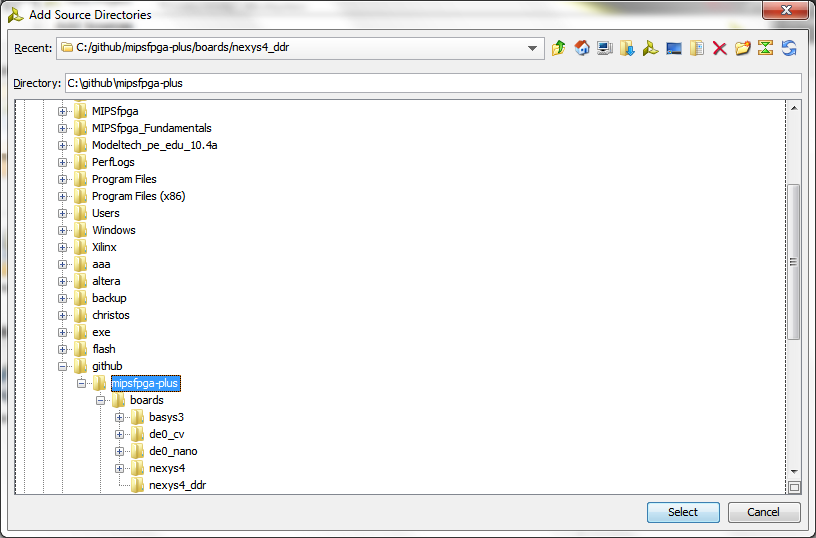

Основной код для лабораторных работ: github.com/MIPSfpga/mipsfpga-plus

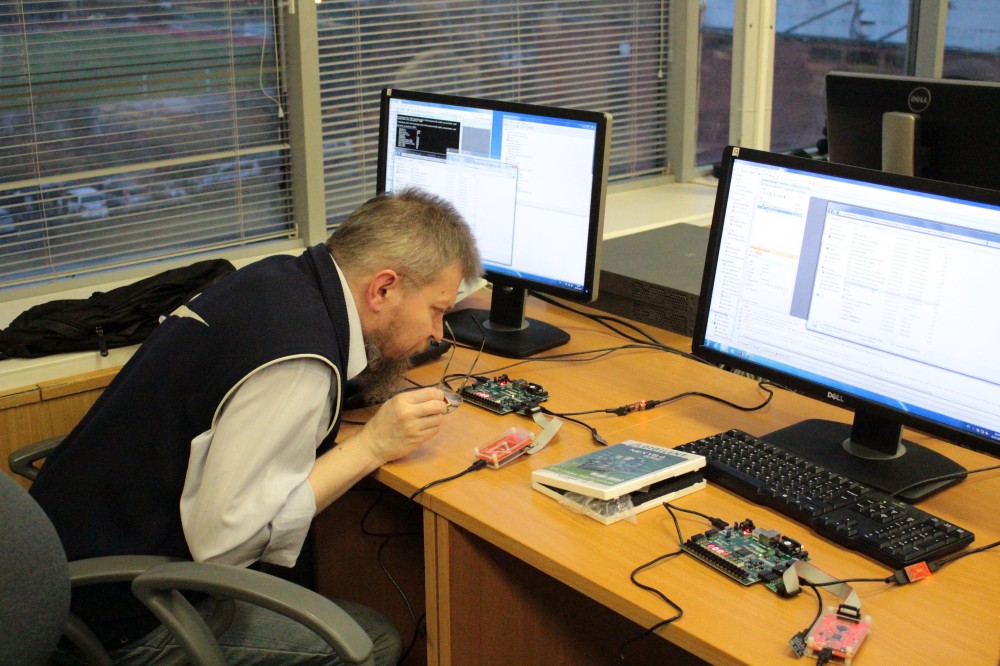

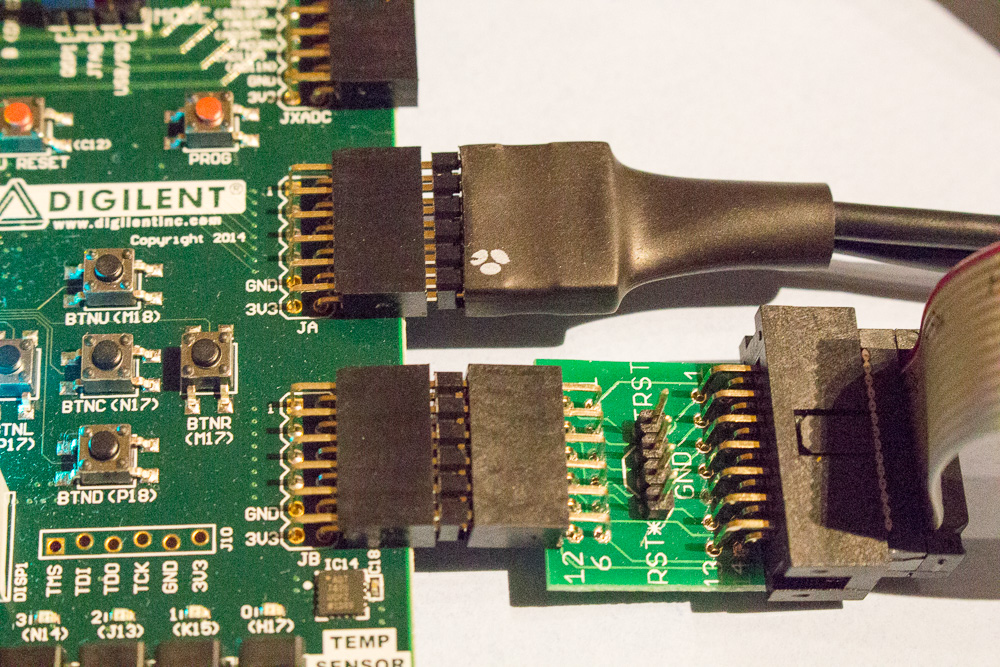

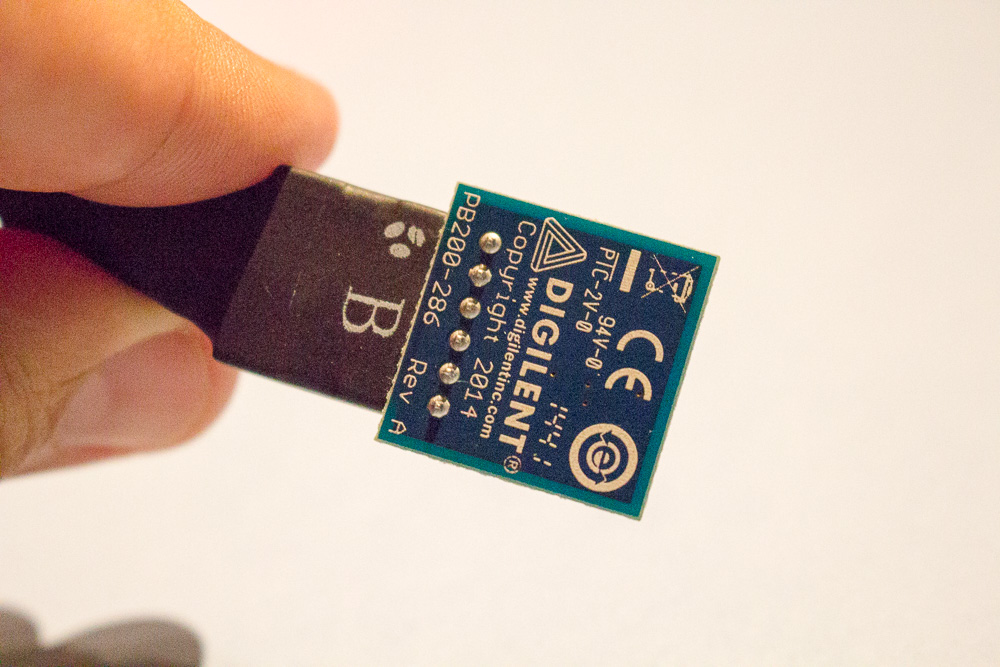

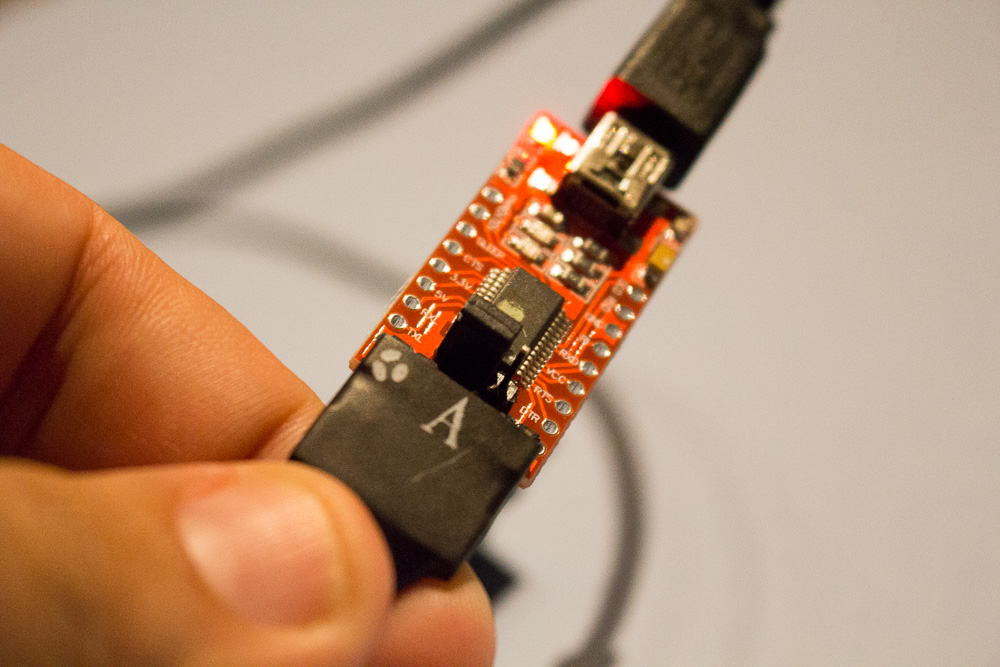

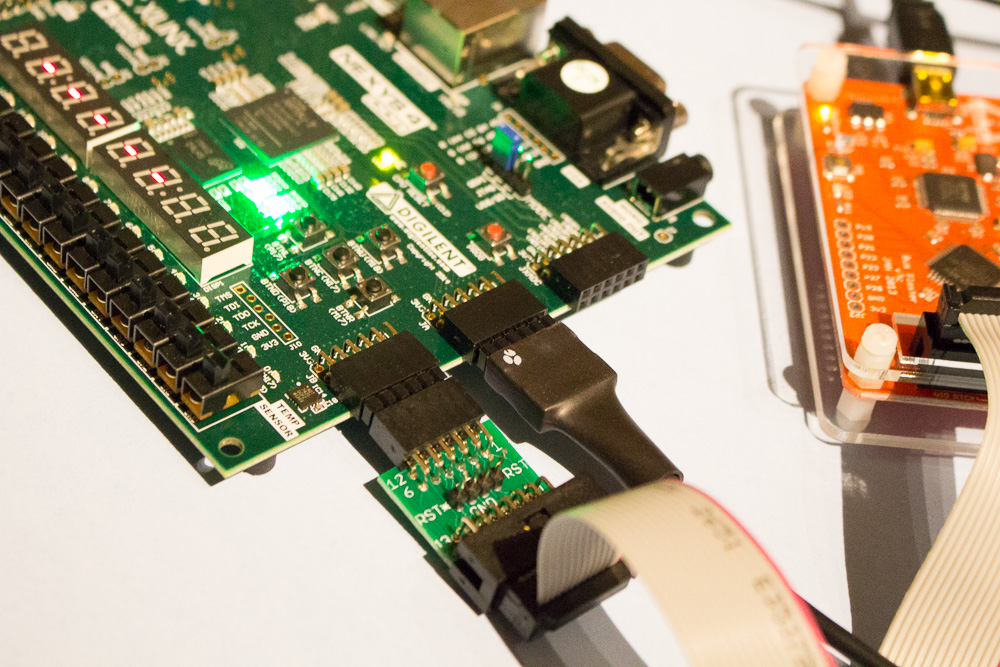

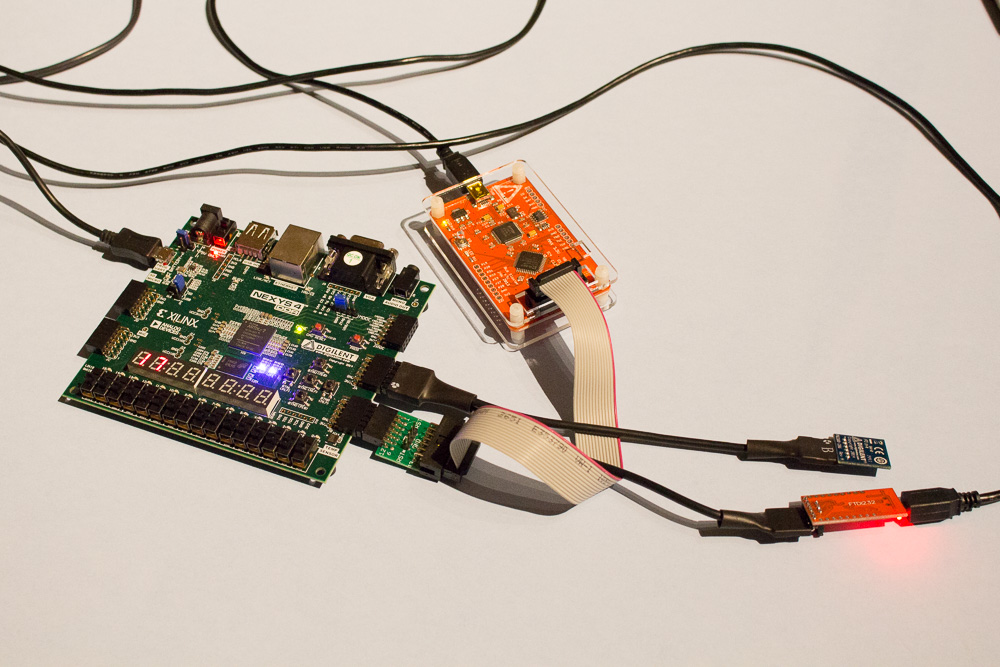

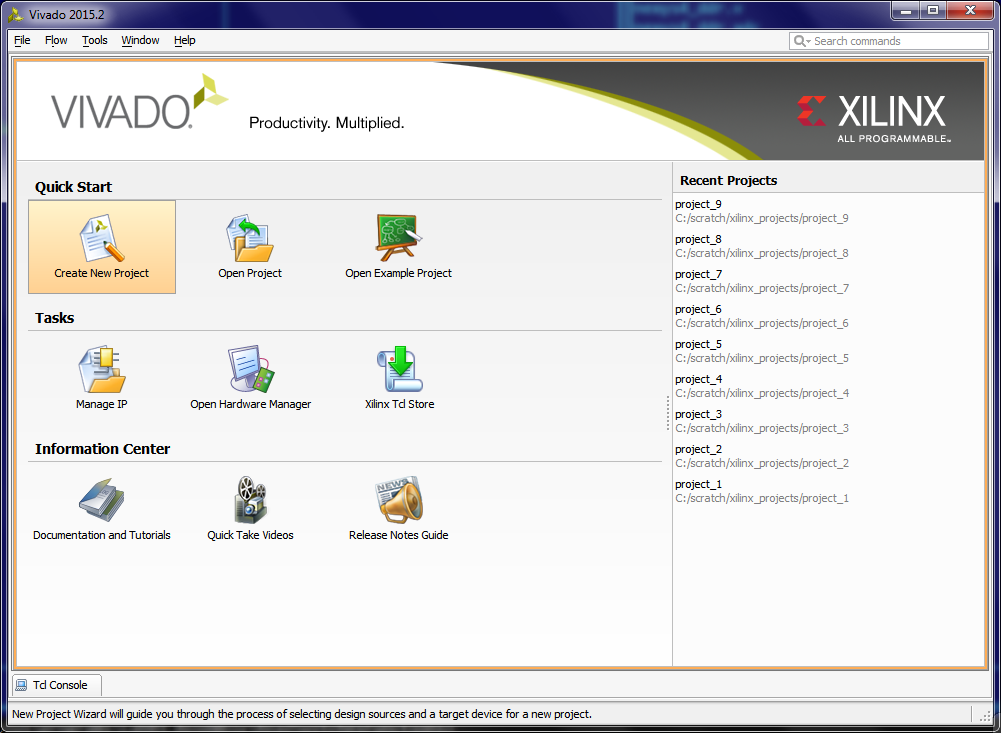

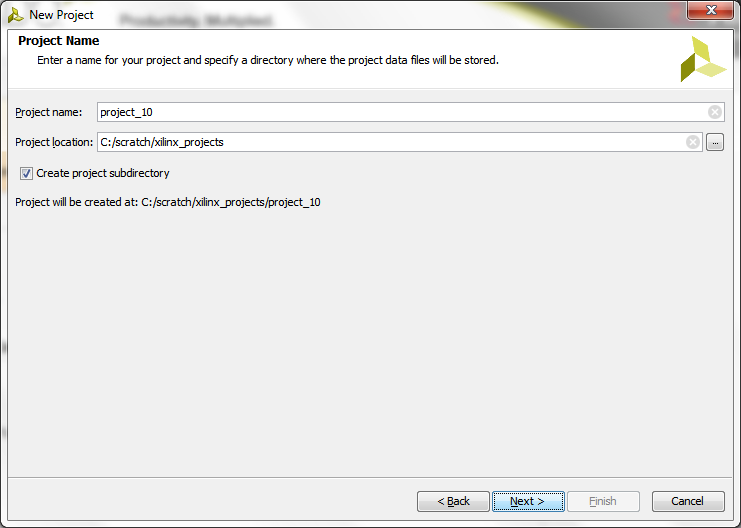

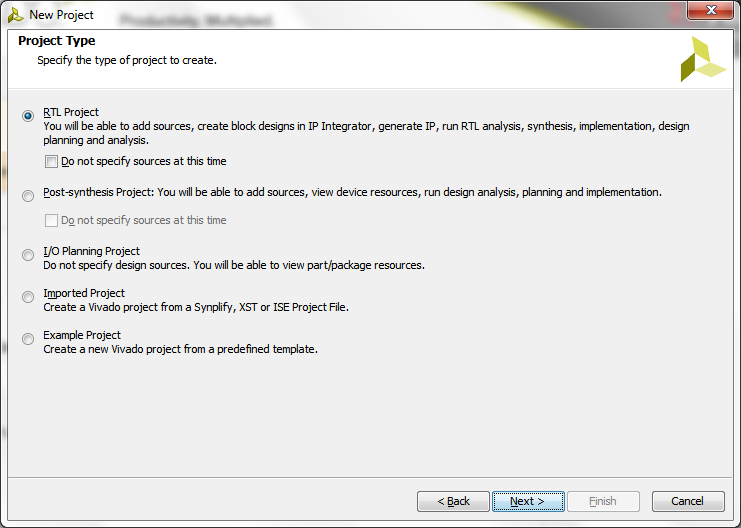

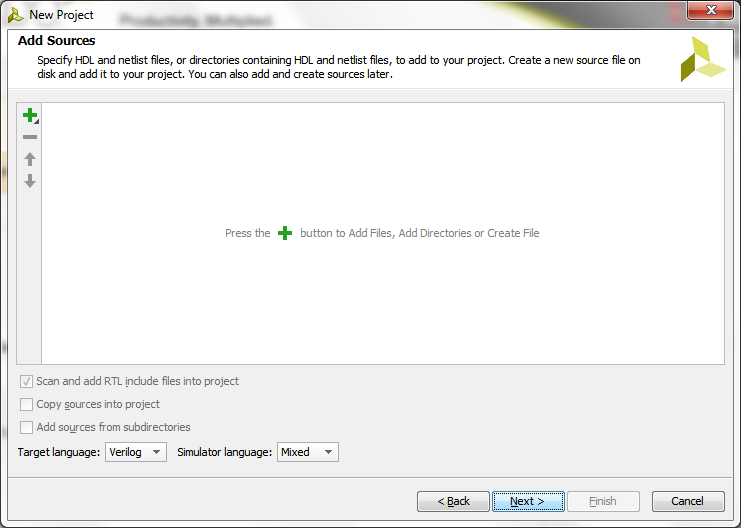

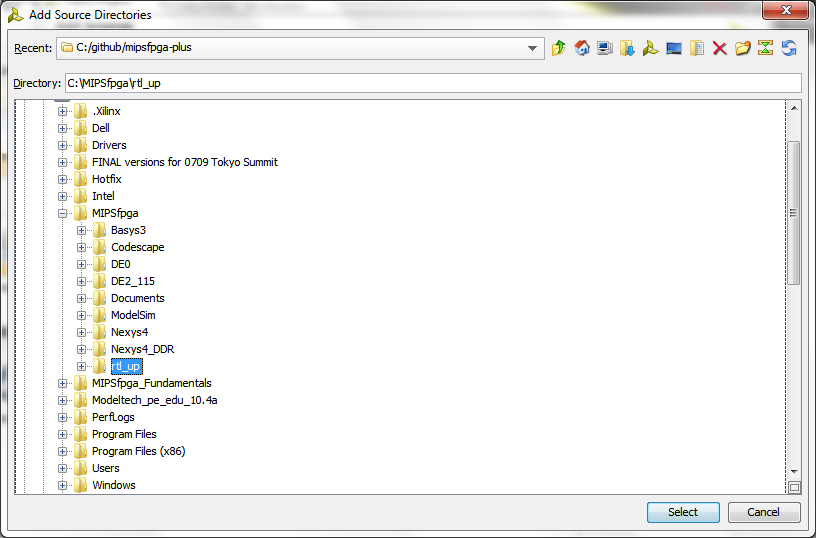

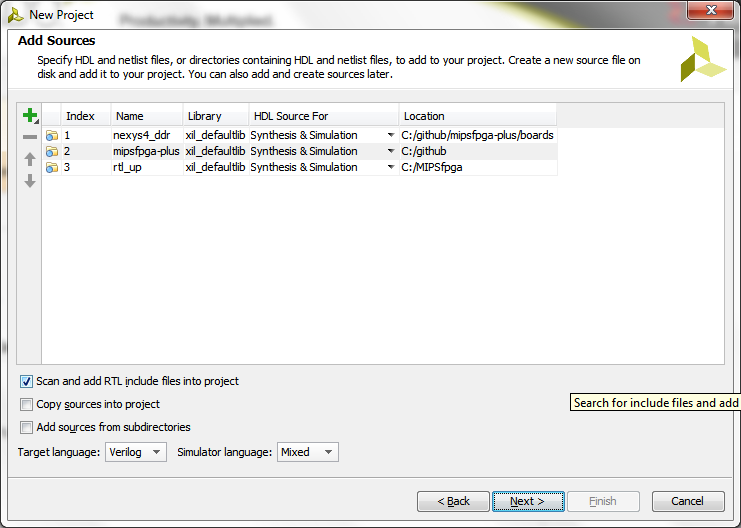

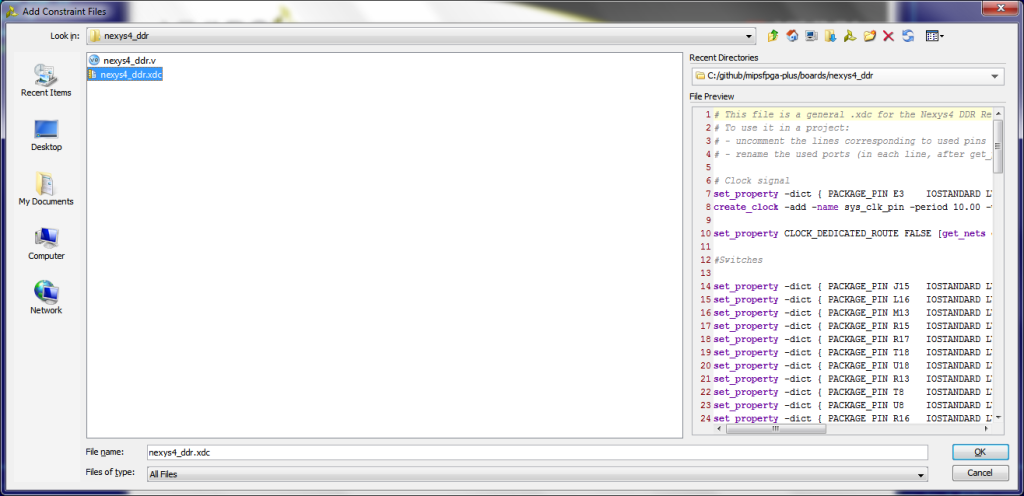

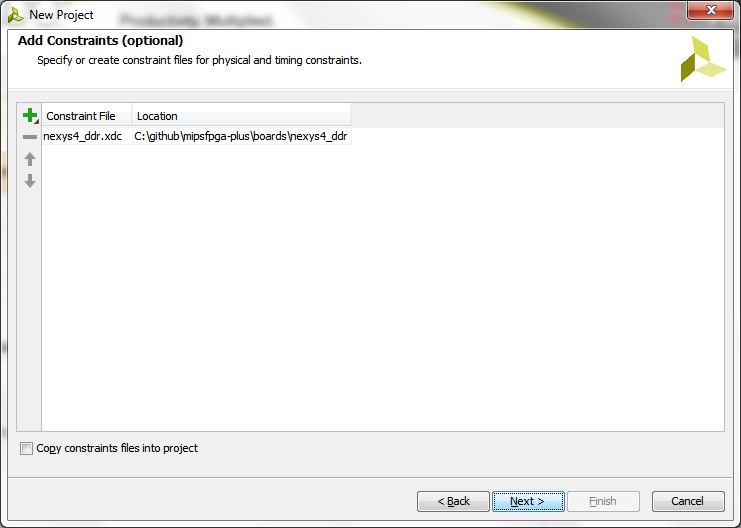

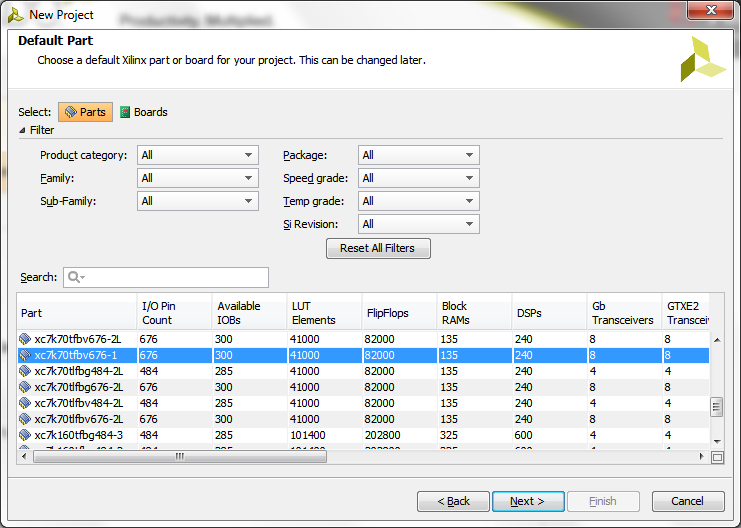

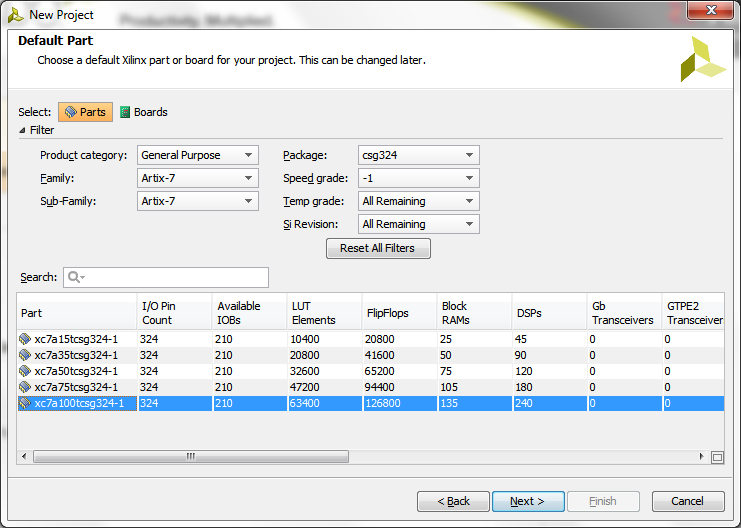

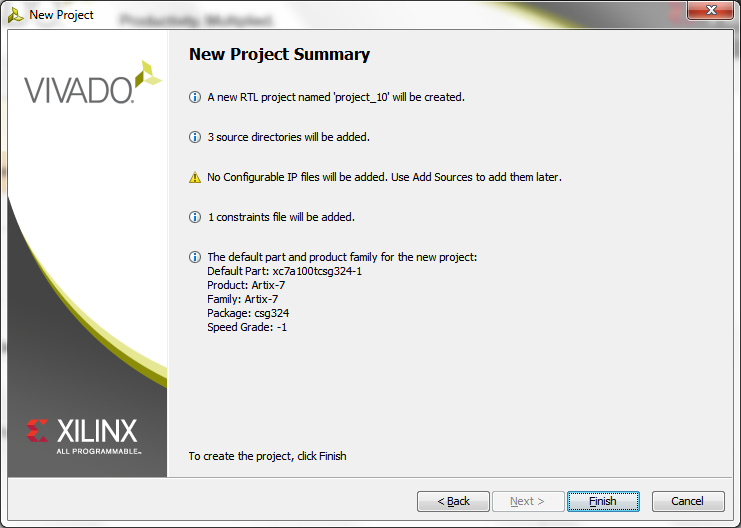

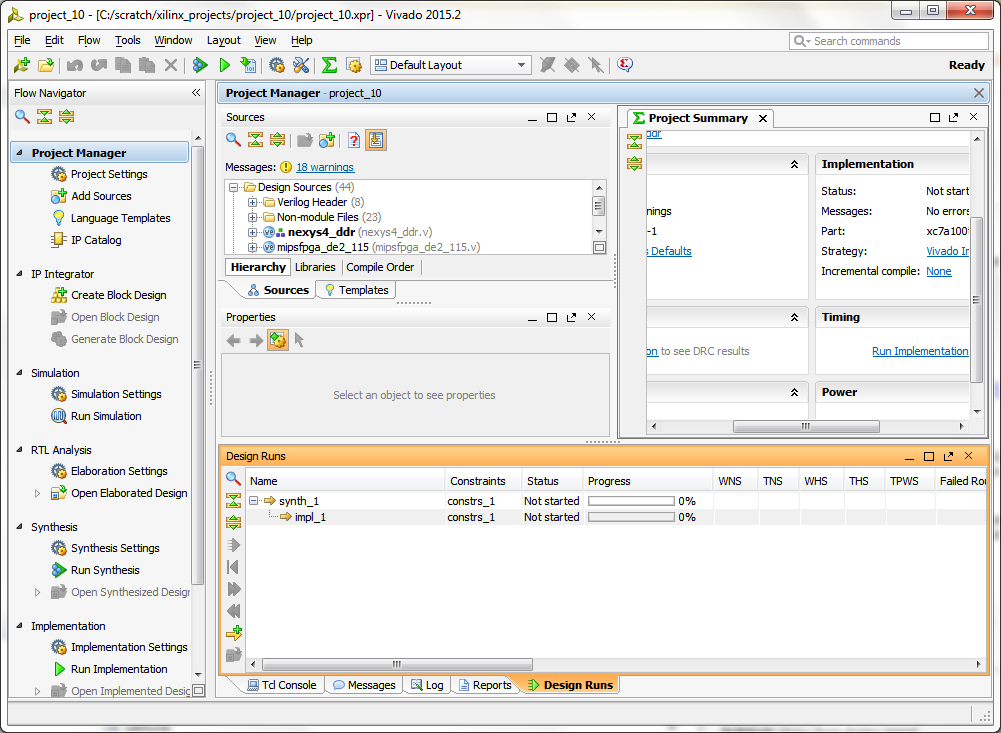

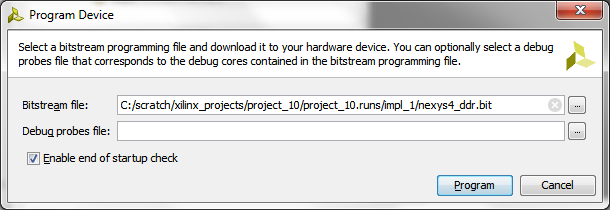

Соединения плат и создание проекта в Xilinx Vivado:

Комментарии (12)

rPman

27.10.2015 18:56Известно ли, что является главной причиной, почему FPGA сопроцессоры до сих пор не встраивают в потребительскую электронику, десктопные компьютеры и главное мобильные? Есть даже Zynq-Z7010/Z7020 ARM процессор (единственный известный мне десктопный компьютер с ним и адекватной ценой)

AlexanderS

27.10.2015 20:52Целесообразность использования: цена и времемя разработки.

ПЛИСы могут выполнять обработку данных быстро, работать на очень высоких частотах, с информационными потоками высокой скорости. В потребительской электронике некуда торопиться: для большинства задач подойдут обычные массовые копеешные МК работающие на 1-20МГц, под которые есть куча библиотек и требуется больше программист, нежели инженер-схемотехник. На борту МК уже есть АЦП/ЦАП, библиотеки для организации интерфейсов и прочие вкусности и не надо все это подключать к ПЛИСу и разбираться с обменом на низком уровне всей этой периферии. Типичный пример: вот в этой статье я написал как делал для себя платку электроники на ПЛИСе от проекта Marsohod, я бы всё то же самое мог сделать на ардуине нано, купленной за 100р., ещё и код бы получился в 3 раза меньше.

Конечно, не стоит совсем уж недооценивать микроконтроллеры. Есть и серьёзные вещи под серьёзные задачи.

Разработка на ПЛИС это… как свободное творчество. Степень контроля совсем другая. Код не работает построчно, а за один такт выполняется весь код. Описывая схему нужно продумывать все мелочи, любое неточное описание работы схемы приведет к её непредсказуемому результату в целом, нужно контролировать каждый сигнал. Одно и то же действие можно написать так, что бы оно выполнялось максимально быстро или максимально экономно по ресурсам, но можно и варьировать.

Но зато, разработка получается долгая. Для приёма по RS надо писать целый приёмник, который будет отсчитывать длину такта UART в зависимости от тактовой частоты, собирать этот байт побитно, проверять бит чётности, организовывать буфер, в который этот байт будет складываться и вычитываться по мере надобности следующей схемой. Т.е. надо ещё и физ. уровень UART понимать. Плюс предусмотреть если будут сбои при сборке байта — схема не должна испортиться и «вылечиться» на сборке следующего байта… А на ардуине написал Serial.read() и этот байт уже используешь дальше )))

rPman

27.10.2015 21:45Я категорически с вами не согласен практически по всем пунктам!

ПЛИС нужна именно для энергоэффективной очень быстрой обработки данных, именно то, чего так нехватает в потребительской мобильной технике!

ПЛИС — это не только эмулятор железа — но вполне подходит и для общих вычислений, но даже без этого, в список задач можно смело положить обработку видео с видеокамеры, 100500 задач, от превращения смартфона в беспроводной джойстик для игр на большом экране (очень точный контроль за положением) до таких задач как отслеживание слежения за направлением взгляда (технологии несколько лет но из-за слабого железа невозможна на текущем железе, а хардварщики не спешат добавлять это в каждое второе устройство, доступны единицы ноутбуков за неадекватные деньги).

Все тут точно так же как и с развитием software, зачем делать под каждый чих новое устройство, когда можно разделять и властвовать — отдели сенсоры от анализа, и оставь последнее за процессором. А миллион программистов найдут еще 100500 необычных применений этим сенсорам.

Проблема сложности разработки под ПЛИС — это сложность входа, как минимум из-за очень дорогих (неадекватно, в смысле необоснованно) отладочных плат. Если для изучения программирования ПЛИС будет достаточно обычного компьютера — програмистов появится на порядок больше, а за ними и инструментарий будет развиваться гораздо быстрее.

Последний ваш абзац — один в один то, что происходило, когда разработчики писали на ассемблере… и кто теперь думает 'о байтах и битах' при разработке домашней странички дяди васи?

UA3MQJ

27.10.2015 23:26Со временем становится легче. ПЛИС программируются на обычном компьютере. Отладочная плата нормального уровня (3-5 тыс ячеек), стоит 1000р. Байты собирать самому тоже не надо. Разработка на ПЛИС происходит БЛОЧНО. Я лично, свой приемник RS232 не писал, а взял готовый модуль. Среды разработки (во всяком случае от Altera точно), позволяют не писать самому модули ЦОС, генераторов и прочее, предоставляя Cores. То есть вопрос разработки на ПЛИС — это соединение блоков. Это даже, как мне кажется, проще, чем ардуино. Одно плохо — развесистые алгоритмы. Их удобнее последовательным алгоритмом выполнять, на процессоре.

AlexanderS

27.10.2015 23:52Тут штука заключается ещё в том, что для использования некоторых блоков нужна полноценная лицензия на САПР, которая стоит явно подороже 1к рублей.

Плюс еще надо все равно понимать схемотехнику хотя бы минимально. Блок обработки данных с АЦП, допустим, у вас есть. Допустим есть какая-то частота. А для АЦП её нужно понижать. Надо понимать что нужно ставить PLL/DCM и синтезированные такты по фазе подгонять. Да и вообще если часть схемы работает на исходных тактах, а другая на синтезированных, то нужно хорошо понимать как между ними переходить. Там вроде бы ничего сложного нет, но для новичка это неочевидно, а если непродумать переход, то можно схватить набор фееричных глюков и потом долго отлаживаться, т.к. подобные ошибки, как показывает практика, очень тяжело найти/понять.

В принципе, я согласен, при наличии протестированных многочисленных библиотек разработка сильно упрощается.

AlexanderS

27.10.2015 23:44Эээ, я тут одно не учёл… надо дать определение «потребительская электроника» =)

Я просто к тому — чем вас не устраивают ARM процессоры в этом сегменте? Тут я оговорюсь, что явно не влаею конкретно этой темой, но современные процессоры в топовых смартфонах разве не позволяют делать всё то, о чём вы написали выше?

rPman

28.10.2015 23:09Именно с видео — нет, доступ к сырому потоку данных практически отсутствует у всех, как класс.

Так же, обработка видео, один из самых затратных процессов, и именно FPGA ставят для первичной обработки видеоданных. Например wii remote, intel realsence camera — стоят именно fpga.

Отладочную плату за 1т.р. с 3к вентилей нет никакого смысла брать, поиграться можно и в эмуляторах, не так ли? Речь идет о полнофункциональном сопроцессоре (выше модель ссылку давал с 30к...80к вентилей), который можно использовать в неожиданных задачах и самое главное — чтобы это было доступно и популярно точно так же как сейчас доступны вычислительные ресурсы GPU с помощью технологий OpenCL (собственно я надеюсь что одним из вариантов использования FPGA будет тот же OpenCL или его функциональные аналоги, пусть компилятор думает об основных проблемах и сложностях).

AlexanderS

Ну и как в целом впечатление от нового софта?

Я прошлые три года ездил. В этот — не получилось. Народу что-то мало в этот раз совсем)

Когда первый раз демонстрировали виваду (года три назад вроде) с целью убедить инженеров в том, что всё нормально, что можно писать на Си, а потом будет нормальный синтез это не очень получилось, т.к. у докладчика схема не развелась, а потом САПР сглючила (сыровата видимо была) и… вообще я понял что работали мы на ISE — так и работать лучше дальше =)

Но фишка в том, что ISE 14.7 последняя в линейке, очевидно, что новые ПЛИСы поддерживаться будут как раз в САПРах типа Vivado и от этого никуда не денешся.

YuriPanchul

Вы несколько перепутали. Семинар ( bit.ly/mipsfpga_russia_2015_flier ) был не про Vivado от Xilinx, а про MIPSfpga от Imagination. Представители Xilinx Макро Групп сделали на ней презентацию про Vivado и HLS, но это не было основной темой презентации. Народу совсем не мало, а наоборот, очень много, так как у нас ограничения на посадочные места и платы, и мы его превысили — желающих раза в три больше, чем мы в начале планировали.

AlexanderS

Да нет, про MIPSfpga я понял. Vivado я просто к случаю вспомнил)