Прошли первые три занятия Школы Синтеза Цифровых Схем в 18 вузах России и Беларуси. На втором занятии пошла речь о D-триггерах и их описании в современном SystemVerilog, а не в стареющем Verilog-2001 и не в допотопном Verilog-95.

В курсе решили не разжевывать всякие старые вещи из курсов 1970-х, которым профессорам во всем мире бывает жалко выбрасывать, типа JK-триггеров или Т-триггеров. Так как инженер современного ASIC-а в 99% случаев использует D-триггеры, и только иногда D-защелки (для clock gating, экономии динамического энергопотребления чтобы в скажем телефоне не разряжалась быстро батарейка), то после комбинационной логики решили идти сразу к D-триггерам.

(Тут можно в порядке научпопа рассказать про SR-защелки, но даже это не обязательно — они никогда не появляются в отчете от Synopsys Design Compiler / IC Compiler и Cadence Genus / Innovus — тулов, которые используют проектировщики продвинутых чипов).

Короче, меньше жира — больше мускулов. Освободившееся в программе место будет использовано, чтобы рассказать про конвейерные дизайны и очереди FIFO, а также современные методы верификации чипов (функциональное покрытие, доказательства утверждений темпоральной логики) — тому, что требуется проектировщикам чипов и чему недостаточно хорошо учат даже в топовых американских вузах. У которых нужно учиться и потом делать лучше.

Что такое D-триггер?

D-триггер - это минимальный элемент состояния, он хранит 1 бит информации в течении 1 такта. Именно он делает электронику "умной", позволяет повторять вычисления, ждать события, организовывать конвейеры вычислений внутри микропроцессора, графического процессора, сетевого роутера. Вместе с объяснением функции D-триггера лектор Александр Силантьев из МИЭТ также описал временные задержки внутри такта и использование D-триггеров в элементарных последовательностных схемах - счетчиках и сдвиговых регистрах.

Иллюстрация работы простейшей последовательностной схемы — счетчика. Она показывает, что внутри такта результат работы комбинационной логики сначала неопределен, но через n-ное количество пикосекунд он устаканивается. Потом приходит фронт тактового сигнала и происходит запись в регистр — группу D-триггеров.

Я лет 10 назад сделал пост в Живом Журнале с картинкой счетчика выше из сумматора и D-триггеров, так мне после этого один русский программист из штата Колорадо двое суток доказывал, что счетчики проще строить на T-триггерах. Я ему говорил, что он правильно запомнил из своего детства 1970-х про T-триггеры (*), но сейчас в XXI веке разработчики строят счетчики из D-триггеров, потому что ситуация счетчика на T-триггерах, при которой сигнал данных используется как тактовый сигнал, плохо стыкуется с анализом тайминга в чипах на миллиарды транзисторов.

(*) Счетчик на устройстве похожем на T-триггер предлагал в 1978 году строить польский журнал "Горизонты техники для детей". Этот журнал переводили на русский и распостраняли в те времена в СССР. Триггер был назван в нем "загадочной схемой", и только через два номера читатели узнавали, что с его помощью можно считать импульсы:

На втором занятии Школы Синтеза тоже был пример с счетчиком. На языке описания аппаратуры SystemVerilog он выглядел так:

Потом на лекции Александр Силантьев из заленоградского МИЭТ объяснял весь синтаксис - зачем $clog2 и что значит "-: w_led":

Но знаете в чем самая удивительная вещь? Я выше написал что сейчас в 21 веке счетчики в 3-нанометровых ASIC-ах строятся на D-триггерах, но только вчера я обнаружил, что есть исключения подтверждающие правило (что вокруг сплошные D-триггеры и лишь очень иногда D-защелки). Оказывается T-триггеры и построенные на их основы ripple-counters не вымерли как мамонты, а иногда используются для экономии энергопотребления (но это нужно делать очень осторожно и не показывать студентам).

Такое инфо я нашел в книжке 2012 года The Art of Hardware Architecture: Design Methods and Techniques for Digital Circuits by Mohit Arora:

Но тут мне нужно остановиться, а то меня занесет на обсуждение C-элементов Мюллера (Muller C-element), "одалживание времени" в D-защелках (D-latch time borrowing) и прочую ересь, от которой молодым людям, изучающим основы RTL, желательно первые 10 лет карьеры держаться подальше. Иначе они научатся говорить, как ChatGPT, но ничего не будут уметь делать.

Приоритет - набить руку в мейнстримных последовательностных схемах с D-триггерами, затем в микроархитектуре с конвейерами и очередями, потом немного в динамическом энергопотреблении с clock gating.

Вот видео второй лекции на Школе Синтеза Цифровых Схем. Помимо D-триггеров, счетчиков и сдвиговых регистров там была еще презентация о симуляции от российской команды Delta Design, которые пишут симулятор верилога Simtera. Симулятор конечно сырой, но в этом есть особая прелесть - если 300-400 студентов Школы Синтеза забросают авторов Simtera претензиями, то Delta Design прокачает свой симулятор, а студенты прокачают свое понимание языка описания аппаратуры System Verilog.

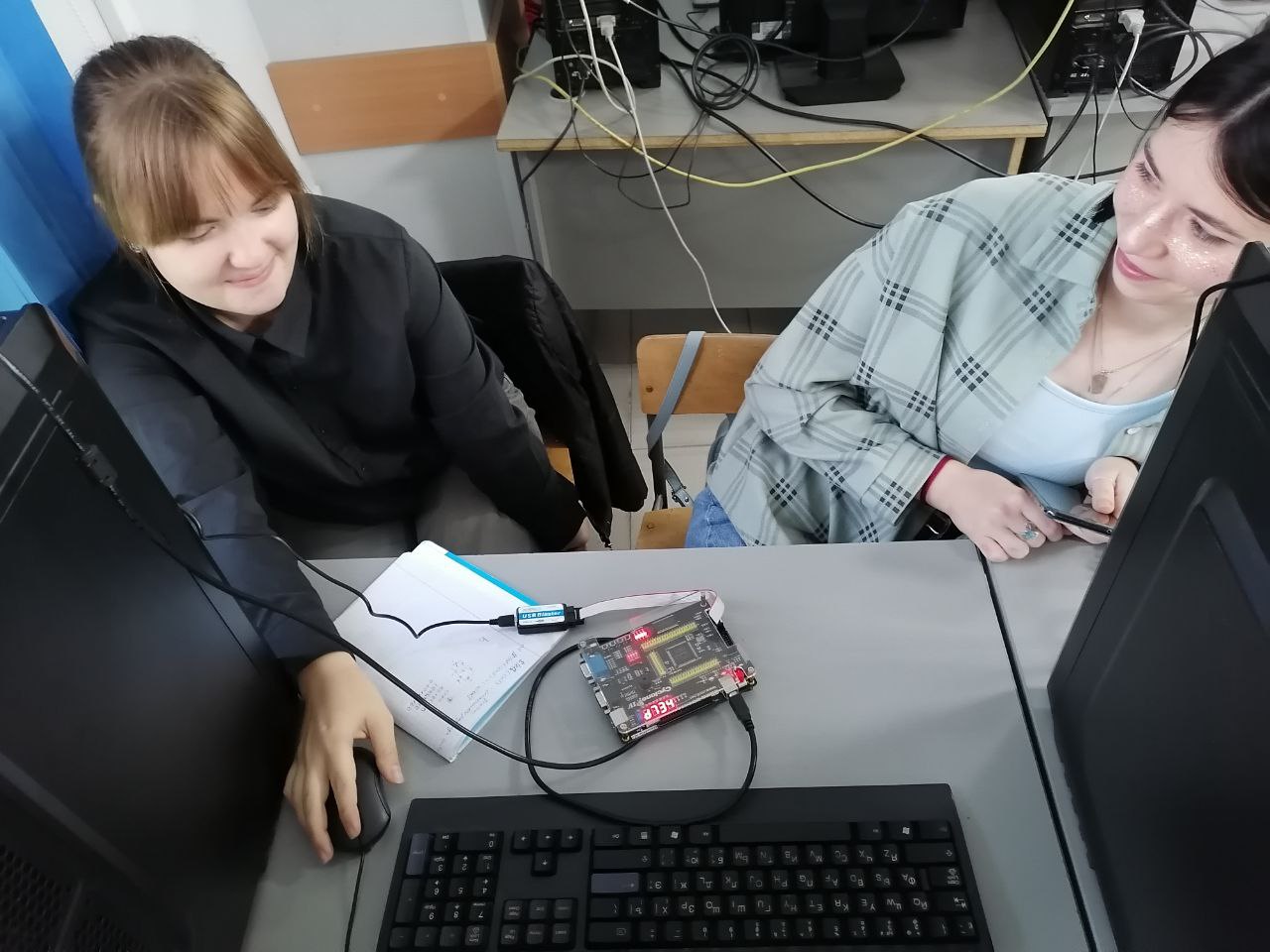

На Школу Синтеза еще можно записаться (но нужно прослушать три лекции по 3-4 часа и пообщаться на каналах, связанных со школой, например DigitalDesignSchool как работать с платами ПЛИС/FPGA). Также сообщите мне в приватных сообщениях, если вы хотите принять участие в портировании упражнений на FPGA платы. Сейчас набор начальных упражнений спортирован на около 30 плат от Intel FPGA, Xilinx, Gowin и Lattice.

semenyakinVS

Жаль что после 24 февраля 2022 года почти все публикации про программирование железяк в России стали восприниматься как потенциально опасные.

YuriPanchul Автор

Даже если российская электроника разовьется в ответ на санкции и военные действия, потом можно легко перековать мечь на орало. Вот вы можете увидеть, что в Америке требования на позициях на ракеты в Lockheed Martin по-сути совпадают с требованиями на позиции на айфоны в Apple:

iDoka

Дьявол кроется в мелочах: все эти "работы мечты" в SpaceX, Lockheed Martin, etc разбиваются об одно маленькое, но обязательное требование:

This position requires a goverment security clearance, you must be a US Citizen for considerationYuriPanchul Автор

Это к тезису ортогонально