Источником выделения тепла на кристалле ИМС являются три основных процесса: динамическая мощность, короткое замыкание и токи утечки. Обзор этих процессов будет проводиться на примере n-МОП технологии (хотя все описанное будет справедливо и для р -МОП).

1. Токи утечки в ИМС – этот процесс привлекает сегодня к себе самое пристальное внимание. Для техпроцесса в 250 мкм и больше токи утечки не сильно сказывались на общем энергопотреблении ИМС, однако с развитием технологий и переходом на более тонкий техпроцесс создания МОП структур, квантово-механические эффекты стали оказывать значимое влияние на токи утечки. Этот процесс более всего проявляет себя в ИМС, когда та находится в режиме ожидания, поскольку другие каналы утечки становятся незначительными. Для создания ИМС с низким энергопотреблением нужно рассмотреть более детально где и как происходят процессы утечки.

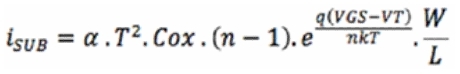

1.1 Обратный подзатворный ток: Эффект в области, находящейся под затвором, который возникает при условии VGS ? VT и VDS > 0 (для n-моп). В этой области при закрытом транзисторе нет напряжения для формирования проводящего канала, однако некоторые электроны могут получать достаточную энергию для движения от истока к стоку. Такой ток называется подзатворным. Приблизительное значения этого тока можно вычислить по формуле:

где:

isub = подзатворный ток;

a = константа, зависящая от процесса или технологии;

T = температура в Кельвинах;

Cox = емкость оксидного слоя;

n = другая константа, зависящая от процесса или технологии;

VGS = напряжение затвор исток;

k = постоянная Больцмана;

VT = напряжение перехода МОП ячейки из одного состояния в другое;

W = ширина канала;

L = длина канала;

q = заряд электрона.

Как видно из формулы, подзатворный ток возрастает с уменьшением длины канала, а с уменьшением напряжения VT транзистора и с ростом температуры возрастает экспоненциально. С уменьшением техпроцесса изготовления КМОП структур неизбежно уменьшается длина канала и пороговое напряжение VT для лучшей работы логики (высокое значение VT замедляет скорость переключения транзистора). Таким образом подзатворный ток возрастает с уменьшением техпроцесса и становится существенным для технологий в нанометровом диапазоне. Когда транзистор переводится в режим пониженного питающего напряжения, в нем наступает благоприятная среда для появления значительного подзатворного тока утечки, так как напряжение переключения транзистора уменьшается.

Рис. 1. Различные токи в структуре n-МОП транзистора.

2. Истощение потенциального барьера стоком. Когда на стоке устанавливается напряжение, оно порождает обедненную зону вокруг себя с некоторым потенциалом. При большом расстоянии между электродами МОП транзистора влияние поля стока на исток остается незначительным и, соответственно, в напряжение между истоком и каналом изменения не вносятся. Однако с уменьшением техпроцесса, расстояние между стоком и истоком сокращается. Как результат, исток попадает под влияние обедненной зоны и напряжения стока. Его потенциальный барьер уменьшаются, что приводит к тому, что поток электронов от истока к стоку возрастает, а напряжение на истоке падает.

1.3 Пробой. Данный эффект является крайним состоянием истощения потенциального барьера, когда напряжение на стоке достигает определенного значения, после которого поток электронов нарастает лавинообразно. Данный ток находится в прямой зависимости от VDS (напряжение между стоком и истоком). Это один из факторов, определяющий максимальное возможное напряжение на транзисторе. С уменьшением размеров МОП расстояние между стоком и истоком сокращается, и одно и тоже напряжение VDS на меньшем транзисторе будет создавать большее электрическое поле. Это поле может вызвать пробой, поэтому с уменьшением техпроцесса становится необходимым снижать рабочее напряжение на транзисторе.

1.4 Инициируемый затвором ток. Представим, что сток подключен к напряжению питания, а затвор к земле или к отрицательному питанию. Такая ситуация приведет к появлению плотного электрического поля в области стока под затвором, формированию там обедненной области и появлению эффекта межзонного туннелирования. Так как подложка подключена к земле, то неосновные носители заряда, собиравшиеся в этой обедненной области стока под действием поля начинают проникать на подложку. Такой ток называется инициируемый затвором. Данный ток сильно зависит от напряжения на стоке и от толщины изолятора затвора.

1.5 Туннельный ток через затвор. При уменьшении техпроцесса толщина оксидного изолятора под затвором также уменьшается. В настоящее время эта толщина составляет 1 – 2 нм. Высоколегированный канал и ультратонкий слой изоляции становятся причиной появления в области изоляции очень плотного электрического поля, измеряемого в МВ/см. При таком поле носители зарядов уже могут проходить через оксидный изолятор, создавая ток через затвора. Чем больше приложенное напряжение, тем больший ток будет проходить через изолятор. Данный ток не просто уходит через затвор, но и может сильно ослабить рабочий ток через сток. Это может привести к неправильной работе транзистора. Для борьбы с этим током утечки в транзисторах используется поликристаллический кремниевый затвор.

1.6 Обратный ток смещения. Между зоной диффузии n+ и подложкой появляется эффект паразитного диода. Такой эффект приводит к тому, что неосновные носители заряда начинают проникать со стока на подложку. Пары электрон-дырка, появляющиеся в обедненной области, также способствуют утечке на подложку. Данный ток напрямую связан с плотностью легирующей примеси и с увеличением плотности растет.

2. Короткое замыкание — другой процесс, на который затрачивается энергия в ИМС. Когда на входе схемы появляется изменение логического состояния, схема изменяет свое выходное состояние. В результате этого процесса МОП могут переходить из состояния “выкл” с состояние “вкл”, и в обратную сторону. Так как переходные процессы не происходят мгновенно, может появляется ситуация, при которой пара n-МОП и p-МОП меняют свое состояние и в какой-то момент ни один из них не находится в состоянии “выкл”. В этот период времени и происходит короткое замыкание. Данный ток не вызван зарядом какой-либо электрической емкости внутри кристалла, поэтому данное замыкание приводит к чистой потере энергии.

Рис. 2. Состояние короткого замыкания в МОП инверторе.

Представим себе ситуацию, когда на входе инвертора А изменяется состояние с низкого на высокий уровень. n-МОП транзистор (нижний) начнет открываться при достижении определенного напряжения Vn-моп на входе А, а в это время верхний p – МОП транзистор еще открыт. Он начнет закрываться когда напряжение на входе достигнет определенного высокого значения Vp-моп. Наступает ситуация, когда оба транзистора открыты и происходит короткое замыкание. Когда какой-либо транзистор закрывается замыкание прекращается. Такой же процесс происходит и при изменении входного сигнала с высокого на низкий уровень. Ток замыкания становится значительным если фронт/спад сигнала на входе продолжаются длительное время и если выход Z подключен к малому сопротивлению. Для борьбы с такими эффектом фронт и спад волны делают более быстрыми и увеличивают сопротивление, к которому подключен выход Z соответственно.

3. Динамическая мощность – это процесс рассеивания мощности на переключение состояний ячеек логики и соответственно состояния их входов и выходов. По этой причине процесс также называют энергией переключения. Когда ячейка изменяет свое логическое состояние с высокого на низкое или наоборот, множество внутренних емкостей (на пересечениях, соединениях проводников и пр.) заряжаются и разряжаются соответственно.

Данный процесс являлся самым значимым из всех процессов энергопотребления вплоть до технологий в 250 мкм. С уменьшением техпроцесса паразитные емкости уменьшились и энергия на переключение состояния тоже. Однако есть способы уменьшения динамической мощности с целью уменьшения общего энергопотребления ИМС.

Рис. 3. Переключающий ток с МОП схеме.

Рассмотрим элементарную схему из МОП элементов. Если все паразитные емкости в МОП ячейке представить в виде одного конденсатора С, то в момент переключения выхода с VDD на GRD произойдет потребление энергии равное CVDD2. Половина энергии накопится в емкости, другая половина теряется. Аналогично, когда выход переключается на VDD, происходит такой же процесс. Энергия на переключение напрямую зависит от напряжения VDD и частоты переключения. Как результат, способ уменьшения динамической мощности — снижение питающего напряжения. Однако это уменьшение приводит к тому, что ячейки становятся более медленными и за ними уменьшается и частота. Следовательно, на операции будет затрачиваться больше времени.

Общая формула динамической мощности:

P = f*C*V*V

где f – частота, С – емкость, V — напряжение. Заметим, что динамическая мощность не зависит от времени фронта или спада волны на входах и выходах.

Другой компонент динамической мощности это потери энергии на множественные «лишние» переключения, которые могут происходить в схеме из-за рассинхронизации задержки на участках схемы со множеством входов. Рассмотрим на примере схемы.

Рис. 4. Схема с 2-мя возможными лишними переключениями

Представим схему, в которой на два входа подается логическая “1” (питание VDD), а на входы A и B сигналы поступают с некоторой несинхронизированной задержкой. При работе логики из-за разницы в приходе сигналов выход Z на короткое время переключится в “1”. Такое событие называется кратковременный сбой.

Для борьбы с ним в схеме создаются условия максимально синхронного прихода сигналов. Если в схеме невозможно избавится от сбоев, то на выходе схемы ставят дополнительную логику для поглощения таких сбоев и блокирования его распространения, например, буферы для поглощения сбоев и балансировки таймингов.

Заключение

Анализируя различные причины потерь энергии на кристалле, можно сделать вывод, что получение низкого энергопотребления у ИМС с уменьшением техпроцесса становится все труднее и труднее. Мировые гиганты микроэлектроники уже сталкиваются с квантовыми эффектами, которые приводят к резкому росту потребления энергии ИМС. С уменьшением техпроцесса на сцену битвы выходят процессы, которые дают новые витки развития технологий изготовления кристаллов.

Комментарии (17)

Kopart

14.12.2015 18:57После разводки цифровой схемы уже есть вся информация для учета дополнительного потребления, связанного с несинхронностью прихода сигналов (лишние переключения). Соответственно можно посчитать эту добавку или ее минимизировать вставив (если возможно) задержки для «быстрых сигналов».

Может кто-то прокомментирует:

Для современных техпроцессов (65-130нм) эта добавка присутствует и ощутимая или успешно минимизируется правильной разводкой?Khort

15.12.2015 00:32Не понятно, о чем Вы спрашиваете. Если под «лишними переключениями» понимаются функциональные и логические состязания, то о них можно узнать на этапе моделирования нетлиста после синтеза, т.е. до топологии. Так же, есть особые приемы синтеза, позволяющие снизить процент неэффективных переключений (не приводящих к переключению выхода) в реализации функции, они описаны в учебниках по LowPower.

Что же касается искусственно вставляемых «задержек», то, насколько мне известно, их вставляют исключительно с целью выдержать setup и hold у сигналов, а так же для увеличения крутизны переходных характеристик (transition) в длинных и высоконагруженных линиях.

Kopart

15.12.2015 13:06После синтеза, но до честной топологии не известны фактические задержки распространения сигналов. У автора это приведено на Рис. 4. Схема с лишним переключением.

Не всегда можно избежать неэффективных переключений особыми приемами синтеза.

В данном примере на Рис.4 я вижу для синхронной схемы возможность задержать сигнал B на разводке, чтобы для него задержка распространения стала совпадать с сигналом А. Тогда переключение сигналов А и В на входе будет практически в один момент, что позволит уже на выходе Z не иметь лишнего переключения.Khort

15.12.2015 13:54На рисунке 4 ерунда нарисована. Сигнал D не должен инвертироваться относительно В, а задержки элементов первого яруса показаны нулевыми (хотя не должны, если уж мы говорим о задержках).

И наконец, для приведенной гистограммы сигналов C и D, на выходе глитч никак не получится.

Про избавление от глитчей с помощью задержек — это фантазия автора, на мой взгляд. Если реализация функции не монотонна на используемых наборах входных сигналов, и на некоторых входных наборах получаются состязания, то вставив задержки мы получим состязания на других наборах. Это как из пустого в порожнее переливать.

p.s. автор, кстати, забил на комментарии

Kopart

15.12.2015 14:18Если логические части в пути разбиты тригерами, то, кажется, что задержав на одном участке «быстрые» сигналы это не приведет к «переливанию из пустого в порожнее».

Я и не рассчитывал на комментарии автора по моему вопросу.

Просто после упомянутого рисунка автора задумался насколько такие глитчи (честные 2 переключения при подсчете) сказываются на потреблении.

Я сранвивал оценки потребления для одинаковой схемы и тестбенча, которые получаются при wireload-модели и в topographical-режиме. Но задумался после рисунка автора, что без полной разводки с точным вычислением задержки распространения сигналов не учесть дополнительное потребление связанное с глитчами. Ведь только тестбенч с честным «sdf» позволит посчитать в потреблении эти глитчи на сигналах.Khort

15.12.2015 14:45+1Смотрите, простой пример: Есть элемент AND с двумя входами. На первый вход подается перепад 0->1, а на второй вход с небольшой задержкой 1->0. На выходе возникнет глитч. Предположим, мы задержали первый вход — глитч пропал. А теперь представьте другую ситуацию: на второй вход приходит 0->1, а на первый вход (задержанный) приходит 1->0. Снова получился глитч на выходе. Это я называю переливанием из пустого в порожнее — как бы Вы задержку не вставили, найдется входной набор сигналов, приводящий к глитчу на выходе.

Что касается процента «ложных» переключений, то их в синхронных схемах это около 10-20% от общего числа переключений (можно нагуглить эту статистику, при желании).

Оценки потребления лучше делать, имея топологию, безотносительно глитчей. Общая закономерность: чем лучше тех. процесс, тем больше может получиться разница между оценкой потребления после синтеза, и после топологии. Это связано с ростом паразитных емкостей при улучшении проектных норм, которые можно экстрагировать только имея топологию.

RomanSansay

16.12.2015 20:14И да, все правильно, из-за рассинхронизации в любую сторону у нас будет возникать лишнее переключение.

Khort

17.12.2015 13:59Проблема глитча в том, что потребляет он только во время переключения. От задержек (времени прихода фронтов сигналов) может зависеть длительность глитча, но два его фронта (передний и задний) остаются. Следовательно, на потреблении схемы эти задержки не влияют.

Но зато влияет синтез, о чем я уже писал. В зависимости от реализации функции, в схеме может быть больше или меньше мест, где возможны глитчи. Да и просто можно сократить число переключений правильной реализацией. Пример:

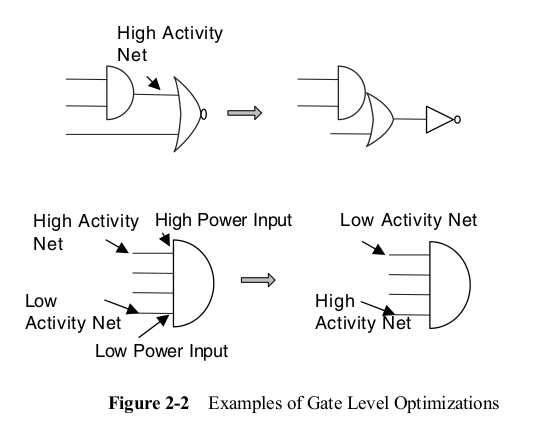

На верхнем рисунке мы избавляемся от цепи с высокой активностью, а на нижнем рисунке переподключаем активную цепь на вход с меньшим потреблением.

Kopart

17.12.2015 16:53От задержек (времени прихода фронтов сигналов) может зависеть длительность глитча, но два его фронта (передний и задний) остаются

Я предполагал решение, в котором если сигналы будут выравнены по времени прихода, то явного глитча не должно быть. В зависимости от рассинхронизации глитч сможет появится только частично, а соответствено дополнительное потребление на глитч будет не на полные переключения уровней в две стороны.

Но согласен, что сложно точно выровнять сигналы задержкой трассировки даже в одном тактовом домене. Но в теории — это бы избавило от гличта при любом сочетании значений сигналов.Khort

17.12.2015 17:45С точки зрения теории, не монотонные функции всегда приведут к состязаниям. А совпадение двух задержек это не теория, а скорее вероятность, причем равная нулю. Ведь есть куча причин, почему два сигнала выровнять нельзя: у пары сигналов есть свое время нарастания и спада, у топологии всех проводников есть своя паразитная емкость, и наконец — у приемных каскадов могут отличаться емкости затворов, мощности, и пороги срабатывания. При этом, все перечисленное плывет от температуры, питания, и зависит даже от расстояния от чипа до края пластины (ситуация, никак не контролируемая в САПР).

RomanSansay

16.12.2015 19:54Автор не забил, просто встает в 6 утра на работу и приезжает в 7 вечера. Отвечать сил не было вчера. Сегодня разобрал вопрос. Подтверждаю, на рисунке 4 нарисовано было с ошибкой. Рисунок заменил. Про методы избавления от гличей это отдельная тема и я там не особо владею информацией. В статье показал, на что расходуется энергия при работе кристалла.

Daffodil

18.12.2015 22:36Не могли бы добавить список литературы? — Читал пару лекций студентам на эту же тему, поэтому интересно какие источники вы использовали.

Khort

19.12.2015 11:06Тоже искал литературу, поскольку очень интересуюсь работой КМОП схем на подпороговых напряжениях. Нагуглил диссертацию из МИЭТ с аналогичным материалом (но подробнее изложенным) В конце есть список литературы, взгляните.

RomanSansay

19.12.2015 11:44Вот источник данного материала.

edn.com/design/integrated-circuit-design/4440402/Aspects-of-IC-power-dissipation

Статья свежая, перевел, отредактировал, обсудил на форуме.

На русском искал, но находил не то, что хотел.

Khort

19.12.2015 19:11Почему то ссылка не вставилась Вот, еще раз: www.miet.ru/upload/iblock/a94/Korshunov_dis.pdf

Khort

Спасибо, интересно!

А можно как то вывести зависимости энергоэффективности работы КМОП схемы, заключающейся в работе электрического тока за одно переключение этой схемы? Любопытно взглянуть на формулу.

Особенно интересует работа транзисторов при питании около или ниже порога. В литературе обычно указывают пик эффективности при питании чуть выше порога. Всегда было интересно, почему функция имеет минимум в этом месте, а не просто монотонно растет вверх при повышении напряжения питания.

p.s.

1. судя по формуле, ток утечки сток-исток растет с температурой не экспоненциально, а скорее в квадрате

2. в тексте есть опечатка — 250 мкм