В этом месяце IBM отметила 20-летний юбилей проекта разработки магниторезистивной памяти с произвольным доступом (MRAM). Изначально цель ставилась в управлении ячейкой при помощи электромагнитного поля. Сейчас проект трансформировался в разработку ячейки памяти с записью информации при помощи передачи момента вращения спина электроном. Такой тип памяти получил название STTMRAM (spin-transfertorqueMRAM).

Вместе с IBM над этим проектом работало много партнеров. Первым была компания Motorola. Затем — компании Infineon, TDK, Micron и другие. Благодаря участию специалистов из этих компаний проект удалось превратить из чисто теоретической концепции в реальную технологию. В течение нескольких лет ряд технических проблем мешал масштабировать память до высокой плотности. Но эту проблему все же удалось решить. И сейчас мы вместе с компанией Samsung подошли к завершающему этапу. Можно сказать, что разработка уже близка к коммерческому запуску. Сейчас основная задача решена, специалисты оптимизируют основную технологию и вспомогательные инструменты. Главным достижением работы с Samsung стал перевод структуры ячейки из горизонтальной в вертикальную.

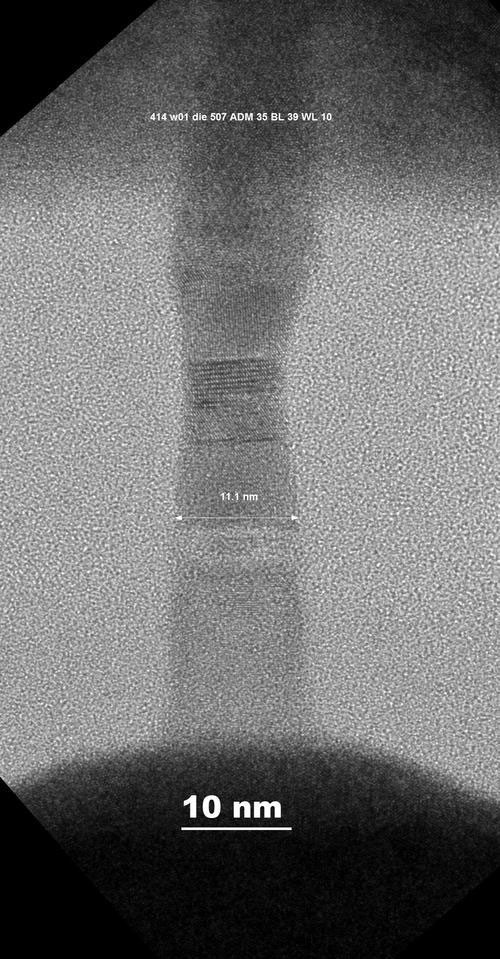

Сейчас уже готов тестовый образец памяти STTMRAM. Размер рабочей части ячейки составляет 11 нм. Соответственно, память такого типа будет производиться по 10-нм техпроцессу. Скорость доступа к ячейке составляет около 10 нс. По этому параметру новая память стоит рядом с DRAM, а не NAND-флэш. STTMRAM позиционируется как основная память с практически бесконечным ресурсом на перезапись.

Еще одним достоинством новинки является пониженное в сравнении с традиционными типами памяти энергопотребление — на запись требуется всего 7,5 мкА.

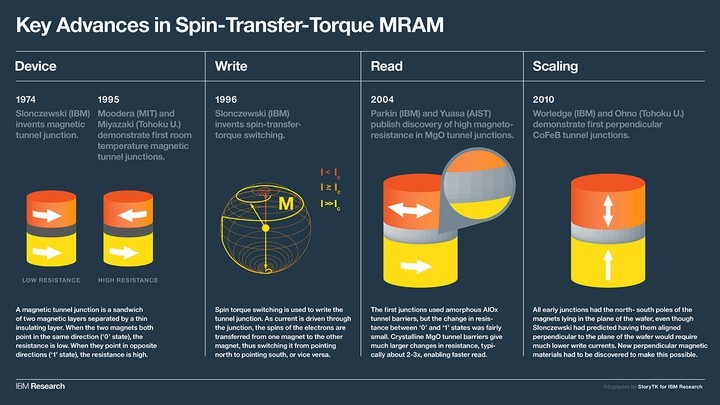

Технология переноса спинового момента (spin-torque-transfer-STT) или переключения с помощью переноса спина использует электроны с определенным состоянием спина (т.н. поляризованных электронов). При прохождении через ферромагнитный слой эти электроны изменяют собственный магнитный момент слоя и переориентируют его намагниченность… Такой способ позволяет уменьшить величину тока, которая нужна для записи данных в ячейку памяти. Потребление энергии при чтении и записи становится практически одинаковым. В случае традиционной MRAM технологии при увеличении плотности размещения ячеек памяти требуется увеличить и ток, необходимый для записи. Новая технология будет актуальна для техпроцесса 65 нм и меньше.

У магниторезистивной памяти примерно равное с SRAM быстродействие и такая же плотность ячеек. Но энергопотребление у MRAM гораздо ниже, чем у DRAM. Кроме того, как говорилось выше, эта память не деградирует с течением времени. В комплексе эти свойства магниторезистивной памяти делают ее действительно универсальной. Она может заменить сразу несколько типов памяти, включая SRAM, DRAM, EEPROM и Flash. Это приведет к унификации памяти на различных устройствах и в разных типах накопителей.

У магниторезистивной памяти примерно равное с SRAM быстродействие и такая же плотность ячеек. Но энергопотребление у MRAM гораздо ниже, чем у DRAM. Кроме того, как говорилось выше, эта память не деградирует с течением времени. В комплексе эти свойства магниторезистивной памяти делают ее действительно универсальной. Она может заменить сразу несколько типов памяти, включая SRAM, DRAM, EEPROM и Flash. Это приведет к унификации памяти на различных устройствах и в разных типах накопителей.«Благодаря своим преимуществам чип MRAM может заменить сочетание SRAM и flash-памяти в некоторых типах устройств, работающих с не слишком ресурсоемкими приложениями. Но наша долгосрочная цель — разработка решения на основе SpinTorqueMRAM для серверов IBM», — говорит доктор Дэниел Ворледж (Dr.DanielWorledge), один из руководителей проекта по разработке памяти нового типа в IBMResearch.

7 ноября этого года наша компания проводит симпозиум, посвященный 20-летию разработки SpinTorque MRAM. С деталями мероприятия можно ознакомиться по этой ссылке.

Комментарии (40)

ploop

05.08.2016 14:24Этот тип памяти подвержен обычному магнитному воздействию? Грубо говоря, «размагнитить» её можно?

(что защита делается элементарно — понимаю, интересует теоретически)

Pshir

08.08.2016 15:52Этот тип памяти подвержен обычному магнитному воздействию? Грубо говоря, «размагнитить» её можно?

Да, конечно

nkie

05.08.2016 14:39+1Можно ли примерную оценку, когда такая память появится на рынке, раз уже понятно что что все уже 100% работает?

Kenya-West

05.08.2016 15:03-1Физика — штука ненадежная, да.

scg

05.08.2016 21:27+1Вы почитайте книгу «Intel: взгляд изнутри», как Intel делал первые образцы своих микросхем. Какая там физика — чистое шаманство. Главное, чтобы с конвейера сходило что-то рабочее, а в физике процесса потом можно разобраться :)

scg

05.08.2016 15:06-4Можно. Лет через 20 она опять во что-нибудь переродится.

Из анонсированных супер-технологий в разных областях за последние лет 15 до рынка дошли только электронные чернила, да и те оказались не такие супер, как их нахваливали. А нет, еще OLED телевизоры нам обещали. Телевизоров мы так и не получили. но хоть смартфоны есть.

Torvald3d

05.08.2016 15:18еще OLED телевизоры нам обещали. Телевизоров мы так и не получили...

Как это нет, не далеко от меня продаются несколько OLED телевизоров 4k8k с полутрометровыми диагоналями за пару миллионов йен. На всякую «мелочь» не смотрел, наверняка тоже есть.

scg

05.08.2016 21:22Вы, наверное, это написали, чтобы рассказать, что я вру. Что технология органических светодиодов победно шагает по планете. Что невероятное соотношение качества картинки, контрастности, дешевизны и энергопотребления заставляет всех людей выкидывать их окон свои старые LCD телевизоры и стоять в очередях за OLED? По вашему, дела обстоят именно так? Вы знаете, первый тестовый образец OLED телевизора от Sony я видел как-раз 10 лет назад в ТЦ Европейский что у Киевского вокзала. Магазин, в котором он выставлялся уже успел обанкротится, но так и не дождался серийных образцов. А то, что где-то в Японии за кучу денег вам предлагают штучные изделия — это ни о чем не говорит.

Mulin

05.08.2016 15:37-1Неправда. В подобных областях срок коммерческой реализации зачастую менее 5 лет. Я прекрасно помню как скоро реализовывались в РЕАЛЬНЫЕ коммерческие образцы памяти, разработки самсунг. Тем более что это у объединение коммерческих структур.

vrmzar

05.08.2016 16:30+1Речь идёт как раз об чудо технологиях IBM, которые постоянно сообщают и революциях и прорывах, но что-то каждый раз не доходит дела до коммерческой реализации. Эта компания хорошо известна своими обещаниями, чего только стоит более чем 20-я история обещания 10, 100 и т.д. Ггц транзисторов, которые так и не пришли к коммерческому успеху.

Atreyer

05.08.2016 20:26+2Вовсю используется в сигнальных процессорах, например, ну то-есть внутри камня есть отдельные блоки обрабатывающие какие-то комбинации сигналов на своей волне, плюс такие блоки используют для синхронизации сигналов.

scg

05.08.2016 21:37+2Тут, в защиту IBM и их скоростных транзисторов я скажу, что они реально используются в производстве. Дело в том, что когда начинаешь соединять их последовательно вместе, то второй транзистор начнет переключаться только когда переключится первый. Частота падает. То, что современные процессоры работают на частотах 10-12-тилетней давности ничего не значит: у них резко выросла сложность. Всякие там, ассоциативные кеши и таблицы поиска знаете как увеличивают глубину схемы? Цепочки из десятков, если не сотен, транзисторов должны последовательно переключиться чтобы прошел один такт процессора.

scg

05.08.2016 21:15Какие 5 лет? В статье же ясно написано про 20-ти летний юбилей. А про чипы памяти на магнитных эффектах я слышал еще когда в институте учился. И тоже говорили, что скорость как у RAM и сохранность как у Flash. И первые образцы уже вроде как отгружались потребителям. И чё?

asd111

05.08.2016 22:23+1Intel обещали в этом году жёсткие диски с памятью Xpoint и показывали тестовые стенды где данная память примерно в 3-7 раз опережала по скорости современные nvme SSD, но согласно Intel Xpoint имеет значительно больший ресурс перезаписи чем SSD.

dzikar

05.08.2016 21:41Эт что выходит, можно будет вставить скажем такой памяти на терабайт и использовать её и в качестве жёсткого диска и оперативной памяти?

agriiii

06.08.2016 03:13-1Это выходит, что надо внимательно читать. Нет, ну если нужен компьютер-тормоз — можно и оперативку этим заменить, но пока — только как замена HDD, так как у SSD скорость доступа выше. Просто эта память должна решать проблемы со сроком хранения из-за перезаписи, но по скорости она не быстрее нынешних технологий, а значит и как оперативная — не желательна.

wormball

06.08.2016 13:20+1> у SSD скорость доступа выше

> Скорость доступа к ячейке составляет около 10 нс. По этому параметру новая память стоит рядом с DRAM, а не NAND-флэш.

Kheus

08.08.2016 15:52Можно пойти дальше и эволюционировать типичную архитектуру современного компьютера «Процессор-ОЗУ-НЖМД-Шина» до «Процессор-ОЗУ-Шина».

SEVENID

08.08.2016 15:52Это выходит, что можно создавать долговечные персистентные системы. Никаких внезапных выключений, никаких перезагрузок; появилось питание — машина снова онлайн и работает с того места, где остановилась. Память будет быстрее и требовать меньше энергии. Разница между оперативкой и жёсткими дисками начнёт стираться.

Ну и, в теории, становятся возможны такие финты ушами — запускаем машину, запускаем задачи, переводим в спящий режим, вытаскиваем оперативку, вставляем в другой компьютер, включаем, продолжаем с точки останова.

TargetSan

05.08.2016 22:23А какова «стойкость» этой памяти? Т.е. сколько в среднем живёт такая ячейка без самопроизвольного изменения состояния?

Вообще было бы очень приятно получить хорошую замену как минимум флэш-памяти и жёстким дискам. Первая дорогая и не слишком надёжная, вторые большие, медленные и боятся механических воздействий. Однако, несмотря на количество проектов неволатильной памяти, ни одна не вышла на широкий рынок. Максимум — нишевые решения. Так что я повременю радоваться пока не выпустят хоть одну небольшую серию потребительских железок.

Fenyx_dml

06.08.2016 00:18Полностью согласен! Самое интересное не сказали — по надежности как? И по цене за мегабайт. Вот это всё что меня интересует. Будет более надежная замена флеш за разумную цену — я двумя руками за!

M_org

12.08.2016 13:39-1Говорить о цене для первых коммерческих образцов, которые даже при заоблачном прайсе будут продаваться все равно дешевле себестоимости — странно :)

Fenyx_dml

14.08.2016 23:26+1Ничего подобного. Это работает при отсутствии альтернатив. Сейчас же рынок перегружен альтернативами и чтобы с ними конкурировать, цена нужна далеко не заоблачная, а очень даже конкурентная.

Vladimir_Feschenko

05.08.2016 22:23Как они делают такую (10 нм) литографию? Это же уже рентгеном надо «засвечивать»!

А по теме: реальный прорыв в технологиях хранения данных, высокая скорость доступа, высокая плотность записи, нет ограничений на количество перезаписей, энергонезависимое хранение… похоже, что век flash-SSD будет коротким (как у CD примерно).a5b

06.08.2016 05:34+3У них в данном случае не 10нм литография, у них 10 нм (11.1 нм) ширина одной структуры — https://hsto.org/files/a20/d78/730/a20d787304fd46d4a0f2be9d0b6fccfb.jpg. (Но тестовые структуры на "7 нм" техпроцесс в IBM уже делают — https://geektimes.ru/company/ibm/blog/253254/)

В настоящей "14 нм" литографии (на базе 193nm ArF excimer с иммерсией + Double patterning / triple patterning "on one or more critical layers.") нет элементов с размером в 14 нм (см слайд 16 из Rani Borkar, A Multi-Year Journey, 2014:

Minimum Feature Size(nm); 22 nm node / 14 nm node: Transistor Fin Pitch 60 / 42; Transistor Gate Pitch 90 / 70; Interconnect Pitch 80 / 52). Маркетинговые обозначения техпроцессов лишь указывают на удвоение максимальной плотности размещения элементов по сравнению с предыдущим техпроцессом (и название получается умножением предыдущего на 0.7). Реальные расстояния между элементами получаются больше чем обозначение техпроцесса, а некоторые размеры отдельных элементов — меньше, см. прогноз Table 1: ITRS 2013 Data for CMOS Technology “Nodes” из http://semiengineering.com/a-node-by-any-other-name/

высокая плотность записи

Плотность элементов они пока что не демонстрируют. В статье http://dx.doi.org/10.1109/LMAG.2016.2539256 https://www.researchgate.net/publication/297676487_Voltage_and_Size_Dependence_on_Write-Error-Rates_in_STT_MRAM_down_to_11_nm_Junction_Size лишь упомянут объем каждого массива из 38 изготовленных — 4 килобита, каждый массив имеет переход различного диаметра (от 50 нм до 11), но линейные размеры ячеек или всего массива не указаны:

… device size was examined in individual devices of 38 STT MRAM 4 kbit chips. Each of the 38 arrays had a different junction diameter.

Вероятно (с учетом 200 мм пластин в руках у Guohan Hu), для исследований использовалась не самые современные литографы...

IBM сообщила, что STT-MRAM может заменить встроенный флеш в логических техпроцессах ("28нм" и тоньше):

https://www.ibm.com/blogs/research/2016/07/ibm-celebrates-20-years-spin-torque-mram-scaling-11-nanometers/

… makes MRAM an ideal technology for always-on devices such as Internet of Things sensors, mobile devices and wearable electronics,… because MRAM uses standard transistors, ..it’s more easily embedded on the same chip as logic and other functions, compared to flash memory. Therefore many semiconductor foundries are considering replacing embedded flash with embedded Spin Torque MRAM at the 28-nm node and beyond.

PS: У Everspin есть MRAM на 256 мегабит, 40nm и 28nm. А флеш-память уже имеет плотность в 256 гигабит, на 3 порядка выше. Intel обещает 128 gbit в Optane (3D XPoint).

Vladimir_Feschenko

06.08.2016 11:20Спасибо! Но всё равно не понятно: структура 11 нм, чтобы получить подобное нужна засветка не длиннее чем 2.5 нм, это уже «конкретный рентген». Что они используют в качестве «фоторезиста»?

a5b

06.08.2016 20:08+1Сейчас используют 193 нм засветку, ширину элементов в 16-17 нм получают

http://www.embedded.com/print/4395587 Figure: TEM cross-section perpendicular to the fins and along metal gate.

Для одиночных отверстий/линий (расположенных далеко от других элементов) можно найти сочетание литографии и травлений, которые создадут нужный размер элемента.

Снизу на https://hsto.org/files/a20/d78/730/a20d787304fd46d4a0f2be9d0b6fccfb.jpg видна часть линии (WL или BL), её размер значительно больше 10 нм.

Кстати, для экспериментов вполне могли воспользоваться e-beam litho: "it can draw custom patterns (direct-write) with sub-10 nm resolution"

Vladimir_Feschenko

15.08.2016 17:22В таком случае (TEM) 16-17 nm — минимальное разрешение в особо непонятных условиях?

Они используют интерференцию при экспонировании фотошаблонов. Как они тогда фотошаблоны готовят? Однозначно! Это заговор! :)a5b

15.08.2016 19:24Как они тогда фотошаблоны готовят?

Фотошаблоны ныне имеют линейные размеры в 4 раза больше области засвета (максимальное поле засвета 26х33 мм, шаблоны — ~ 104 x 132 мм). Структуры на шаблонах должны иметь точность нанесения в нм близкую к разрешению литографа (~40-50 нм, см NXT — Technical Specifications). Пишут маски (шаблоны) с помощью лазеров или электронных пучков, в течение часов (десятков часов); затем (в нескольих итерациях) проверяют что записалось (микроскопом) и чинят (ионными пучками?).

В одном проекте десятки шаблонов (30-40, т.н. photomask set), из них 1/4-1/3 — для "критических слоёв", имеющих значительную стоимость (~100 тыс USD) максимальное разрешение (OPC+PSM) — т.е. для транзисторов (FEOL, несколько слоев: n-well, poly, sources, drains, nitride, contacts), и нескольких (1-4) нижних слоев металла (2 слоя на каждый металл: переходные отверстия между слоями и сам слой металла). При использовании Double patterning требуется две маски на слой. Для ряда критических слоев на 14 нм Интел уже использует triple patterning — по три маски на слой ("Bohr revealed that Intel is already using triple patterning for certain critical layers at 14nm").

Верхние металлы (BEOL) имеют более "толстые" техпроцессы с более простыми (дешевыми) масками.

Процесс изготовления простых (binary) масок, Roger Robbins "Photomask Making" 2007: http://www.utdallas.edu/~rar011300/LithographyProcess/PhotomaskMaking.pdf

Кто как, но Интел уже сделал для себя специальный кластер для подготовки шаблонов.

Вот статья про кластер для SMIC (Китай), Application of HPC in Mask Manufacturing — упрощенная схема подготовки шаблонов:

http://www.intel.com.tr/content/dam/www/public/us/en/documents/case-studies/xeon-e5-smic-paper.pdf Semiconductor Manufacturing International Corporation (SMIC) mask factory deploys high-performance computing solution to reduce costs and shorten the semiconductor manufacturing cycle. 2015

Собственные мощности: http://www.nextplatform.com/2015/11/26/intel-supercomputer-powers-moores-law-life-support/ Intel’s Own Supercomputer Powers Moore’s Law Life Support — November 26, 2015

Bohr says it takes a million CPU hours to design the photomasks to pattern the integrated circuits at scale currently. “That is the price we have to pay to pattern ten nanometer dimensions using 193 nanometer light.

Подробная статья про HPC внутри самого Intel для изготовления чипов

http://www.intel.com/content/dam/www/public/us/en/documents/white-papers/intel-it-hpc-silicon-design-paper.pdf High-Performance Computing For Silicon Design. 2013

• Four generations of HPC have successfully enabled Intel silicon tapeout, reducing tapeout time from 25 to less than 10 days.

… electronic design automation (EDA) tools. These tools apply extremely compute-intensive resolution enhancement techniques (RET) to update layout data for mask manufacturability and verify the data for compliance to mask manufacturing rules. A key EDA application within the tapeout stage is optical proximity correction (OPC), which makes it possible to create circuitry that contains components far smaller than the wavelength of light directed at the mask. OPC is a complex, compute-bound process. To accelerate the process, OPC applications take advantage of distributed parallel processing; tasks are divided into thousands of smaller jobs that run on large server clusters. It is critical to complete tapeout as fast as possible—and to minimize errors

HPC-1 45nm 2006-2008, HPC-2 32nm 2008-2010, HPC-3 22nm 2010-2012, HPC-4 14nm 2012-

The largest tapeout jobs, such as design rule check (DRC) workloads, require servers with a very large RAM capacity. We also use these large-memory servers as master servers for distributed OPC applications.

To illustrate the scale of the challenge, there may be as many as 40,000 OPC jobs executing concurrently on thousands of servers.Про HPC-5 для "10 нм" техпроцесса http://media15.connectedsocialmedia.com/intel/12/14135/Hyperscale_High_Performance_Computing_Silicon_Design.pdf декабрь 2015

HPC-5 Large-Memory Compute Server with 3 TB and up to 6 TB of RAM… 4 Rack Units… 1.49 kW consumed

EDA application license server… simultaneous license checkout of 1,000 keys per second from a single machine

We are currently developing the sixth-generation HPC (HPC-6), which is planned to support the tape-out of 7nm processors.

Они используют интерференцию при экспонировании фотошаблоновВысчитывают: https://en.wikipedia.org/wiki/Computational_lithography ftp://download.intel.com/pressroom/kits/research/computational_litho_poster.pdf

antonvn

Какова сейчас достигаемая плотность ячеек? Или, как на фото, 1 шт/образец?

QuickJoey

antonvn

Тестовый образец памяти объёмом 1 бит?

QuickJoey

вы путаете максимальный объём и плотность. это разные размерности. ваш вопрос тогда должен звучать примерно так: «какой максимальный объём (на одном чипе?) удалось получить?»

Alexsandr_SE

можно дальше 1 ячейки не ушли?

QuickJoey

если они в полушаге от коммерческого запуска, и говорят про техпроцесс, но наверное речь про бОльшие объёмы.

Alexsandr_SE

Или про специфические условия. Когда объем памяти может быть достаточно мал.

QuickJoey

про объём нам подсказывают

Alexsandr_SE

К примеру в районе 4 мегабайт на микросхеме будет все это заменять, но в специализированных устройствах.

a5b

Не указано. Много тестовых 4-кбит массивов с разными размерами ячеек.

http://dx.doi.org/10.1109/LMAG.2016.2539256 Dependence of Voltage and Size on Write Error Rates in Spin-Transfer Torque Magnetic Random-Access Memory — IEEE Magnetics Letters Volume:7, 2016 (указывалось иное название "Voltage and size dependence on write-error-rates in STT MRAM down to 11 nm junction size." в http://www.eetimes.com/document.asp?doc_id=1330058)

https://www.researchgate.net/publication/297676487_Voltage_and_Size_Dependence_on_Write-Error-Rates_in_STT_MRAM_down_to_11_nm_Junction_Size

voidptr0

Больше, чем 50 Мб на 25 кг.