Перевод статьи Кена ШирриффаПочти каждый смартфон использует процессор на основе чипа ARM1, представленного в 1985 году. Более десяти миллиардов ядер ARM было использовано в различных гаджетах, включая один из самых больших провалов Apple, карманный компьютер Newton, и один из самых оглушительных её успехов — iPhone. В этой статье мы рассмотрим ключевые части процессора ARM1: опишем общую структуру чипа, посмотрим на то, как устроены транзисторы и как они функционируют, взаимодействуя друг с другом для хранения и обработки данных, а также взглянем на визуальную симуляцию этого микропроцессора и узнаем, что происходит внутри ARM1 во время его работы.

Обзор микросхемы ARM1

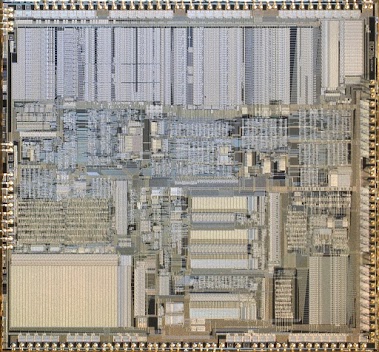

Микропроцессор ARM1 построен из функциональных блоков, каждый из которых имеет конкретное назначение. Регистры хранят данные, АЛУ выполняет простую арифметику, декодеры команд определяют, как выполнять каждую команду, и так далее. По сравнению с большинством процессоров, схема чипа ARM1 проста, и каждый функциональный блок хорошо отличим. Для сравнения, компоновка микросхем, таких как 6502 или Z-80, оптимизирована вручную, чтобы избежать пустых мест на подложке. В этих процессорах функциональные блоки склеиваются вместе, что затрудняет их понимание.

Основные компоненты чипа ARM1. Немаркированные контакты являются различными управляющими сигналами

Сейчас вы видите изображение, на котором показаны наиболее важные функциональные части микропроцессора ARM. Фактическая обработка происходит в нижней части чипа, которая относится к тракту данных. Чип обрабатывает одновременно 32 бита, поэтому его структура включает в себя 32 горизонтальных слоя: 31 бит сверху, 0 бит снизу. Несколько шин данных функционируют горизонтально для связи различных компонентов чипа. На изображении можно заметить большую секцию из двадцати пяти регистров. Счётчик команд (пятнадцатый регистр) находится слева от секции регистров, а нулевой регистр – справа. Девять из двадцати пяти регистров являются дополнительными, поскольку есть копии некоторых регистров для использования при обработке прерываний.

Все вычисления происходят в арифметико-логическом устройстве (АЛУ), которое находится справа от блока регистров. АЛУ выполняет 16 различных операций: сложение, сложение с переносом, вычитание, логическое сложение и так далее… АЛУ использует два 32-битных входа и выдаёт 32 бита на выходе. Более подробно об устройстве АЛУ можно прочитать здесь. Справа от АЛУ располагается 32-битное устройство сдвига. Этот большой компонент выполняет двоичную операцию циклического сдвига на входе. Слева находятся линии адреса, которые обеспечивают доступ к адресам в памяти через адресные контакты. Справа расположены линии данных, считывающие и записывающие значения данных в память.

Сверху расположен блок управления. Линии управления проведены вертикально от блока управления к схеме линий данных ниже. Эти сигналы выбирают регистры, сообщают АЛУ какую операцию выполнять и так далее. Схема декодирования команд обрабатывает каждую инструкцию и генерирует необходимые управляющие сигналы. Блок декодирования регистров обрабатывает биты выбора регистров в инструкции и генерирует управляющие сигналы для выбора необходимых регистров.

Контакты

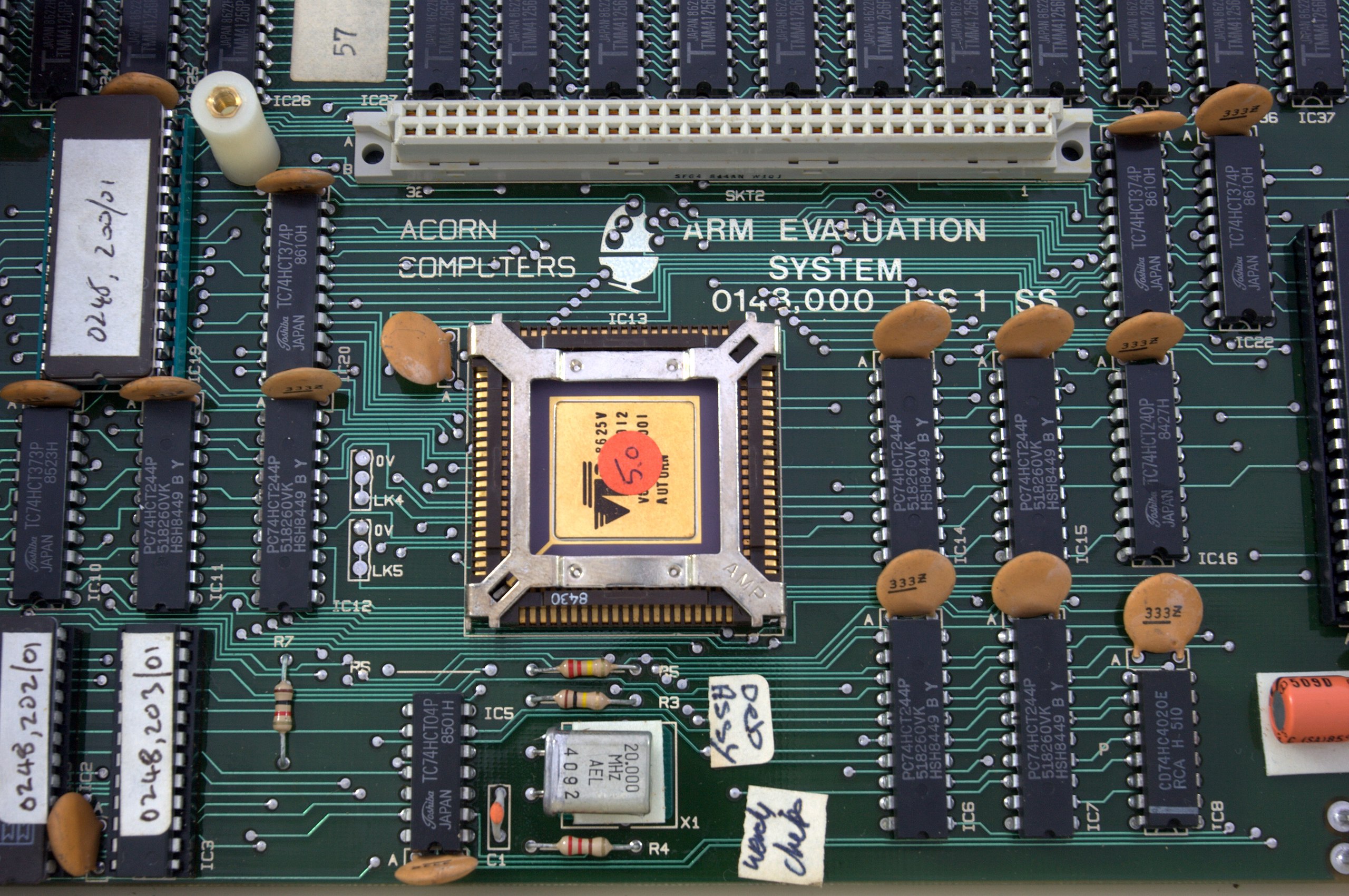

Квадраты вокруг внешней поверхности изображения – площадки, которые соединяют процессор с внешним миром. На фотографии ниже изображен восьмидесяти четырёх контактный корпус микропроцессора ARM1. Позолоченные контакты подключены к площадкам на кремниевой микросхеме внутри корпуса.

Процессор ARM1, установленный в Acorn ARM Evaluation System

Большинство площадок используется для линий адреса и данных, ведущих к памяти. Чип имеет 26 линий адреса, которые позволяют ему получать доступ к 64 мегабайтам памяти и 32 линии передачи данных, позволяющим ему считывать или записывать 32 бита за раз. Адресные линии находятся в левом нижнем углу, а линии данных – в правом. В симуляционной модели чипа можно увидеть, что сигналы поступают на линии адреса памяти, а по линиям данных считывается информация из памяти. В правой части симулятора показаны значения адреса и данных, представленные в шестнадцатеричном формате. Если вы знаете шестнадцатеричную систему счисления, вы можете легко сопоставить эти значения с состояниями контактов.

Каждый уголок чипа имеет линию питания (+) и линию заземления (-), обеспечивающих напряжение питания 5 вольт, которое необходимо для работы микросхемы. Различные сигналы управления расположены в верхней части чипа. В симуляторе легко заметить два тактовых сигнала, которые задают тактовый импульс. Частоты фазы 1 и фазы 2 чередуются, обеспечивая тактовый сигнал, необходимый для работы микросхемы. В нашей визуальной симуляции он становится активным примерно дважды в секунду, но реальный чип имеет частоту в 8 мегагерц, что более чем в миллион раз быстрее. Обратите внимание на имя производителя «ACORN» на чипе вместо 82 контакта.

Два тактирующих сигнала

История процессора ARM

Микропроцессор ARM1 был спроектирован в 1985 году инженерами Софи Уилсон и Стивом Фарбером из Acorn Computers. Изначально чип назывался Acorn RISC Machine и предназначался в качестве сопроцессора для компьютера BBC Micro.

Софи Уилсон и Стив Фарбер

Всего было произведено несколько сотен микропроцессоров ARM1, поэтому вы могли подумать, что он затерялся в недрах истории микропроцессоров 1980-х годов. Однако первый чип ARM1 привёл к удивительно успешной архитектуре ARM, количество чипов которой насчитывает более 50 миллиардов единиц. Что же произошло?

В начале 1980-х годов научные исследования предполагали, что если упростить набор инструкций для процессора, разработчики получат более высокую производительность — процессор будет простым, но более быстрым: компьютер с сокращённым набором команд или RISC (reduced instruction set computer). Исследовательские работы Стэнфорда и Беркли вдохновили разработчиков ARM на выбор архитектуры RISC. Кроме того, учитывая небольшую команду разработчиков Acorn, выбор RISC был практичным решением.

На компьютере с архитектурой RISC набор инструкций ограничивался наиболее часто используемыми, оптимизированными для высокой производительности и выполняемыми за один такт. Инструкции в свою очередь – это фиксированный размер, упрощающий логику декодирования команд. Для RISC-процессора требуется гораздо меньше схем для управления и декодирования команд, что позволяет разместить на чипе больше компонентов.

Простота конструкции RISC очевидна при сравнении микропроцессоров ARM1 и Intel 80386, выпущенных в том же году: ARM1 имел около двадцати пяти тысяч транзисторов, а 80386 – двухсот семидесяти пяти тысяч. Ниже изображены две фотографии процессоров в одинаковом масштабе. Площадь кристалла ARM1 составляет пятьдесят квадратных миллиметров, по сравнению со ста четырьмя квадратными миллиметрами у 386-го.

Из-за небольшого количества транзисторов процессор ARM1 имел небольшую мощность: около одной десятой ватта по сравнению с почти двумя ваттами у 386-го. Комбинация высокой производительности и низкого энергопотребления сделали более поздние версии микропроцессоров ARM очень популярными для встроенных систем. Компания Apple выбрала процессор ARM для своей злополучной карманной системы Newton. В 1990 году Acorn Computers, Apple и производитель чипов VLSI Technology создали компанию Advanced RISC Machines для продолжения разработки ARM.

С тех пор ARM стала самой популярной архитектурой с более чем пятьюдесятью миллиардами процессоров. Большинство мобильных устройств используют микропроцессор ARM. Например, процессор Apple A8 внутри iPhone 6 использует 64-битный ARMv8-А. Несмотря на свои скромные начинания, ARM1 попал в список IEEE Spectrum, состоящий из 25 чипов, которые потрясли мир и стали самыми влиятельными микропроцессорам по версии PC World за всё время.

Интересно, что компания ARM не производит чипы. Вместо этого интеллектуальная собственность ARM лицензируется для сотен различных компаний, которые выпускают чипы, используя архитектуру ARM.

Низкоуровневое строение чипа

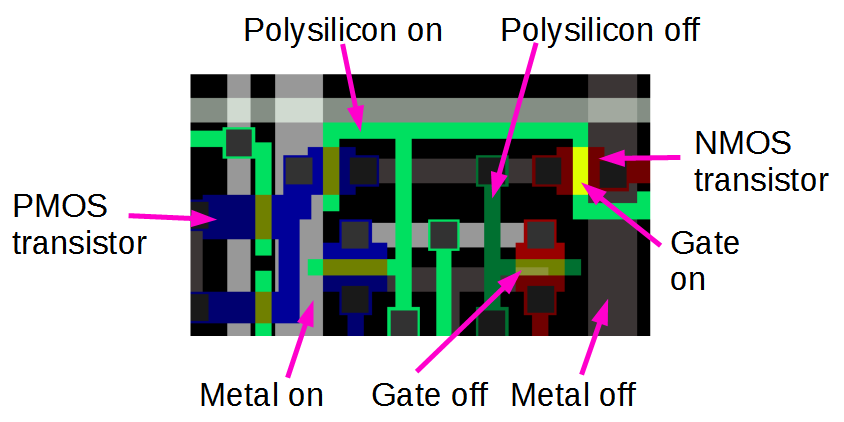

Микропроцессор ARM1 состоит из пяти слоёв. Если увеличить масштаб чипа в симуляционной модели, можно увидеть компоненты чипа, построенные из этих слоёв. Симуляционная модель использует для каждого слоя определённый цвет и обозначает линии активности своим цветом. Нижний слой состоит из кремния, на котором расположены транзисторы. Во время производства, области кремния модифицируются (легируются) с применением различных примесей. Кремний может быть легирован положительно, чтобы сформировать P-MOS-транзистор (синий) или отрицательно для N-MOS-транзистора (красный). Нелегированный кремний в основном представляет собой изолятор (черный).

Симулятор ARM1 представляет различные слои своими цветами

Линии из поликремния, обозначенные зелёным цветом, наносятся поверх кремния. Когда поликремний пересекает легированный кремний, он образует затвор транзистора (жёлтый). Наконец, два слоя металла, обозначенные серым цветом, расположены поверх поликремния и обеспечивают проводимость. Чёрные квадраты – контакты, которые образуют связи между различными слоями.

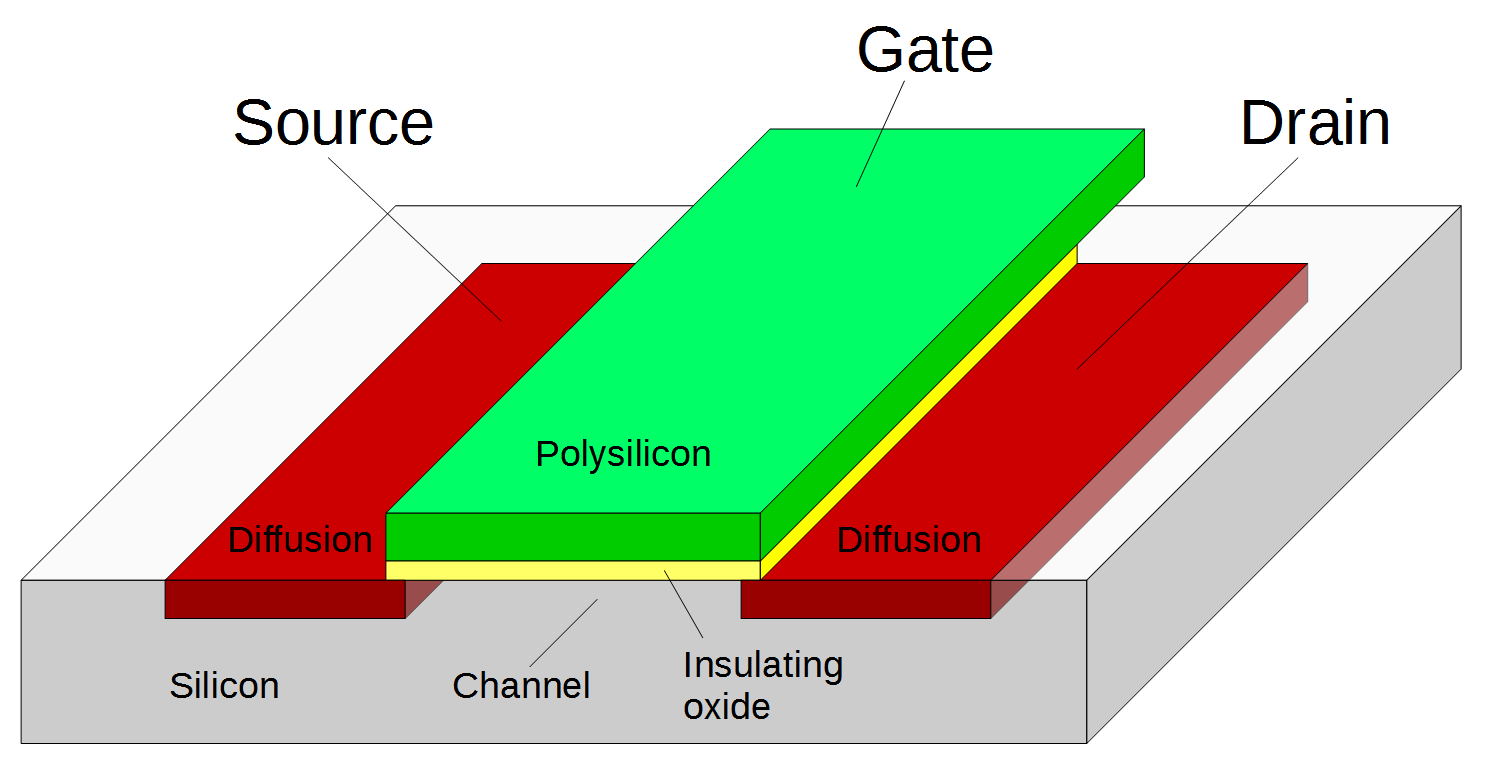

Для наших целей МОП-транзистор можно рассматривать в качестве переключателя, управляемого затворами. Когда он включён (закрыт), сток и исток в кремниевых областях соединены. Когда он отключён (открыт) сток и исток отсоединены.

Структура МОП-транзистора

Как и большинство современных процессоров, ARM1 был построен с использованием технологии КМОП, в которой используются два типа МОП-транзисторов: N-канальные и P-канальные. N-канальные МОП-транзисторы включены только тогда, когда на затвор подаётся сигнал высокого уровня и выход протянут к земле. P-канальные МОП-транзисторы включаются тогда, когда на затворе сигнал низкого уровня и на выход подаётся напряжения до пяти вольт.

Понятие регистрового файла

Файл регистра является ключевым компонентом ARM1, хранящим информацию внутри чипа. Регистровый файл состоит из двадцати пяти регистров, каждый из которых содержит тридцать два бита.

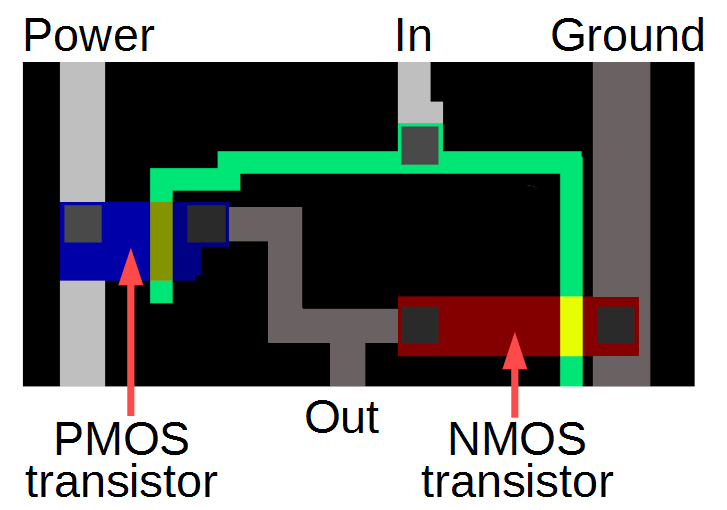

На изображении ниже показаны два транзистора, образующих инвертор. Если на вход поступает сигнал высокого уровня, N-MOS-транзистор (красный) включается, подключая выход к земле, чтобы на выходе иметь сигнал низкого уровня. Если же на вход поступает сигнал низкого уровня, то транзистор P-MOS (синий) включается, подключая линию питания к выходу, чтобы на выходе иметь сигнал высокого уровня. Таким образом, выход является противоположным входу, создавая инвертор.

Инвертор

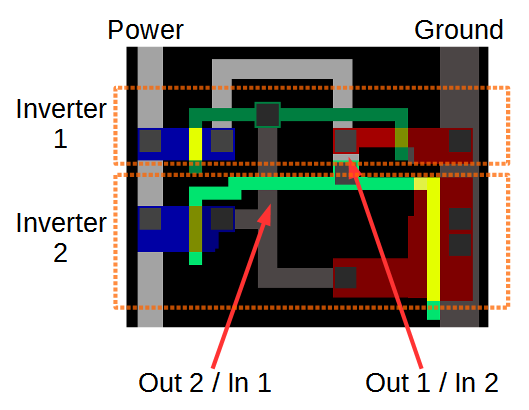

Объединение двух инверторов в петлю формируют простую схему хранения. Если на выходе первого инвертора 1, второй выдаёт 0, который поступает на вход первого инвертора и на его выходе создаётся 1 – цепь стабильна. Соответственно, схема будет оставаться в таком состоянии неопределённо долго, «запоминая» один бит, пока принудительно не будет переведена в другое состояние.

Два инвертора формируют регистр, который может хранить 1 бит

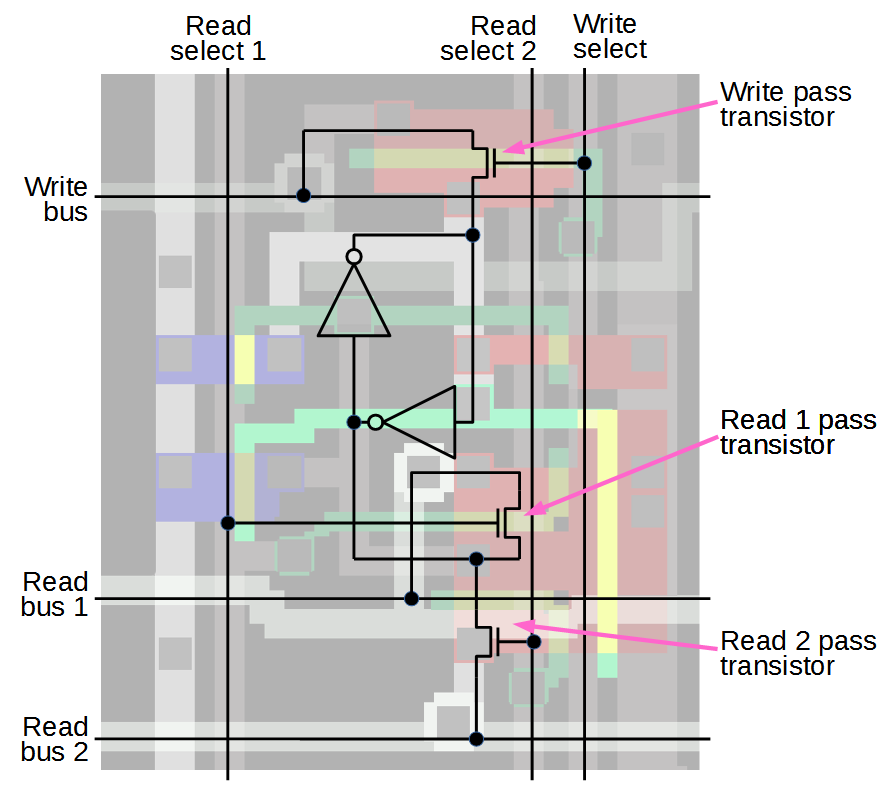

Чтобы создать такую схему в используемой ячейке регистра, добавляются линии чтения и записи, а также линии выбора для подключения ячейки к линиям шины. Когда линия записи активирована, обеспечивается контакт шины с инвертором, позволяя перезаписать текущее значение на новый бит. Аналогично транзисторы соединяют бит с шиной чтения при активации соответствующей линии выбора, позволяя считывать сохранённое значение.

Схема одного бита регистрового файла ARM1

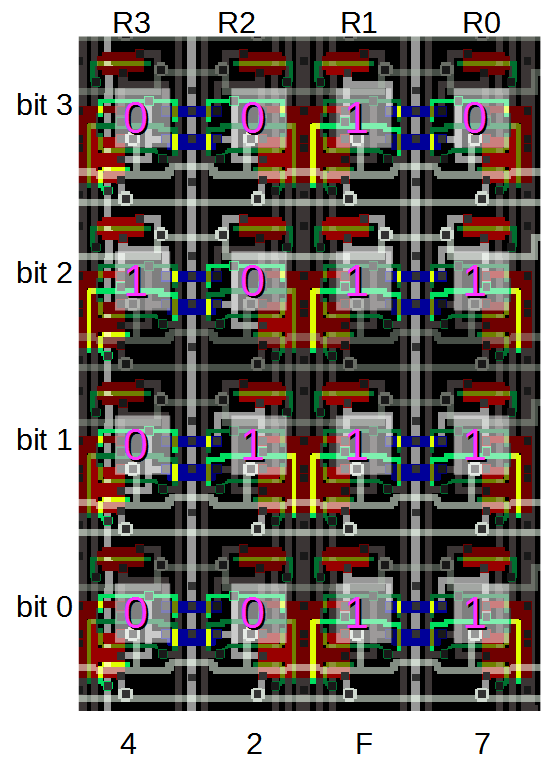

Чтобы создать регистровый файл, ячейка регистра должна повторяться 32 раза по вертикали для каждого бита, и 25 раз по горизонтали для формирования каждого регистра. Каждый регистр имеет три горизонтальные линии – линию записи и две линии чтения. Каждый регистр имеет три вертикальные линии управления – линию выбора записи и две линии выбора чтения. При активации желаемых линий управления могут быть прочитаны два регистра и может быть записан один регистр за раз. В симуляционной модели – вы можете увидеть активные вертикальные линии управления для выбора регистров и биты данных, перемещающихся на горизонтальных линиях шины.

Посмотрев на ячейку памяти в симуляторе, можно определить, какой инвертор включён и определить, равен ли бит 0 или 1. Если активен вход верхнего инвертора, то бит равен нулю. Если вход нижнего инвертора активен, то бит равен единице. Таким образом, внимательно присмотревшись, можно считывать значения регистров прямо из симулятора.

Изображение регистрового файла ARM1

Устройство быстрого сдвига

Устройство быстрого сдвига выполняет двоичные сдвиги и является ещё одним интересным компонентом ARM1. В большинстве инструкций используется устройство сдвига, позволяющее сдвигать двоичный аргумент вправо, влево или чередовать любые символы (от 0 до 31 бит). Во время запуска симулятора вы можете увидеть диагональные линии, перемещающиеся вправо и влево в быстром сдвиге.

На изображении ниже показана структура устройства сдвига. Биты сдвигаются вертикально относительно нулевого и тридцать первого бита. Выходные биты сдвигаются горизонтально между нулевым битом снизу и тридцать первым битом сверху. Диагональные линии показывают где вертикальные линии соединены с горизонтальными, генерируя сдвиг на выходе. Различные положения диагональной линии приводят к разным сдвигам. Верхняя диагональная линия сдвигает биты влево, а нижняя диагональная линия вправо. Во время сдвига обе диагонали активны; это может быть незаметно, но в сдвиговой части слова часть сдвигается вправо, а часто влево.

Структура устройства быстрого сдвига

Давайте увеличим область на устройстве сдвига, чтобы получше разглядеть его основные компоненты. Оно содержит 32 на 32 поперечные сечения транзисторов, каждый из которых соединяет одну вертикальную линию с одной горизонтальной. Транзисторные затворы соединены диагональными управляющими линиями; транзисторы вдоль активной диагонали соединяют соответствующие вертикальные и горизонтальные линии. Таким образом, активируя соответствующие диагонали, выходные линии подключаются к входным линиям, сдвинутым на определённое число бит. Поскольку входные линии микросхемы функционируют горизонтально, есть 32 соединения между входными линиями и соответствующими вертикальными битовыми линиями.

Детальное рассмотрение устройства быстрого сдвига ARM1

Заключение

Микропроцессор ARM1 привёл к удивительно успешной архитектуре процессора ARM, которая является сердцем вашего смартфона и вообще любого мобильного устройства. Простая архитектура RISC чипа ARM1 упрощает понимание схемы микропроцессора по сравнению со структурой 80386. Увлекательная визуальная симуляция микропроцессора ARM помогает понять что происходит у него внутри.

Наш видеоролик, созданный по этой статье: Внутри CPU: ARM1

Комментарии (14)

REPISOT

02.04.2018 08:10Не увидел в разделе «История» в чем же принципиальное отличие «Acorn (или Advanced) RISC Machine» от просто RISC.

Ну, был RISC. Инженеры Acorn решили: а давайте сделаем свой, с карточными играми и поэтессами.

kolu4iy

02.04.2018 14:04Насколько мне известно, изначально — RISC — это общее название, акроним от Reduced Instruction Set Computer. Т.е. принципиально только одно: команды маленькие, фиксированной длины, их просто декодировать и просто исполнить. В Стэнфорде, например, RISC процессоры звались MIPS, а у Acorn — ARM.

В то же время, CISC — это совершенно необязательно x86, просто он является самым известным представителем Complex Instruction Set Computer.

DASM

02.04.2018 15:26Смотрю я на систему команд АРМ и хочу спросить, а где она, собственно, простая?

sumanai

02.04.2018 15:39Планировалась так. И в одной из версий команды были переменного размера, потом вернули обратно, чтобы жизнь мёдом не казалась.

DASM

02.04.2018 15:51Вы thumb? Помню когда первый раз знакомился с АРМ поразило, что все команды условные. И все 32 бита. Расточительно. Потом thumb сделали и переключение режима на ходу (вроде джамп на нечетный адрес). А сейчас и вовсе Thumb2, который уже вполне разумно выглядит, но вот ничего рискового в нем не вижу

SergeyMax

02.04.2018 19:54ПростотаОграниченность состоит не в том, что нет команды деления (её, кстати, часто нет), а в том, что команды принимают только сильно ограниченный тип аргументов. То есть если это операция сложения, то она складывает только регистр с регистром, причём регистры не любые, а из определённого диапазона. В итоге то, что в x86 без особых раздумий выполняется одной инструкцией, в ARM распадается на три.

beeruser

02.04.2018 22:08+1Reduced это не simple. Так как команд мало, декодер получается простым (что видно на картинке).

В ARM1 — несколько десятков команд. Вообще весь процессор концептуально даже проще чем 8-битники. Это позволило создать его командой из нескольких человек.

Помню когда первый раз знакомился с АРМ поразило, что все команды условные. И все 32 бита. Расточительно.

Когда все условные и 32 бита — так проще. Сдвигатель, работающий в большинстве инструкций это опять же RISC подход.

Thumb2, который уже вполне разумно выглядит, но вот ничего рискового в нем не вижу

Это просто схема кодирования. Команды в Thumb2 и ARM одни и те же.

Где вы потеряли RISC-овость?

eatfears

02.04.2018 17:39Уточните, пожалуйста. Инструкции для выполнения попадают в процессор и в схему декодирования команд также по линиям передачи данных?

a5b

02.04.2018 18:51Да, через шину данных: https://en.wikichip.org/wiki/acorn/microarchitectures/arm1#Core

Данная статья — перевод

Reverse engineering the ARM1, ancestor of the iPhone's processor — http://www.righto.com/2015/12/reverse-engineering-arm1-ancestor-of.html, есть еще несколько заметок по тегу http://www.righto.com/search/label/arm

- Counting bits in hardware: reverse engineering the silicon in the ARM1 processor http://www.righto.com/2016/01/counting-bits-in-hardware-reverse.html

- More ARM1 processor reverse engineering: the priority encoder http://www.righto.com/2016/01/more-arm1-processor-reverse-engineering.html

- Conditional instructions in the ARM1 processor, reverse engineered http://www.righto.com/2016/01/conditional-instructions-in-arm1.html

- The ARM1 processor's flags, reverse engineered http://www.righto.com/2016/02/the-arm1-processors-flags-reverse.html

- Reverse engineering ARM1 instruction sequencing, compared with the Z-80 and 6502 http://www.righto.com/2016/02/reverse-engineering-arm1-instruction.html

- Reverse engineering the ARM1 processor's microinstructions http://www.righto.com/2016/02/reverse-engineering-arm1-processors.html

Также Dave Mugridge's series of posts http://daveshacks.blogspot.ru/search/label/arm:

- Inside the armv1 Register Bank http://daveshacks.blogspot.co.uk/2015/12/inside-armv1-register-bank.html

- Inside the armv1 Register Bank — register selection http://daveshacks.blogspot.co.uk/2015/12/inside-armv1-register-bank-register.html

- Inside the armv1 Read Bus http://daveshacks.blogspot.co.uk/2015/12/inside-armv1-read-bus.html

- Inside the armv1 — the Read Bus B, ALU Output Bus, and Address Bus http://daveshacks.blogspot.ru/2016/01/inside-armv1-read-bus-b-alu-output-bus.html

- Inside the ALU of the armv1 — the first ARM microprocessor http://daveshacks.blogspot.co.uk/2015/12/inside-alu-of-armv1-first-arm.html

- Inside the armv1 — instruction decoding and sequencing http://daveshacks.blogspot.ru/2016/01/inside-armv1-instruction-decoding-and.html

- Inside the armv1 — decoding barrel-shifter commands http://daveshacks.blogspot.ru/2016/01/inside-armv1-decoding-barrel-shifter.html

- Inside the arm1v — the ALU control logic http://daveshacks.blogspot.ru/2016/01/inside-arm1v-alu-control-logic.html

VBKesha

Отличная статья.

Тут вот ещё wiki.psxdev.ru/index.php/Main_Page хотели PS1 зареверсить, жалко что последние новости от 2016 года, тоже интересно могло бы получится.

1801BM1

PS1 люди «честно реверсят», вскрывают микросхемы, шлифуют, фотографируют, векторизуют, это очень много работы. А упомянутый в статье симулятор ARM1 сделан на базе готовых файлов фотошаблонов, полученных от самой компании ARM. Что, впрочем, не делает симулятор менее интересным.