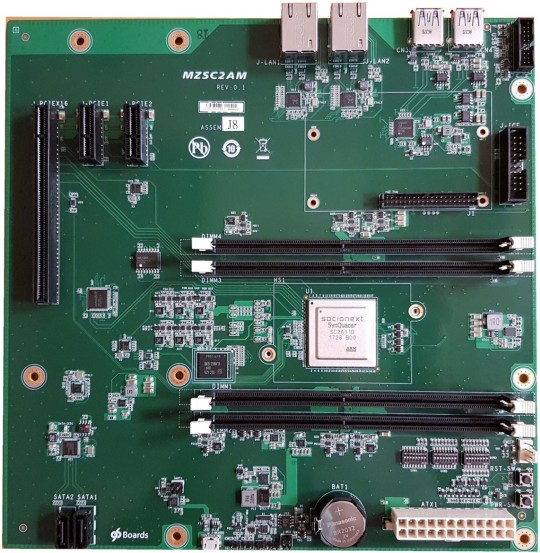

Материнcкая плата SynQuacer E-Series для 24-ядерного ARM-сервера на процессоре ARM Cortex A53 с 32 ГБ оперативной памяти, декабрь 2018 года

Много лет процессоры ARM с сокращённым набором команд (RISC) доминируют на рынке мобильных устройств. Но им так и не удалось пробиться в дата-центры, где по-прежнему властвуют Intel и AMD с набором инструкций x86. Периодически появляются отдельные экзотические решения, такие как 24-ядерный ARM-сервер на платформе Banana Pi, но серьёзных предложений пока нет. Точнее, не было до этой недели.

На этой неделе AWS запустила в облаке собственные 64-ядерные ARM-процессоры Graviton2 — это система-на-кристалле с ядром ARM Neoverse N1. Компания утверждает, что Graviton2 намного быстрее, чем ARM-процессоры предыдущего поколения в инстансах EC2 A1, а вот и первые независимые тесты.

Инфраструктурный бизнес — это сравнение цифр. По сути, клиентам дата-центра или облачного сервиса не важно, какая архитектура у процессоров. Их волнует соотношение цены и производительности. Если работа на ARM дешевле, чем на x86, то их и выберут.

До последнего времени нельзя было однозначно сказать о том, что вычисления на ARM будут выгоднее, чем на x86. Например, серверный 24-ядерный ARM Cortex A53 — это модель SocioNext SC2A11 стоимостью около $1000, которая могла поднять веб-сервер на Ubuntu, но по производительности сильно уступала процессором x86.

Однако потрясающая энергоэффективность процессоров ARM заставляет снова и снова присматриваться к ним. Например, SocioNext SC2A11 потребляет всего 5 Вт. А ведь на электроэнергию приходится почти 20% затрат дата-центра. Если эти чипы покажут пристойную производительность, тогда у x86 не останется шансов.

Первое пришествие ARM: инстансы EC2 A1

В конце 2018 года AWS представила инстансы EC2 А1 на собственных ARM-процессорах. Определённо, это было сигналом для индустрии о потенциальных изменениях на рынке, но результаты бенчмарков оказались неутешительными.

В таблице ниже показаны результаты стресс-тестирования инстансов EC2 A1 (ARM) и EC2 M5d.metal (x86). Для тестирования использовалась утилита

stress-ng:stress-ng --metrics-brief --cache 16 --icache 16 --matrix 16 --cpu 16 --memcpy 16 --qsort 16 --dentry 16 --timer 16 -t 1mКак видим, A1 проявили себя хуже во всех тестах, кроме кэша. По большинству других показателей ARM уступали очень сильно. Эта разница в производительности больше, чем разница в цене 46% между А1 и M5. Другими словами, инстансы на процессорах x86 по-прежнему оставались выгоднее по соотношению цена/производительность:

| Test | EC2 A1 | EC2 M5d.metal | Разница |

| cache | 1280 | 311 | 311,58% |

| icache | 18209 | 34368 | -47,02% |

| matrix | 77932 | 252190 | -69,10% |

| cpu | 9336 | 24077 | -61,22% |

| memcpy | 21085 | 111877 | -81,15% |

| qsort | 522 | 728 | -28,30% |

| dentry | 1389634 | 2770985 | -49.85% |

| timer | 4970125 | 15367075 | -67,66% |

Конечно, микробенчмарки не всегда показывают объективную картину. Важна разница в реальной производительности приложения. Но и здесь картина оказалась не лучше. Коллеги из Scylla сравнили инстансы a1.metal и m5.4xlarge с одинаковым количеством процессоров. В стандартном тесте на чтение базы данных NoSQL в конфигурации с одним узлом первая показала 102 000 операций чтения в секунду, а вторая 610 000. В обоих случаях все доступные процессоры используются на 100%. Это соответствует снижению производительности примерно в шесть раз, что не компенсируется более низкой ценой.

Кроме того, инстансы A1 работают только на EBS без поддержки быстрых устройств NVMe, как в других инстансах.

В общем, A1 стал шагом в новом направлении, но не оправдал надежд на ARM.

Второе пришествие ARM: инстансы EC2 M6

Всё изменилось на этой неделе, когда AWS представила новый класс ARM-серверов, а также ряд инстансов на новых процессорах Graviton2, в том числе M6g и M6gd.

Сравнение этих инстансов показывает уже совершенно другую картину. В некоторых тестах ARM проявляет себя лучше, а иногда намного лучше, чем x86.

Вот результаты выполнения той же команды стресс-тестирования:

| Test | EC2 M6g | EC2 M5d.metal | Разница |

| cache | 218 | 311 | -29,90% |

| icache | 45887 | 34368 | 33,52% |

| matrix | 453982 | 252190 | 80,02% |

| cpu | 14694 | 24077 | -38,97% |

| memcpy | 134711 | 111877 | 20,53% |

| qsort | 943 | 728 | 29,53% |

| dentry | 3088242 | 2770985 | 11,45% |

| timer | 55515663 | 15367075 | 261,26% |

Это уже совершенно другое дело: M6g в пять раз быстрее A1 при выполнении операций чтения из базы данных Scylla NoSQL, а в новых инстансах M6gd работают быстрые накопители NVMe.

Наступление ARM по всем фронтам

Процессор AWS Graviton2 — лишь один пример использования ARM в дата-центрах. Но сигналы поступают с разных сторон. Например, 15 ноября 2019 года американский стартап Nuvia привлёк $53 млн венчурного финансирования.

Стартап основали три ведущих инженера, которые занимались созданием процессоров в Apple и Google. Они обещают разработать процессоры для дата-центров, которые составят конкуренцию Intel и AMD.

По имеющейся информации, Nuvia спроектировала с нуля процессорное ядро, которое может быть построено «поверх» архитектуры ARM, но без получения лицензии ARM.

Всё это указывает на то, что ARM-процессоры готовы покорить серверный рынок. В конце концов, мы живём в эпоху пост-ПК. Годовые поставки x86 упали почти на 10% с пикового 2011 года, в то время как чипы RISC взлетели до 20 миллиардов. Сегодня 99% 32- и 64-разрядных процессоров в мире — это RISC.

Лауреаты премии Тьюринга Джон Хеннесси и Дэвид Паттерсон в феврале 2019 года опубликовали статью «Новый золотой век для компьютерной архитектуры». Вот что они пишут:

Рынок урегулировал спор RISC и CISC. Хотя CISC выиграл более поздние этапы эпохи ПК, но RISC выигрывает сейчас, когда наступила эпоха пост-ПК. Новых ISA на CISC не создавалось в течение десятилетий. К нашему удивлению, общее мнение по лучшим принципам ISA для процессоров общего назначения сегодня по-прежнему склоняется в пользу RISC, спустя 35 лет после его изобретения… В экосистемах с открытым исходным кодом искусно разработанные чипы убедительно продемонстрируют достижения и тем самым ускорят коммерческое внедрение. Философией процессоров общего назначения в этих чипах, скорее всего, будет RISC, который выдержал испытание временем. Ожидайте таких же стремительных инноваций, как и во время прошлого золотого века, но на этот раз с точки зрения стоимости, энергии и безопасности, а не только производительности.

«В следующем десятилетии произойдет кембрийский взрыв новых компьютерных архитектур, означающий захватывающие времена для компьютерных архитекторов в академических кругах и в индустрии», — такой вывод делают они в завершении статьи.

Комментарии (27)

xFFFF

07.12.2019 01:08RISC растёт большей частью за счет мобильных устройств. Точно такой же бурный рост CISC был в 2000-х. Сейчас такой рост не нужен, т.к. ОС неплохо работает на компах 5-8 летней давности. Мобилы восьмилетней давности были унылым говном, по сравнению с современными. Через несколько лет рынок насытится, и рост RISC тоже замедлится.

Cenzo

07.12.2019 03:00Рынок сильно сдвигается в сторону IoT сейчас, в системах безопасности, умных домах, IP камерах, итд — везде будут энергоэффективные и шустрые RISC (скорее всего ARM) процессоры, так что до пика рынка еще имхо далеко. Требования к CPU только растут из-за новых возможностей и обязательности шифрования для каждого девайса. Количество АРМов на квадратный метр дома только растёт, и рядом пара одиноких x86 в ноуте и компе.

xFFFF

07.12.2019 18:34IoT это все малопотребляющее и маломощное. Абсолютно другая ниша. В статье речь про сервера…

Cenzo

10.12.2019 00:28IoT тоже разные бывают и на месте не стоят, о том и речь была, что например в продвинутых IP камерах уже достаточно мощные процессоры, сжимают несколько потоков h265 на лету в разном разрешении, следят сами за зонами движения, сами отслеживают движущиеся объекты, скоро еще научат их распознавать образы и тд. Там для дополнительной мощности при малом потреблении применений море.

algotrader2013

07.12.2019 04:16Интересно, почему xeon phi стал мертвой веткой эволюции? Идея вставить 8 pcie карт в один сервер, и получить 480 полноценных x86 ядер (пусть и частично ограниченных в скорости операций с RAM и IO) и под 2000 потоков в 2011 году на первый взгляд кажется весьма заманчивой. Сразу возникает много идей, как это использовать, начиная от гипервизора, который тащит на себе 2000 сайтов-визиток и захудалых интернет магазинов на 100 покопателей в день в одной коробке, и заканчивая аналитическими СУБД, делающими в 2000 потоков аггрегации (что актуально для колоночных баз).

DrPass

07.12.2019 06:32+1Для того, чтобы потянуть 2000 сайтов-визиток на 200 тысяч юзеров суммарно, в общем-то, и не надо 480 полноценных х86 ядер. С этим и четыре полноценных ядра вполне себе справятся. Это надо для дата-майнинга, но рынок пока что невелик.

mistergrim

08.12.2019 13:45Xeon Phi в первую очередь предназначен для параллельных вычислений (собственно, изначально он и разрабатывался как видеокарта). Для серверов от него толку мало.

quwy

07.12.2019 06:57Ой, этой новости уже лет 15, если не 20. Все наступает, да не наступит никак.

ARM — это в первую очередь экономичность, а уже потом — производительность. А серверам чаще всего нужно ровно наоборот. Плюс для совсем тяжелых вычислений у x86 в рукаве есть козырь в виде GPGPU, с которым у альтернативных платформ все пока довольно грустно.

gnomeby

07.12.2019 17:23Ой, этой новости уже лет 15, если не 20. Все наступает, да не наступит никак.

Врядли 15 лет назад можно было ARM брать в аренду и разворачивать там сервера.

ARM — это в первую очередь экономичность, а уже потом — производительность.

Это определяется исключительно дизайном конкретной модели, у интела есть процессоры также соответствующие этому определению.

quwy

07.12.2019 17:44Врядли 15 лет назад можно было ARM брать в аренду и разворачивать там сервера.

Их и сейчас на первом попавшемся хостинге не взять. Некоторые, ориентированные на специфическую аудиторию, за неадекватные производительности деньги.

Это определяется исключительно дизайном конкретной модели, у интела есть процессоры также соответствующие этому определению.

У арма вся цель существования заключена в этом, в отличие от интела.

gnomeby

07.12.2019 19:17У арма вся цель существования заключена в этом, в отличие от интела.

Конкретно эти процессоры — нет.

RPG18

07.12.2019 22:59x86 в рукаве есть козырь в виде GPGPU

50/50. Потому что есть ARM со специализированными блоками, ARM с FPGA, ARM с CUDA ядрами.

ne_kotin

08.12.2019 21:30+1для совсем тяжелых вычислений у x86 в рукаве есть козырь в виде GPGPU, с которым у альтернативных платформ все пока довольно грустно

Да щас.

CUDA, TensorFlow, и NGC прекрасно работают на NVidia Jetson, кои суть есть ARM. И если мне не изменяет — там есть PCI-E, куда можно воткнуть видеокарту. Вот вам и GPGPU.

В пределе от ARM-ядра требуется только просасывать сеть и координировать выполнение полезной нагрузки на GPU, т.е. по сути нужна компактная плата с двумя разъемами — GbE и PCI-E для сетевизации и скейлинга видеокарт.

А старшие NVidia афаик умеют подобный цирк без участия центральных процессоров.

mynameco

Сейчас внутри почти всех CISC находятся ядра RISC, по сути борьба идет за то чтобы выкинуть прослойку преобразования x86 CISC в RISC, что должно дать выигрыш.

gnomeby

Не из-за этой прослойки x86 потребляет в разы больше электричества. Там много чего другого есть. Один предсказатель ветвлений чего стоит.

quwy

Можно подумать арму предсказатель ветвлений не нужен. Да и потребление декодера в легендах сильно преувеличено, термокарты процессоров есть в открытом доступе.

gnomeby

И где же они?

quwy

В гугле

fougasse

а кто управлять будет RISC ядрами?

proninyaroslav

Классический RISC сейчас только в MIPS да в RISC-V. ARM сейчас это больше CISC с элементами RISC, не более. В RISC нет инструкций переменной длины, инструкций, которые читают/записывают несколько регистров (push/pop), загрузка/сохранение с автоматическим приращением, арифметика/логика со сдвигами. Зато это всё есть в ARM.

Videoman

По вашему определению и PDP11 получается CISC. Это так?

mistergrim

PDP-11 всегда был CISC.

proninyaroslav

То что у PDP-11 ортогональная система команд, инструкции фиксированной длины, только регистровые операции и минимальный набор инструкций — делает его похожим на RISC. Но в то время ещё не было определения RISC, когда PDP-11 только вышел в продажу.

netch80

> только регистровые операции

По-моему, вы с прямым углом перепутали.

PDP-11 это где возможны операции типа ADD @6(R2), @-(R3).

Не может быть «похожим на RISC» процессор, у которого есть косвенный автодекрементный режим адресации (номер 5), косвенный индексный (номер 7) и т.п. — каждая такая особенность добавляет дополнительные сложности в декодер и такты в исполнение. И даже операции чтения-модификации-записи ячейки в памяти без прочих косвенных эффектов это уже уход от RISC.

«Похожий на RISC» это, например, базовые арифметические операции S/360, где второй источник ещё может быть в памяти, но первый источник и приёмник — только в регистре.

Ортогональность системы команд это как раз аргумент больше против RISC, чем за. RISC это простота одной команды, а не набора в целом.

netch80

Если вы про соответствие логике классической линии RISC, где все команды исполняются за фиксированное количество тактов, то да, современные RISC все вылазят за неё. И дело не только в перечисленных вами вещах: классический RISC даже не мог содержать операций с плавающей точкой или целочисленного деления — они все выносились в сопроцессоры или строились циклами с поддержкой этих действий. (Не рассматриваем, конечно, вариант занизить тактовую частоту так, чтобы АЛУ мог выполнять такое за 1 такт — это невыгодно для всего остального.)

Но с большей частью остального вы перегибаете.

В современном мире с его требованием out-of-order нет смысла требовать соответствия пятитактной схеме Berkeley/MIPS или её аналогу, зато появляется возможность делать более длинные и сложные действия, где они нужны (как с плавучкой).

Со сдвигами — нет никакой проблемы в операции типа a=b+(c shl d), если d — константа; это всего лишь несколько дополнительных вентилей на barrel shifter?е. Но даже если это не константа, то это всего лишь участие 4 регистров вместо 3 в списках зависимостей.

То же и с каким-нибудь LDP, STP, с автоинкрементом/автодекрементом.

Зато нет команд типа MOVES (x86), EDMK (S/360)…

ARM — RISC с элементами CISC, да. Но не наоборот, он продолжает сохранять простоту для управляющего устройства.