Если вы думали, что Intel'овская «банда» – это самые верные приверженцы закона Мура, то вы, наверное, не слыхали, как распространяется на эту тему Филип Вонг. Вонг, вице-президент корпоративных исследований Taiwan Semiconductor Manufacturing Corp (TSMC), на недавней конференции Hot Chips выступал с презентацией, в которой заявил, что закон Мура не только жив и здравствует, но, с достаточно разнообразным инструментарием технологических трюков, останется верным ещё не менее трёх десятилетий.

«Он не мёртв, — заявил он присутствовавшим на Hot Chips. – Он не замедляется, он даже не кашляет».

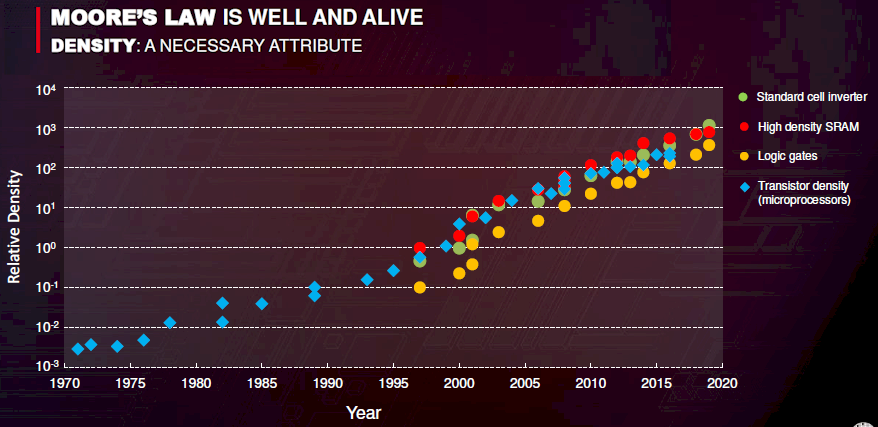

Послушать Вонга, так единственным необходимым для поддержания закона Мура действием будет улучшение плотности. И хотя он признаёт, что тактовая частота упёрлась в свой потолок, ознаменовав конец закона масштабирования Деннарда, он говорит, что именно плотность транзисторов позволит улучшить быстродействие и энергетическую эффективность.

Закон Мура жив

В конечном счёте, неважно, как будет достигнута большая плотность. Вонг считает, что главное, чтобы компании могли запихивать больше транзисторов в меньший объём с лучшей энергоэффективностью. В краткосрочной перспективе этого можно будет достичь старым, проверенным способом, а именно – улучшая технологию изготовления КМОП так, чтобы получалось производить транзисторы с меньшей длиной затвора.

TSMC уже освоила техпроцесс на 7 нм и движется к 5 нм. Вонг сказал, что экосистема разработки техпроцесса на 5 нм уже готова, и компания уже начала выпуск рисковых образцов – то есть, уже готовы и техпроцесс, и инструменты разработки, и сейчас производятся рабочие подложки. На последнем собрании акционеров TSMC сообщила, что планирует начать массовое производство чипов на 5 нм в первой половине 2020 года. Оказывается, что в планах компании есть уже и техпроцесс на 3 нм.

Но вся эта технология основывается на планарных [плоских] чипах, и Вонг признаёт, что этот подход в итоге перестанет масштабироваться. «Если идти по пути двумерного увеличения, то мы уже пришли к нескольким сотням атомов, и скоро у нас все атомы кончатся», — пояснил он.

Но это не означает конец увеличения плотности. Он отметил, что некоторые инновации в полупроводниковой промышленности поддерживали восходящий график плотности даже по окончанию масштабирования Деннарда. В частности, появились технология напряжённого кремния и high-k диэлектрика, а за ними последовала FInFet (Fin Field Effector Transistor), технология трёхмерных структур. Сейчас для выхода за пределы 7 нм исследуют технологию DTCO (Design Technology Co-Optimization).

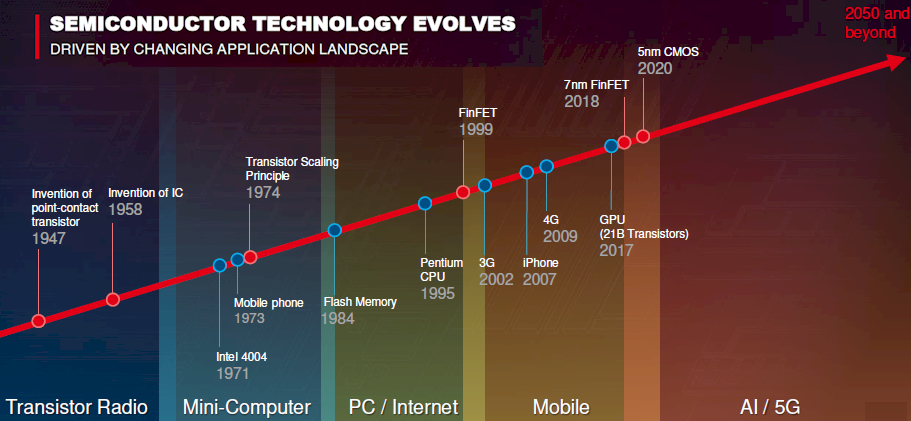

Все эти инновации произошли потому, что нужно было разрабатывать новые вычислительные платформы, требовавшие более быстрого и энергоэффективного железа. Эта эволюция породила миникомпьютеры в 1970-х, ПК в 1980-х, интернет в 1990-х, а сегодня – мобильные устройства. Каждая ступень требовала увеличения плотности через улучшение полупроводникового производства. Вонг считает, что следующие запросы поступят от искусственного интеллекта и 5G.

Эволюция полупроводниковой технологии

Какие же инновации потребуются для того, чтобы вечеринка закона Мура не прекращалась?

В краткосрочной перспективе общую вычислительную плотность и плотность памяти будет увеличивать использование чиплетов, используемых для создания многочиповых корпусов 2,5D структур, даже если сами чипы не будут становиться плотнее. Вонг сказал, что этот процесс уже делает конкретный техпроцесс отдельного чиплета менее важным параметром, чем возможность интеграции этих компонентов в одном корпусе.

У TSMC есть собственный вариант корпуса 2,5D с технологией Chip-on-Wafer-on-Substrate (CoWoS) (с этой технологией конкурирует Embedded Multi-die Interconnect Bridge, или EMIB, от Intel). CoWoS позволяет создавать многочиповые корпуса, закрепляя чиплеты и подходящую память на интерпозере, и соединять их при помощи вертикальных контактов TSV. Самой интересной реализацией CoWoS считается ускоритель GPU Tesla V100 от Nvidia, в котором GV100 GPU упакован с памятью высокой пропускной способности (HBM). Интеграцией большего количества чиплетов занимаются Intel, AMD и Xilinx.

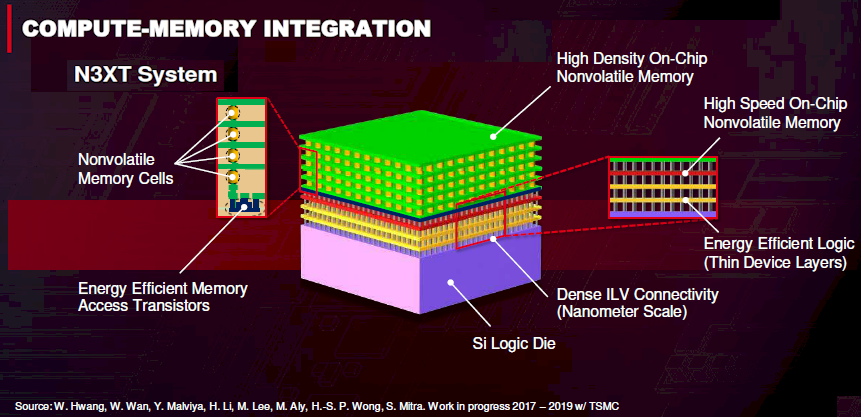

Но возможности 2,5D по увеличению плотности не безграничны. Более масштабируемое решение потребует реально трёхмерных технологий размещения транзисторов. Для этого, по мнению Вонга, лучше всего подходит монолитная трёхмерная технология N3XT на основе новых материалов и плотной интеграции памяти с логикой. N3XT, «наноинженерная технология вычислительных систем», обсуждается в академических кругах с 2015 года, но теперь, когда такие компании, как TSMC, начали принимать её всерьёз, у неё появился неплохой шанс на коммерциализацию.

Вонг продемонстрировал слайды со схемами того, как может выглядеть подобное устройство. Оно состоит из слоёв энергоэффективной логики (жёлтые), высокоскоростной памяти (красные) и энергонезависимой памяти высокой вместимости (зелёные), расположенных попеременно друг над другом. И всё это сидит на обычном кремниевом логическом кристалле (пурпурный).

Система N3XT

Главное тут – объединить различные слои посредством ILV, Inter-Layer-Via (межслойным вертикальным доступом). В отличие от TSV микрометрового масштаба, ILV можно формировать на нанометровых масштабах. И хотя это чрезвычайно важная часть технологии N3XT, Вонг мало что смог о ней рассказать. Очевидно, однако, что TSMC плотно работает над ней и зарегистрировала уже несколько связанных с ней патентов.

В трёхмерных чипах перемежение памяти и логики очень важно, поскольку позволяет уменьшать расстояние между ними, обеспечивая тем самым высокую пропускную способность и низкую задержку передачи информации, что будет необходимым для таких областей применения, как ИИ и 5G. В КМОП нельзя перемежать память и логику, поскольку для травления логических транзисторов требуется температура порядка 1000 градусов Цельсия, которая уничтожила бы соседние слои на производстве. Тут требуется что-то, что можно изготавливать при температурах порядка 400 градусов.

Оказывается, что в последние несколько лет исследователи изучали новые материалы, вроде бы подходящие для производства высокоскоростных транзисторов при относительно низких температурах. В отличие от кремниевых материалов, используемых на производстве сегодня, там используют монослои дихалькогенидных переходных металлов (TMD) на основе таких элементов, как молибден, вольфрам и селен.

Материалы TMD демонстрируют высокую мобильность носителей заряда – электроны передвигаются по ним с большой лёгкостью – при узких каналах. Что удобно, именно такие характеристики нужны для создания транзисторов размером менее 2-3 нм. Вонг сказал, что в лаборатории TSMC испытывают экспериментальные TMD-подложки на основе дисульфида вольфрама.

Ещё один кандидат на наноматериалы – углеродные нанотрубки. Вонг сказал, что были произведены их экспериментальные варианты, показавшие хорошее поведение материала в качестве полупроводника. Уже были собраны рабочие прототипы логики и SRAM на основе углеродных нанотрубок, включая и вариант RISC-V от исследователей из MIT.

Что касается памяти, то, по мнению Вонга, наиболее вероятными кандидатами для трёхмерной интеграции будут: SST-MRAM (spin-transfer torque magnetoresistive random access memory, магниторезистивная оперативная память, которая использует для записи перенос спинового момента электрона); память с изменением фазового состояния PCM; резистивная память с произвольным доступом ReRAM; память на базе программируемой металлизации ячейки CBRAM; сегнетоэлектрическая оперативная память FERAM. Всё это энергонезависимая память со случайным доступом, которой не требуется операция стирания ячейки перед записью в неё новой информации. Некоторые варианты уже есть на рынке — Everspin MRAM, Samsung MRAM, Crossbar ReRAM и Intel 3D XPoint (которая, по мнению большинства, представляет собой вариант PCM).

Новые типы памяти

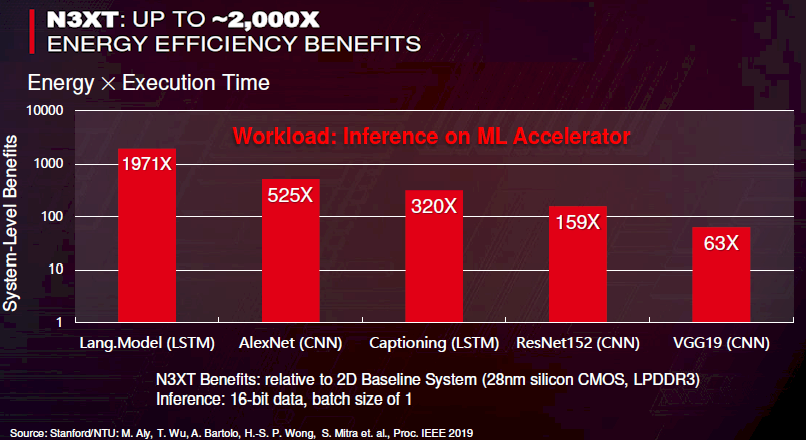

Исследователи проводили симуляции быстродействия устройств N3XT и сравнивали их с традиционными двумерными чипами с примерно такой же ёмкостью логики и памяти. Согласно их исследованиям, где использовались различные методы измерения скорости работы алгоритмов машинного обучения, устройства технологии N3XT оказались в 63-1971 раз эффективнее двумерных.

Преимущество N3XT перед двумерными системами

Звучит многообещающе. Но Вонг не стал распространяться, как именно эти технологии в ближайшие 30 лет смогут поддерживать скорость улучшения технологий, необходимую для закона Мура. К примеру, переход на новые наноматериалы даст нам однократный прирост плотности транзисторов по отношению к двумерным компонентам. Но и там в итоге мы столкнёмся с атомными ограничениями.

Теоретически, если можно будет удваивать высоту трёхмерных устройств каждые 18 месяцев, можно будет достичь увеличения плотности на квадрат площади поверхности. Конечно, для мобильных и встраиваемых устройств такой подход быстро станет слишком громоздким, да и чипы для компьютеров в дата-центров после семи-восьми поколений упрутся в 4-метровый потолок.

Чтобы всё продолжало работать несколько десятилетий, и плотность продолжала укладываться в кривую закона Мура, необходимо будет разработать другие технические инновации, не упомянутые Вонгом. Но если вы производите чипы, как компания TSMC, вам придётся принять на веру, что исследователи постоянно будут подкидывать вам новые кандидаты на технологии, которым для выхода на рынок понадобятся всего лишь запросы от новых, более требовательных задач. А если вспомнить историю, то такие задачи обязательно появятся.

Victor_koly

Это точно — упрутся. Даже если сначала создадут чип высотой 80 мкм, «удваивать высоту» 8 раз даст 20.5 мм — явно больше разумного размера кристалла. Тогда придется думать до 3-мерных структур охлаждения внутри кристалла.

Squoworode

Сделают его пористым и приделают штуцеры для жидкости

Tufed

Зато его теперь можно будет охлаждать сбоку. С четырех боковых граней! Это же гениально!

A1exXx

Да какие там 20 мм. как охлаждать даже пару десятков слоёв? корпус будет со встроенным водяным охлаждением?

PashaWNN

Ну и скорость прохождения сигнала, конечно же. Теоретически можно сделать «кубик» с равными гранями, равными стороне сегодняшних «квадратов», но не более.

Victor_koly

Размер чипа — это ведь меньше, чем «размер корпуса» — 37.5mm x 37.5mm у i9-9900K?

И я подозреваю, что при любой топографии «кубического» чипа путь тока между противоположными вершинами выйдет не намного меньше суммы 3 ребер.

amartology