Если вы изучили начала цифровой схемотехники и компьютерной архитектуры по книжке Харрис & Харрис и потом вознамерились пойти собеседоваться на позицию проектировщика микросхем в Apple или NVidia, то вы интервью не пройдете. Посколько вы наверняка получите вопрос про реализацию в хардвере очередей FIFO, а это в Харрис & Харрис не описано.

Хуже того, даже если вы возьмете книжку Digital Design by William Dally & Curtis Harting, которую используют для обучения студентов в Стенфорде, и прочтете ее от корки до корки, то у вас все равно мало шансов, потому что, хотя FIFO там и есть, но в очень базисной форме, а контроль потока данных заканчивается на скид-буферах.

А что же хотят электронные компании?

Даже Dally & Harting - это уровень ~2000-года, а в современной электронной индустрии юный инженер должен владеть кучей трюков, в которые входят не только разнообразные, в том числе извращенные, виды FIFO (на D-триггерах и на SRAM, с однопортовой SRAM или двухпортовой, на одном тактовом сигнале или двух, с несколькими головами или несколькими хвостами, хранящие данные в памяти в виде связанного списка, разделяющие общую память для нескольких FIFO, FIFO с возможностью undo push итд) - но и комбинации этих FIFO с кредитными счетчиками.

Последнее называется credit-based flow control, оно необходимо для построения высокопроизводительных CPU, GPU и сетевых микросхем и применяется для интерфейса конвейерных блоков внутри микросхемы как обобщение того, к чему только прикасался Dally & Harting.

В принципе, этой кухней может овладеть даже способный школьник олимпиадного типа, не говоря уже о студентах. И не только этим, но и другими микроархитектурными штучками - арбитрами, контроллерами банков памяти итд. Проблема в том, что это ноу-хау плохо представлено в учебниках, хотя его можно накопать в патентах, статьях в интернете, на гитхабе (хотя там бывают чудовищно неправильные реализации) и на докладах на международных конференциях.

Чтобы решить эту проблему в России и дать некоторый импульс развитию российских микроэлектронных проектов, которые страдают от недостатка квалифицированных кадров, инициативная группа инженеров и представителей academia решила организовать серию докладов на выставке ChipEXPO-2021, которая пройдет 14-16 сентября в Сколково.

Вот полная программа и регистрация на Секцию 1 (упражнения с FPGA для студентов и продвинутых школьников): http://www.chipexpo.ru/shkola-sinteza-cifrovyh-shem-na-verilog

Регистрация на две другие секции (Секция 2: Микроархитектура, верификация и физическое проектирование микросхем и Секция 3: Продвинутые и экспериментальные методы автоматизации проектирования микросхем): http://www.chipexpo.ru/programm

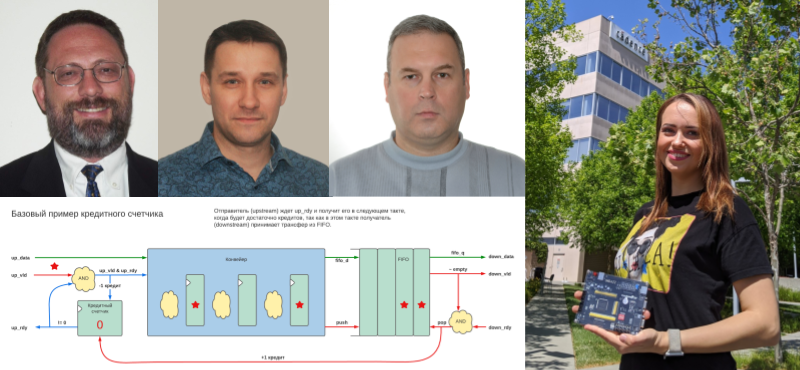

На семинаре будет например доклад от Дэна Гисселквиста, который, согласно блогу компании Symbiotic EDA, разработывал FIFO для ВВС США, а сейчас ведет блог ZipCPU.com и агитирует за использование методов формальной верификации:

А про комбинацию FIFO с кредитными счетчиками расскажет Дмитрий Смехов, инженер-разработчик ПЛИС, компании IRQ, ИнСис и Inline Group. Дмитрий занимается high-frequency trading - быстрой торговлей на бирже с помощью вычислений FPGA. Его доклад называется "Как организовать конвейер для обработки потока данных с максимальной пропускной способностью, минимальным размером памяти и без чрезмерных временных задержек: двойные буфера, очереди и кредитные счетчики".

Дмитрий на снимке в начале поста правее, рядом с девушкой Наташей, которая стоит с FPGA платой рядом с штаб-квартирой компании Cadence. Cadence, Synopsys и Mentor Graphics (ныне Siemens EDA) - триада ведущих разработчиков программ для проектировщиков микросхем.

Да, так вот Дмитрий Смехов начнет с краткого пересказа материала из учебника, который используют в Стенфорде, а потом перейдет к тому, чему в Стенфорде не учат.

А конкретно про FIFO расскажет Сергей Иванец, декан факультета электронных и информационных технологий Черниговского национального технологического университета (Сергей на изображении в начале второй слева, после Дэна Гисселквиста).

Сергей также будет вести второй день практических занятий на платах с микросхемами реконфигурируемой логики FPGA. Эта часть семинара на ChipEXPO будет доступна не только начинающих профессионалам, но и младшим студентам и даже продвинутым школьникам. Сергей будет показывать, как подсоединять к FPGA плате дисплей и рисовать на нем всякие картинки:

В самом Сколково организаторы ChipEXPO, в кооперации с московским вузом МИРЭА поставят штук 20 компьютеров с установленными на них Intel FPGA Quartus и принесут десятка три FPGA плат, но мы все-таки рекомендуем приносить свои ноутбуки и установить на них все заранее. Как это сделать объяснил Сергей Иванец на видео:

Главное отличие секции практических упражнений с FPGA этого года от школы 2020 года - это работа со звуком. Каждый участник получит микрофон и усилитель, и сделает серию экспериментов по распознаванию и генерации звуков.

Вы спросите: "Вы хотите учить школьников и первокурсников DSP и Фурье-преобразованию?" Нет, оказывается, ноты можно распознавать просто подсчетом тактов между пересечением уровня звука среднего значения, так называемым методом zero-crossing. Правда звук для этого должен быть близок к идеальной синусоиде.

Какой же инструмент генерирует звук такой чистоты? Это флейта! На наше мероприятие приедет флейтистка Мария Беличенко, которая сыграет короткие мелодии типа Yesterday Битлз или лирическую песню из сериала Бандитский Петербург, и конечные автоматы на верилоге, спроектированные участниками семинара, будут отличать одну мелодию от другой.

Примеры которые используются в этой части семинара работают со всеми версиями Quartus начиная с 13.0sp1. Желательно конечно использовать последнюю из бесплатных (Lite) версий, но текущая бесплатная версия Quartus Prime Lite Edition 20.1.1 не работает сразу после скачивания ни на текущей версии Windows 10, ни на текущей версии Linux Ubuntu 20.04 LTS. Для Windows у нее истекла дата сертификата драйвера, а для Linux она использует устаревшую библиотеку.

Обе проблемы можно решить: для Windows - c помощью скачивания patch, а для Linux - с помощью "sudo ln -sf /lib/x86_64-linux-gnu/libudev.so.1 /lib/x86_64-linux-gnu/libudev.so.0".

Если вы находитесь не в Москве и хотите поучаствовать в семинаре удаленно, и у вас нет FPGA платы, есть некий резерв FPGA плат, которые будут рассылаться по почте, со следующими ограничениями:

Получатель должен быть или школьником, или преподавателем вуза или школы или кружка, которому интересно внедрить упражения с реконфигурируемой логикой в свою деятельность. Насчет студентов и особенно работающих инженеров мы полагаем, что они могут купить FPGA платы сами - на AliExpress или через российских дистрибуторов.

Получатель должен показать сертификат, что он прошел три небольших онлайн-курса от Роснано «От транзистора до микросхемы», «Логическая сторона цифровой схемотехники» и «Физическая сторона цифровой схемотехники».

Деньги на платы, перевод и трансляцию мероприятия дали: Cadence Design Systems, Siemens EDA / МЕГРАТЕК (Megratec - Mentor Graphics Technologies), Наносемантика, Alchemical Music Box, Максим Маслов (сооснователь Eltechs) и Юрий Панчул.

Сертификат нужен по двум причинам:

Чтобы практический семинар принес пользу, необходимо, чтобы участник четко понимал концепции логического элемента, D-триггера и синтеза языков описания аппаратуры. Все это не программирование. Это проектирование аппаратных структур, несмотря на то, что код на Verilog-е незнакомому с ним человеку выглядит как программа. Все это сразу в голову не ложится - если просто сесть и начать с ним играться как с ардуино, то человек скоро упрется в непонимание что происходит. Поэтому нужно теоретическое предисловие.

Курсы связывают упражнения на FPGA с проектированием высокопроизводительных микросхем в большой индустрии, в которой проектируются микросхемы для айфонов и тесл. Это важно для мотивации, профориентации и перспективы.

Помимо базовой школы по FPGA и секции "что не учат в вузах но спрашивают на собеседования в электронные компании", на семинарах на ChipEXPO еще будут тьюториалы по современным методам функциональной верификации (шикарная ниша для бывших программистов на Java, которым захотелось двинуться в железо - в SystemVerilog есть объектно-ориентированные библиотеки и фреймворки.

Также на ChipEXPO будут:

Эдмунд Хуменбергер, евангелист открытых маршрутов проектирования, которые может быть когда нибудь станут такой же альтернативой Synopsys и Cadence, какой стал Линукс для Windows;

Стив Хувер, основатель стартапа, который сделал язык, автоматизирующий построение конвейера, чтобы вам приходилось меньше разбираться с этим клубком сигналов в коде на Verilog или VHDL;

Роберт Оуэн, известный консультант по образовательным программам (Texas Instruments, ARM, Xilinx) который в этот раз будет от Imagination Technologies - компании, которая в свое время спроектировала GPU внутри ранних Apple iPhone.

И презентации от компаний Cadence Design Systems и Siemens EDA / Mentor Graphics, которые входят в топ-3 разработчиков программного обеспечения для проектировщиков микросхем и поддержали это мероприятие.

Вот так!

Комментарии (24)

fromzerotoinfinity

24.08.2021 02:30+1Вот из=за этого не пойду, не куплю и слушать не буду....

<q>Бывший проектировщик микросхем для Военно-Воздушных Сил США </q>

Вот не люблю я это виляние хвостом.... Кто это? Бывший - это сказочно

YuriPanchul Автор

24.08.2021 02:35+1Вы прочитали заголовок и не читая пост сразу написали комментарий? В посте есть имя и фамилия, как и источник информации.

fromzerotoinfinity

24.08.2021 03:32+1Юрий, я, - легальный обладатель и Харрис на русском и приложения к нему в Вашем соавторстве. И если б там было Цифровой синтез: практический курс ОТ бывшего мегаразработчика из Королевской академии ВВС Британии, то не купил бы. Не люблю *лайф-кочей*

Я ж четко написал, что не пойду, не куплю и слушать\читать не буду именно из-за заголовка...

Можно ж было без реферансов написать - лекция в Cколково как верифицировать FIFO.

Читать статью не буду даже, если очень интересно.Дождусь очереной книги от Вас. Там уж точно прочту без США :)

YuriPanchul Автор

24.08.2021 05:34*** И если б там было Цифровой синтез: практический курс ОТ бывшего мегаразработчика из Королевской академии ВВС Британии, то не купил бы. Не люблю *лайф-кочей* ***

У вас предубеждение к военным контракторам или к разработчикам из громких организаций вообще? Между прочим Дэвид Харрис - не просто профессор в коледже, а бывший RTL дизайнер в Интеле. Представьте что я бы написал пост "Новая книжка по цифровой схемотехнике и архитектуре компьютера от бывшего разработчика Пентиума II". У вас бы сразу было отторжение?

amartology

24.08.2021 09:13+6Юрий, чтоб вы понимали — к вашему кликбейту в заголовках окружающие в основном относятся как к раздражающей, но безвредной причуде хорошего человека. Как, знаете, если гениальный профессор не может руки после посещения туалета. Так что дело, конечно, ваше, и каждый развлекается, как умеет, но в долгосрочной перспективе очков вам такое поведение не добавляет. Околополитические срачи можно оставить для фейсбука, а важное дело делать чуть более серьезно.

Что касается этой конкретной ситуации, вы же понимаете разницу между «бывшим разработчиком из большой компании Х» и «бывшим военным из армии Х»? Конечно понимаете, и понимаете, что сгенерит больше срача — поэтому из всех вариантов выбрали именно этот. Не людей, которые продвигают опенсорсные EDA, ни текущих разработчиков Samsung, Imagination и Syntacore. Нет, вы выбрали именно бывшего иностранного военного. Хинт: в нынешней околомедийной околомикроэлектронной ситуации фраза «человек из Yadro» привлекла бы больше кликов)

mpa4b

24.08.2021 19:54Такие конторы, как байкал или yadro — в основном занимаются склейкой готовых купленных IP-блоков (таких как ядра процессора, контроллер памяти, периферия, PCI-E, USB и т.д.), вряд ли там от RTL-разработчиков требуется уметь делать мультиголовое мультихвостовое двухклоковое фифо на связных списках в однопортовой памяти :)

amartology

24.08.2021 20:12Нууууу, принадлежащий Yadro Синтакор — вполне себе респектабельный разработчик именно что процессорных ядер.

YuriPanchul Автор

24.08.2021 20:31Вот это вы зря. Для проектирования системы на кристалле даже на основе лицензируемых ядер тоже нужно уметь проектировать извращённые FIFO, например с асинхронным возвращением кредитов. Чтобы связывать компоненты в некоторых случаях

Albert2009ru

25.08.2021 14:11Надо было назвать статью "Лекции проведёт девушка Наташа, при содействии таких то таких то..."... Я бы точно пошёл :)))))))))

mpa4b

24.08.2021 19:48Пустят на доклады только студентов и школьников? Или обычный человек тоже может попасть? На ссылке регистрации варианта два — или студент или школьник.

YuriPanchul Автор

24.08.2021 20:35Там есть ещё и ссылка на регистрацию для секций 2 и 3 http://www.chipexpo.ru/programm

mpa4b

25.08.2021 16:06Ааа, по этой ссылке я тоже регался. Инвайт пришёл вот только что, спасибо :)

mpa4b

06.09.2021 19:42Не спасибо. Только что пришло письмо, что мол бегом бегите на какие-то курсы от какого-то роснано и если успеете то может быть вас пустят.

Для сведения, мне нафиг не нужно втыкать в занятия с фпга платами, просто хотел послушать пару лекций. Но раз так...

YuriPanchul Автор

06.09.2021 19:54Вы наверное не прочли описание. Есть три секции - упражнения с FPGA, лекции по микроархитектуре и продвинутые. Курсы роснано требуются только и исключительно если вы хотите повтыкать в FPGA плату - потому что плат и посадочных мест меньше чем запросов, и мы хотим гарантировать, чтобы если уж кто-то будет втыкать, то он будет знать что он втыкает. Лекции по микроархитектуре и верификации проходят в другой комнате. Для них ничего проходить не надо - только зарегистрироваться. Их также можно посмотреть онлайн.

Gaari

27.08.2021 07:33я так понял выберут самых перспективных и они будут работать на ВВС США. Красиво подано!

amartology

27.08.2021 09:40YuriPanchul вот видите, это ровно то, о чем я говорю. Вы сами себе создаете дополнительные сложности и недоверие таким кликбейтом.

LordCarCar

Так что там с FIFO-буфером? Или Вы начинаете продажу билетов на хабре???

Khort

Хочется ошибиться, но судя по картинкам, там очередная вариация на тему асинхронного (на хендшейках) фифо.

YuriPanchul Автор

Вы ошибаетесь. На картинке полностью синхронное FIFO (и push и pop происходит с одним и тем же тактовым сигналом), просто оно стоит после конвейера с латентностью N и вся схема построена так, чтобы 1) при остановке интерфейса к соседнему блоку справа FIFO могло бы вместить все транзакции/пакеты/треугольники которые сейчас летят через конвейер и при этом 2) запуск транзакций слева от конвейера останавливался бы только тогда, когда в этом FIFO справа не было бы места для текущих в полете + новой транзакции. Это базовая схема конвейер + очередь + кредитный счетчик, но к ней есть много вариантов, в том числе асинхронных, где встает интересный вопрос возврата кредитов в асинхронном случае.

См. подробнее https://hsto.org/getpro/habr/upload_files/e1e/cf0/31c/e1ecf031ccf787e15c627bddd4999012.png

Khort

>просто оно стоит после конвейера с латентностью N

В том то и дело что не просто. Тактовый сигнал с множественным прохождением через комбинационную логику, латентность N ... С учетом вариаций параметров, у такого тактового сигнала очень быстро не останется буквально ничего ни от скважности, ни от фронтов, ни от min pulse width, а если что то и останется и схема таки заработает, то разброс летенси на выходе получится километр на километр - это вам любой SSTA инженер скажет. Поэтому единственный вариант общения с таким фифо - асинхронный CDC переход, а максимальная глубина фифо вовсе не N, а до тех пор пока тактовый сигнал еще похож на тактовый. Даже не вникая в логику работы этого фифо сразу видно огромное число проблем.

И, просто для справки - подобные схемы фифо известны с ~80х, к примеру GASP Сазерленда (SUN, 2000г.). Почти все они оказались не рабочими, т.е. дальше публикаций или прототипов дело не заходило.

Но, я ни в коем случае не против. Просто, немного "в теме", отсюда и критика.

YuriPanchul Автор

Троллить изволите? Где на моей диаграмме "Тактовый сигнал с множественным прохождением через комбинационную логику"? Тактовый сигнал распределяется через clock tree и подается на регистры всех стадий конвейера в одно и то же время плюс-минус skew. Нету на диаграмме никаких CDC переходов.

Я могу конечно нарисовать и FIFO с CDC, счетчиками Грея итд, но конкретно данная диаграмма - это не тот случай.

amartology