После полученных на предыдущие статьи о микропроцессоре Эльбрус откликов мне стало понятно, что для полноты картины не хватает рассмотрения вопроса – а что же делать? Можно ли каким-либо образом улучшить Эльбрус в качестве general-purpose CPU (на что намекали представители МЦСТ) и насколько? Можно ли его применить в каких-то локальных нишах? Давайте попытаемся разобрать данные вопросы.

Доработка микропроцессора Эльбрус для улучшения его характеристик в качестве general-purpose CPU

Как я упоминал в предыдущих статьях, проблемы VLIW-архитектур и статического планирования операций давно известны в индустрии. Поэтому в нашем анализе мы можем опираться не только на некоторые абстрактные идеи и соображения относительно архитектуры Эльбрус, но и на опыт разработки других VLIW-процессоров линеек Intel Itanium, Transmeta, Nvidia Denver, который зачастую очень показателен.

Итак, какие улучшения возможны в Эльбрусе, чтобы улучшить его характеристики в качестве GP CPU процессора?

Локальные микроархитектурные улучшения

Мы опустим мелкие изменения, которые фундаментально ни на что не повлияют. Но есть две вещи, которые жизненно необходимы для микроархитектуры Эльбрус – аппаратный префетчер данных (hardware prefetcher) и предсказатель ветвлений (branch predictor). Данные улучшения не дадут прироста на цифрах Spec CPU2006/2017, которые Алексей Маркин представил в своей статье, т.к. эти результаты получены на пиковых опциях с профилем (а значит, там сделан софтварный префетч и нет проблем с неудачными вызовами в горячих циклах). Но зато они существенно помогут при запуске «неоптимизированного» кода, как в примере с вызовом функции из первой статьи. Это не решит множества других проблем, но даст определённый прирост микроархитектурной скорости на реальных задачах.

Правда, здесь есть один важный нюанс: алгоритмы современных префетчеров и предсказателей достаточно нетривиальны, а в топовых процессорах они вылизывались десятилетиями. Поэтому сразу сделать хорошую реализацию этих модулей не получится - доведение до хороших характеристик потребует немало времени. В первых же версиях новые функциональности будут сбоить и иногда давать заметные ухудшения.

Также возникает проблема совместимости с кодом, откомпилированным под более ранние версии Эльбруса. И если добавление аппаратного префетчера можно сделать прозрачно, то внедрение предсказателя переходов в зависимости от реализации, либо вообще приведёт к несовместимости со старым кодом, либо не даст на старом коде никакого улучшения (вернее, даже даст ухудшение). Т.е. так или иначе, для получения преимуществ новых микроархитектурных улучшений потребуется перекомпиляция всей программной экосистемы.

Спикеры от МЦСТ заявляли, что предсказатель ветвлений планируется к реализации в новых версиях Эльбруса, а аппаратный префетчер чуть ли не уже реализован (правда, никакого упоминания об этом в публичных спецификациях я не нашёл).

Ну и не могу не отметить, что озвученные улучшения – это первый шаг к отходу от концепции статического планирования, сделанного «умным» компилятором.

Что касается других VLIW-процессоров общего назначения, то линейка Intel Itanium изначально имела branch predictor, а в процессе развития получила и hardware prefetcher. Что касается процессоров от Transmeta и Nvidia, то про их архитектуры намного меньше информации (они были скрыты под системами двоичной трансляции), точные данные мне неизвестны, но вероятнее всего, предсказатели ветвлений они в каком-то виде имели.

Динамические оптимизации

Собственно говоря, если обобщить мерцающие технические контраргументы в пользу микроархитектуры Эльбрус в различных дискуссиях, то они сводятся как раз к реализации «динамических оптимизаций». Примерно так это звучит со стороны неофициального телеграм-канала МЦСТ:

В МЦСТ работал сотрудник с такими же именем и фамилией, занимался двоичной трансляцией. Если это не совпадение, а детали и язык говорят, что это он, то Максим действительно знает архитектуру изнутри. Но против его аргументов есть контр-аргументы. Главный - что здесь рассмотрен случай компиляции помодульной, без использования какого-то профиля. А в нормальной "промышленной" реализации не хватает чисто софтварного инструмента - получения профиля от реального использования ПО и докомпиляция этого ПО с учётом профиля и всех имеющихся динамических библиотек.

Это не совсем тривиально, но именно с таким инструментом большинство аргументов Максима "против" можно снять.

И сама архитектура Эльбрус не стоит на месте, в неё добавляются динамические механизмы (уже добавлен префетчер, добавляются в следующей реализации предсказатели переходов и т.п.)

А так в статье Алексея Маркина (автора статьи в защиту Эльбруса):

Для качественной компиляции необходимо понимать, какие участки кода исполнялись больше, а какие меньше. Для этого существует понятие профилирующей компиляции. Это двупроходная сборка, на первом проходе которой выполняется сборка с опцией -fprofilegenerate, после чего программа запускается на обучающем наборе данных. Во время этого обучающего запуска программа выполняет сбор информации о переходах по ветвлениям, вызовах функций и исполнении циклов. На втором проходе производится сборка с опцией - fprofile-use, во время которой компилятор использует полученную информацию для определения оптимального набора и области применения оптимизаций. Использование этой технологии позволяет ускорить исполнение программ в среднем более чем на 17%. Такая схема бывает сложна для пользователя, более того она требует подбора тестовых данных таким образом чтобы программа исполнялась на тех же маршрутах что и при пользовательских данных

…

К перспективным исследованиям можно отнести использование возможностей аппаратного профилирования процессоров Эльбрус-16С для динамической оптимизации исполняемого кода

Показательно, что представители МЦСТ здесь явно признают наличие проблем производительности при компиляции без профиля, и даже совершенно верно указывают, что сбор профиля – это «не совсем тривиально».

Так что же означают эти туманные «динамические оптимизации»? На самом деле, всё достаточно банально – фактически речь идёт о реализации динамического оптимизатора наподобие JVM, который будет работать во время исполнения программы, в динамическом режиме собирая профиль и делая оптимизации, на нём основанные. А аппаратная поддержка тут нужна для сбора качественного профиля с минимальными накладными расходами.

Чисто в теории это - правильное направление. Например, VLIW-процессоры от компании Transmeta и линейка Nvidia Denver изначально исповедовали именно такой подход – они всегда работали ТОЛЬКО в режиме динамической трансляции. Таким образом они решали и проблему программной совместимости (эмулируя архитектуру x86 в случае Transmeta и ARM в случае Nvidia), и проблему отсутствия профиля. Потому что заставить всю программную экосистему переехать на компиляцию с профилем просто нереально, и в компании МЦСТ это тоже прекрасно понимают.

Но у этого решения есть вполне очевидная цена – необходимо разработать эффективный динамический оптимизатор, доработать программную экосистему, всё это интегрировать вместе, и к тому же опять перекомпилировать коды (потому что наиболее эффективная схема реализации динамических оптимизаций требует доработок компилятора lcc). Создать такое решение продуктового уровня даже при наличии опытной команды и достаточных ресурсов – это много лет разработки (я бы оценил в 5-10 лет), а в условиях кадрового голода МЦСТ у меня сомнения в реализуемости такого проекта в принципе. Недаром на текущий момент самые плохие цифры производительности у Эльбруса как раз на бенчмарках различных языков с динамической трансляцией байткода (Java, Javascript и т.д.). И опять-таки, это всё приводит к усложнению программного стэка (например, придётся отлаживать ошибки в коде, созданном динамически «на лету»), а как следствие - к увеличению количества сложных багов и проблем с интеграцией всего этого хозяйства.

Как «динамические оптимизации» улучшат ситуацию, даже если всё вышеописанное в конце концов сделать? Для цифр Spec CPU2006/2017 это снова не даст никакого роста производительности – напомню, что заявленные результаты от МЦСТ получены на пиковых уровнях оптимизации с профилем. Улучшения будут присутствовать опять-таки на «неоптимизированном коде» и составлять они будут в среднем порядка 17% - если ориентироваться на цифры, представленные Алексеем в своей статье (и эти цифры примерно согласуются с моими оценками).

Радикальная переработка микроархитектуры

Самый перспективный, но, к сожалению, нереалистичный вариант. Нереалистичный потому, что масштаб переделок таков, что он сопоставим с разработкой абсолютного нового процессора с нуля. При этом направление изменений будет диктовать отказ от множества особенностей Эльбруса, что по факту полностью девальвирует саму идею VLIW и статического планирования.

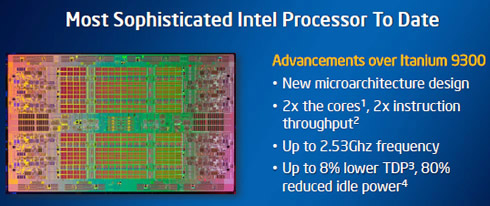

Но давайте подробнее. Для желающих глубже погрузиться в вопрос сложностей VLIW-архитектур, как их пытались решить и почему в итоге это направление было признано бесперспективным для general-purpose CPU, я настоятельно рекомендую поизучать историю линейки процессоров Intel Itanium. Как по мне, она крайне показательна. Ведь в разработку Intel Itanium были вложены огромные усилия и ресурсы – компания Intel видела в данной линейке свою будущую 64-битную архитектуру, из-за чего даже упустила создание x86-64 со стороны AMD, и была вынуждена догонять конкурента.

Особый интерес в плане изучения опыта Intel Itanium для нас представляет статья с говорящим названием «General Purpose VLIW is Dead»(ссылка). В ней описана микроархитектура уже 7-го поколения процессоров Itanium с кодовым именем Poulson. Это - вершина развития линейки Intel Itanium в плане микроархитектуры. Последнее, 8-ое поколение Kittson было де-факто тем же Poulson с улучшенными частотами. Посмотрим на схему микроархитектуры Poulson в сравнении с предшественником Tukwila:

Для Tukwilla всё типично для VLIW-архитектуры – инструкции, поступая с декодера, читают значения из регистрового файла и отправляются дальше на исполнительные устройства (последние на картинке опущены).

А что мы видим для Poulson? Инструкции с декодера попадают в Instruction buffer, а дальше - Branch Queue, ALU Queue, Memory Queue и т.д. Хм, да это же попытка реализовать простейший ОоО в условиях VLIW! По этому поводу автор статьи пишет:

Tukwila and all earlier Itanium designs were VLIW microarchitectures; compiled bundles formed the basis of execution and instructions were statically scheduled. Any dependencies were resolved by global stalls. The global stall microarchitecture would halt the entire pipeline until the problem had been resolved.

Poulson is fundamentally different and much more akin to traditional RISC or CISC microprocessors. Instructions, rather than explicitly parallel bundles, are dynamically scheduled and executed. Dependencies are resolved by flushing bad results and replaying instructions; no more global stalls. There is even a minimal degree of out-of-order execution – a profound repudiation of some of the underlying assumptions behind Itanium

Последнее предложение подводит знаковую черту под концепцией VLIW-архитектур – в итоге своего развития они пришли к тому, что необходимо реализовывать ОоО-исполнение внутри процессора. А в таком случае все особенности VLIW – это лишь помеха. Поэтому отказ от VLIW-архитектур для general-purpose CPU стал неизбежностью.

В условиях Эльбруса всё аналогично. Если делать столь радикальные переделки микроархитектуры с реализацией ОоО во VLIW-архитектуре, то это колоссальная по сложности работа. Причём по её итогу придётся просто выбросить многие «фишки» Эльбруса, которые станут ненужными. А главное – сама концепция широкой команды в таком случае становится не только бессмысленной, но даже вредной. Поэтому намного проще взять обычную RISC архитектуру и сделать на её основе современный процессор с ОоО-исполнением. Это будет проще, быстрее, дешевле, а в итоге получится более быстрый и удобный для пользователей процессор.

Давайте подведём небольшой итог. Из реалистичного (префетчер, предсказатель ветвлений,и даже пусть динамические оптимизации) - в Эльбрусе можно сделать набор определённых улучшений, которые позволят улучшить производительность на реальных задачах. При этом из предыдущих статей помним, что верхний предел микроархитектурной скорости на Эльбрусе, рассчитанный по данным запусков на Spec CPU2017, в 3-4 раза уступает современным RISC/CISC процессорам с ОоО исполнением. Эта оценка не изменится. Для «неоптимизированного кода», где производительность может деградировать в разы от микроархитектурной скорости на Spec CPU2017, ситуация улучшится. Ввиду отсутствия Эльбрусов в свободном доступе нет возможности привести точные значение ускорения. Но, я бы грубо оценил, что на коде из реальной жизни средняя производительность сейчас падает в 2 раза по сравнению с цифрами на Spec CPU2017, т.е. Эльбрус по микроархитектурной скорости приблизительно в 6-8 раз хуже современных RISC/CISC аналогов. Предложенные улучшения подтянут это соотношение где-то к 5.

Из вышеизложенного, как мне кажется, вывод достаточно очевиден – попытка допилить Эльбрус принципиально ничего не изменит. Как general-purpose CPU он всё равно будет существенно уступать современным RISC/CISC аналогам именно в силу изначальной концепции, заложенной в архитектуру. Индустрия этот путь прошла, различные варианты решения проблемы известны и изучены, они не помогают. Яркий пример в этом отношении - история линейки Intel Itanium. Компания МЦСТ в данный момент лишь пытается повторить то, что 20 лет назад уже было опробовано. Но результат здесь уже известен заранее.

Потенциальные ниши для применения микропроцессора Эльбрус

Но бесперспективность Эльбруса как general-purpose CPU ещё не говорит о том, что не существует локальных ниш, в которых он может быть конкурентоспособен. Попробуем проанализировать, где микропроцессор Эльбрус всё же может найти своё применение.

-

Специализированные процессоры

Хотя VLIW-архитектуры больше не применяются в general-purpose CPU, тем не менее, они находят широкое применение в специализированных решениях, таких как DSP процессоры и графические процессоры (хотя в графике VLIW-архитектура тоже уже не самый оптимальный подход). Но переделывать Эльбрус в решения такого рода малоэффективно. Данный процессор изначально проектировался для серверного и десктопного сегментов, в нём множество вещей, не нужных для специализированных решений, и наоборот – нет необходимой специфики для других доменов. Можно на базе наработок Эльбруса создать какое-то решение, но это де-факто будет разработка нового специализированного чипа. Поэтому данное направление развития не является сколь-либо перспективным для Эльбруса, на мой взгляд.

-

Решения для безопасности

В Эльбрусе есть две функциональности связанные с безопасностью, отсутствующие в массовых процессорах, доступных сейчас на широком рынке – это отдельный стек вызовов и аппаратная поддержка тегированной памяти. В остальном он ничем принципиально не отличается по безопасности от современных RISC/CISC процессоров.

Отдельный стек вызовов – полезная «фишка», но проблема в том, что она закрывает только одну из множества потенциальных угроз – так называемую ROP-атаку. При прочих равных, это приятное дополнение, но только при условии, что по остальным характеристикам процессор конкурентоспособен. Т.к. для Эльбруса это не так, то ценность наличия отдельного стека вызовов становится нулевой.

А вот с тегированной памятью, на мой взгляд, ситуация интереснее. В теории, компиляция и запуск программы в таком режиме (называемым защищённым) позволяет обнаруживать различные ошибки и потенциальные уязвимости в коде. Сейчас в индустрии многие крупные компании тратят серьёзные ресурсы на поиск и исправление ошибок в своих продуктах, используя разные программные средства статического и динамического анализа корректности поведения программы. Вполне возможно, что для них будет интересно использовать программно-аппаратное решение на базе Эльбруса, если оно будет быстрее или качественнее. Правда, данный рынок крайне мал, и вряд ли там потребуется больше нескольких тысяч Эльбрусов. Но это уже задача для маркетологов МЦСТ - детальнее разобраться в потенциале данного направления

-

Запуск Windows-приложений

В контексте импортозамещения может возникнуть ситуация, когда некоторый софт будет возможно запустить только под Windows. И если сделать эффективное решение по двоичной трансляции для Linux-приложений можно без аппаратной поддержки, то запустить Windows без помощи со стороны процессора уже достаточно сложно и требует большого времени на разработку. В то же время в Эльбрусе аппаратная поддержка для двоичной трансляции и сам транслятор уже присутствуют. В том случае, если пользователи готовы смириться с существенной потерей в производительности, решение на базе Эльбруса вполне может им подойти. Но тут есть одна стратегическая проблема – если мы ставим процессоры в рамках импортозамещения, то странно для таких решений использовать ОС Windows. Т.е. переход на Linux-based дистрибутивы и перевод всего программного обеспечения под Linux в данном случае будет лишь вопросом времени. Поэтому Эльбрус здесь может выступать лишь как решение для переходного периода, и в перспективе этот рынок будет стремиться к нулю.

-

High Performance Computing (HPC)

Если мы внимательно посмотрим на характеристики процессора Эльбрус, то заметим, что он обладает достаточно внушительными показателями так называемых GFLOPS. Иными словами, потенциально, Эльбрус может совершать очень большое количество операций над вещественными данными за единицу времени. Например, для самого последнего процессора от МЦСТ Эльбрус – 16С этот параметр составляет 750 GFLOPS для вещественных чисел двойной точности. Этот показатель не просто внушителен в пересчёте на одно ядро, где он вплотную подбирается к самым топовым решениям от Intel, но даже очень прилично выглядит в абсолютных значениях. Самый производительный процессор от Intel, который я нашёл в данном списке, имеет 1612 GFLOPS, и это показатель для 28-ми ядерного решения!

Да, мы знаем, что на практике в Эльбрусе эти гигафлопсы плохо помогают на большинстве реальных задач от пользователей, но логично тогда поискать тот класс задач, где их можно всё-таки заиспользовать. И тут сразу напрашивается ответ – это High Performance Computing (HPC). Опять-таки, далеко не для всех задач в HPC количество гигафлопсов важно, но в общем и целом - это тот класс задач, где многие недостатки VLIW-архитектуры нивелируются, и Эльбрус может демонстрировать свой потенциал не только на бумаге. Тем более, что HPC вычисления, как правило, сопровождают достаточно квалифицированные специалисты, которые понимают специфику своих вычислений и по природе своей работы должны углубляться в особенности процессора и могут адаптировать программу под Эльбрус.

Из недостатков данного рынка применений для Эльбруса – он также крайне ограничен (сюда включаются как непосредственно суперкомпьютеры, так и часть пользователей, которым нужен запуск такого класса задач на своих машинах). Можно говорить о тысячах, возможно о десятках тысяч процессоров. Но всё равно это небольшие объёмы, которые будут держать реальную цену процессора очень высокой. Наличие вычислительного кластера, который хорошо считает только на определённых задачах, также не добавляет Эльбрусу плюсов в глазах потенциального клиента. Также здесь Эльбрус фактически вступает в конкуренцию с современными графическими картами, но т.к. в России они сейчас вообще не производятся, этот момент можно пока опустить.

Собственно, на мой взгляд, это все варианты, которые заслуживают обсуждения. Ситуации, когда приобретение процессора лишено экономической логики, рассматривать смысла не вижу - там возможно всё, что угодно.

Если внимательно посмотреть на вышенаписанное, то можно суммировать, что у Эльбруса, как представителя семейства VLIW-архитектуры, нет потенциала приблизиться к современным RISC/CISC процессорам по производительности на general-purpose нагрузках, даже с учётом доработок.

При этом возможные ниши для практического применения Эльбрусов существуют, но эти ниши достаточно узки и в большинстве случаев Эльбрусы в них могут быть безболезненно заменены обычными RISC/CISC процессорами.

Комментарии (212)

YuriPanchul

02.10.2021 20:20+2*** внедрение предсказателя переходов в зависимости от реализации, либо вообще приведёт к несовместимости со старым кодом, либо не даст на старом коде никакого улучшения (вернее, даже даст ухудшение). ***

А почему? Из-за введения каких-нибудь инструкций типа branch likely? Это совсем необязательно, branch predictor можно сделать прозрачным, только сливать конвейер при mispredict.

Armmaster Автор

02.10.2021 21:56+3Если сделать branch предиктор прозрачным - это вариант 1. Но в таком случае все nop'ы в старом коде останутся и бранч предиктор ничего не даст, только в момент перехода начнёт ещё иногда ошибаться и это даст ухудшения. Хотя может быть это можно как-т ооптимизировать, надо подумать.

BugM

03.10.2021 03:28+1Это же решается просто перекомпиляцией тех же исходников.

С учетом количества и массовости софта под Эльбрус перекомпиляция всего и раскатка в прод новых версий под новый процессор не выглядит нерешаемой задачей.

Armmaster Автор

03.10.2021 16:07Я не уверен, что это можно назвать простым, учитывая, сколько сейчас копий ломается вокруг портирования софта. В любом случае это лишняя работа, причём в контексте Эльбруса более объёмная, чем для других архитектур

Vedomir

02.10.2021 22:50+2Правда здесь есть один важный нюанс: алгоритмы современных префетчеров и предсказателей достаточно нетривиальны, а в топовых процессорах они вылизывались десятилетиями. Поэтому сразу сделать хорошую реализацию этих модулей не получится — доведение до хороших характеристик потребует немало времени. В первых же версиях новые функциональности будут сбоить и иногда давать заметные ухудшения.

Если я все правильно понял, то это проблема будет касаться и RISC out-of-order процессоров отечественной разработки не считая покупки уже готовых ядер от той же самой ARM где все это уже делалось кучу времени.

Armmaster Автор

02.10.2021 23:00+4В целом - да. Хотя в случае RISC-V есть большая экосистема с разделением труда, где уже опытные люди будут писать сами ядра на HDL (включая branch predictor) и их оптимизировать, и цикл разработки там более короткий, что позволит быстрее довести реализации до хорошого уровня.

victor_1212

02.10.2021 23:56>В Эльбрусе есть две функциональности связанные с безопасностью, отсутствующие в массовых процессорах, доступных сейчас на широком рынке – это отдельный стек вызовов и аппаратная поддержка тегированной памяти.

на перспективу (далекую) развитие в этом направлении вероятно будет востребовано, учитывая опыт компании об этом стоит подумать, нечто подобное CRASH для специальных применений в первую очередь

ps

Б.А. вскользь упоминает об этом проекте в своей старой статье

Armmaster Автор

03.10.2021 00:11Вопрос в масштабе этого рынка. У меня есть сомнения, что он позволит хоть как-то окупить разработку процессора. Да и по факту мы видим, что на текущий момент никакого особого спроса по данной линии на Эльбрус нет.

victor_1212

03.10.2021 01:40+1>позволит хоть как-то окупить разработку процессора ...

правильно, не позволит очевидно, и спроса нет потому что пока гром не грянул, креститься никто не собирается, но именно это направление заслуживает внимания, и cpu cycles, как обычно строго imho

vladshulkevich

03.10.2021 18:03+1как я уже неоднократно предполагал, проблемы окупаемости нет. Причем тут масштаб рынка вообще не вкуриваю. Это "изделие военной техники".

surVrus

02.10.2021 23:57+4Благо дарю за статью! Очень познавательно.

Однако мне хотелось бы добавить одну бочку дегтя, к описанной ложке меда про потенциальные возможности Эльбруса.

И только в аспекте экономики и рынка. Технику и технологию оставлю в стороне.

Допустим, что у Эльбруса есть перспективы в какой-то нише. Эта ниша может быть в России, и может быть (чем черт не шутит) и в некоем экспортном потенциале.

Берем самый оптимистичный сценарий: всем чиновникам в России поставят только компы с Эльбрусами. Это от 2 до 3 млн компов. Плюс еще столько же всей их мишпухе. Выходит - от 4 до 6 млн штук. Каждому военному тоже по компу. Еще столько же выйдет (мы оптимисты!). Итого - от 8 до 12 млн штук весь рынок. Много это или мало? Мировой рынок компов (включая таблеты) в 2020 году около 460 млн штук. То есть вся эта байда с Эльбрусом - менее 3% от рынка. Если по-честному, то в пределах погрешности оценки этого самого рынка.

За что биться? все госзаказы, вся военка вместе взятая - это слезы и мелочи на экономической арене. Да и этот сегмент рынка - весьма "хрупкий". Рано или поздно кому-то в правительстве взбредет в голову вернуться к "интеграции" и "миру-мир" - и вся эта бредятина про "импортзамещение" сгинет без следа, вместе с Эльбрусом. Так не будет? Да только на моей памяти (за последние 40 лет) в России политический строй поменялся 2 раза. Про всякие там "политики гласности", и прочее - вообще вспоминать лень.

И что тогда? Не будет лоббирования "госзаказа" - рухнет вся структура Эльбруся. Потому как без такого "госзаказа" - она неконкурентноспособная, от слова "совсем". Нигде, никому кроме этого сегмента принудительного "госзаказа" не нужная.

Armmaster Автор

03.10.2021 00:19+3Если продавать любой российский general-purpose проц тиражом порядка 10 млн в год, это будет суперокупаемый продукт, а компания будет торговаться на бирже в топ-10.

Но в предыдущих статьях я уже высказал своё мнение, что:

По возможности процессор должен иметь экспортный потенциал.

Текущая помощь от государства должна в итоге к тому, чтобы отечественные компании, производящие процы, смогли выйти на горизонт конкурентоспособности, чтобы быть в состоянии вести экономическую деятельность с минимальной поддержкой от государства.

Ну т.е. мне кажется, это тезисы перекликаются с тем, что вы написали.

plumqqz

03.10.2021 00:57+2У Эльбруса как раз замечательный экспортный потенциал - это не штатовский процессор, а уверенно обстреливать штатовские корабли и самолеты хотели бы уметь очень многие страны, так что эльбрус может быть очень интересен; рынок, правда, все равно маленький.

checkpoint

03.10.2021 03:41+3Для того, что бы обстреливать чьи-то корабли нужны ПЛИС, процессоры в этой теме уже давно ушли на второй или третий план.

plumqqz

03.10.2021 14:39

checkpoint

03.10.2021 23:18Про них и речь. Там все на ПЛИСах. ЦП используется в рабочих местах оператора, типа ПЭВМ ЕС1866, в которую просится что-то на базе ARM или MIPS.

mikhanoid

04.10.2021 17:20Плисы не везде «влезают» по своему энергопакету. DSP-процессоры используют не реже.

surVrus

03.10.2021 09:45а уверенно обстреливать штатовские корабли и самолеты

Не совсем понимаю, как связаны процессоры и обстрел каких-то кораблей. Если возможность обстрела кораблей существенно зависела бы от вычислительной мощности того, кто стреляет, то шансов их обстрелять не было бы никаких. Подключить неограниченные вычислительные мощности (тупо 100 500 000 процессоров) для США не представляет скорее всего никакой проблемы.

Кстати, если это могут быть любые процессоры, в том числе и Эльбрус. Американцы могут их свободно использовать в таком своем гипотетическом "супер оружии" Не?

Наверное и иным странам ничего не мешает использовать процессоры, разработки США, против кораблей США. Вроде нет никакого метода для процессора определить, в какой области знания работает программа на нем. Встроенного в процессор метода.

Ну и Ваши представления о текущем уровне военной техники сильно искажены. Ни в военке, ни в космосе, в "критических" и "важных" технологиях процессоры типа Эльбрус практически не используются. Скажем так, там используются намного более примитивные, более быстрые, более простые, более надежные, менее очевидные, но и более дорогие методы решения задач, которые на "гражданке" решаются при помощи процессоров.

Paskin

03.10.2021 13:40Разговоры про необходимость не-Штатовских процессоров вызваны обычно верой в то, что штатовские можно каким-то образом отключить в угрожаемый период - как правило, не подкрепленной знаниями, тем более - как это сделать, не "задев" свою же технику.

Эльбрусы вроде как собирались использовать во всяких АРМ и системах управления - хотя судя по тому, что даже в пропагандистских роликах команды все равно отдаются голосом по телефону - они действительно не mission-critical.

plumqqz

03.10.2021 14:41Вы это, например, Эрдогану объясните, который после попытки переворота вдруг озаботился не штатовской ПВО.

stranger_shaman

03.10.2021 16:04в этой не штатовской ПВО вовсю используются штатовские атмеги.

amartology

04.10.2021 12:13+4Вы бы не писали такое в интернет. С прошлой пятницы за такое можно уголовное дело получить.

odins1970

03.10.2021 16:13Вы можете гарантировать, что интерес Турции к системе ПВО российского производства не является частью ее игры с США , для выбивания себе экономических и политических льгот ???

sim2q

04.10.2021 09:59Никто не может гарантировать что то на 100%, но так получается, что "у нас" вообще ничего не будет

uzverkms

03.10.2021 12:09+1Настоящий взлёт x86 (Intel) случился не из-за необходимости кого-то обстреливать, а из-за выхода на широкий гражданский рынок.

surVrus

03.10.2021 10:26Если продавать любой российский general-purpose проц тиражом порядка 10 млн в год,

В том-то и беда, что я ошибся. У буржуев продают по 450 млн компов в год. А в России - весь рынок "компов для чиновников" и "военки" - 10-12 млн. Не на год, а вообще.

Да и скорее всего не смогут столько выпустить процессоров, если 10 млн в год компов надо делать.

По возможности процессор должен иметь экспортный потенциал.

Это да, тут я с Вами согласен. Но Эльбрус его не имеет, совсем не имеет. Ключевое слово тут "никогда".

смогли выйти на горизонт конкурентоспособности,

Это да, тоже все верно. Главное тут - сроки. Государство может (даже обязано) управлять развитием технологий, давать на это огромные деньги и ресурсы. Но с точно обозначенной экспортной целью и не менее жестко ограниченными сроками. Тогда обычно такая поддержка срабатывает.

это тезисы перекликаются с тем, что вы написали.

Да, совершенно с Вами согласен.

lelik363

03.10.2021 15:13За что биться? все госзаказы, вся военка вместе взятая — это слезы и мелочи на экономической арене.

Есть ещё IIOT — промышленная автоматизация и промышленный интернет. Рынок очень большой. А так как Россия страна с преимущественно холодным климатом, то процессоры с рабочим диапазоном температур -45С… +100С имеет хорошую перспективу.

surVrus

03.10.2021 17:48+1Есть ещё IIOT

Есть такая песня. Но в ее тексте нет слова "Эльбрус".

При энергопотреблении от 50 Вт, перспективно использование такого процессора только в качестве системы отопления в квартире.

Насчет промышленной автоматизации - тут да, тут Вы правы. Но в этой области роль самих процессоров небольшая. Более важны всякие интерфейсы (ADC DAC входы-выходы). Причем чтобы все это было надежным, защищенным от разных помех, и т. п. То есть вся "обвязка" автоматики занимает намного больше места и более важна. А ее "от производителей Эльбруса" нет. Есть вполне себе обычные стандартные решения. И вот зачем тогда нужен очень дорогой супер-процессор, который еще и купить не так просто?

Да и в автоматике важную роль играет софтовая "обвязка" этого всего железа, привычки и предпочтения разработчиков. Чтобы туда влезть со своим продуктом надо потратить не один год.

lelik363

03.10.2021 21:10+1При энергопотреблении от 50 Вт, перспективно использование такого процессора только в качестве системы отопления в квартире.

Странное заявление. Во всем мире считают иначе. COM-HPC Ampere Altra 175W TDP — это один из примеров решения промышленного использования.

surVrus

03.10.2021 22:09-2Согласен. Для 1-2% задач IIOT может быть такое применение, где TDP не играет особой роли.

И уупс, я пропустил в слове IIOT одну буковку I. Ошибочка, прошу прощения.

Я то думал про IOT, про него и написал.

OpenA

06.10.2021 06:44+2Я ничего не фантазирую а смотрю в ассемблер и на сообщения компилятора.

И он скомпилировал это без каких либо предупреждений, при этом в ассемблере хорошо видно что:

{ nop 2 return %ctpr3 addd,0,sm 0x0, 0x0, %dr21 ldgdw,2,sm 0x0, [ _f32s,_lts0 start ], %r0 addd,3,sm 0x0, 0x0, %dr23 ldgdw,5,sm 0x0, [ _f32s,_lts0 start ], %r1 } { sxt,2,sm 0x2, %r0, %dr20 sxt,5,sm 0x2, %r1, %dr22 } { movtq,0,sm %qr20, %qr20 shls,2,sm %r2, 0x2, %r0 movtq,3,sm %qr22, %qr22 }1. он загружает данные размером 32бита

2. кладет их в двойной регистр (младшую часть квадрорегистра), старшую часть заранее заполнил нулями,

3. и наконец делает над квадрорегистром адресное преобразование командой movtd (mov tag data или что то типа этого).

Скорее всего он создает таки локальный указатель на данные, по типу

(StructRGB *){0,0,0,}только с числом, используяarrкак переменную. Если это так то упало скорей всего из за+ indexнадо попробовать отставитьarr = (int*)startи посмотреть будет ли ссылка на число.А при чтении массива падать будет все равно потому что безопасный режим не разрешает читать неинициализированные данные надо его перед этим или заполнить или использовать memset(arr, 0 sizeof(int) * n)

Читать плачь про слишком строгие правила работы с указателем было забавно, учитывая что в других языках с ними вообще ничего нельзя делать, кроме как получить или передать. Запустите лучше вот такой код, если вам не сложно. Интересно все таки структура указателя, по ассемблеру получается что при складывании он увеличивает поле size, может расположение не такое просто.

a1batross

05.10.2021 13:03+2Вы показали код с UB, который стреляет вам в ногу. Какой нехороший защищенный режим, на нём код с UB не работает!

Armmaster Автор

03.10.2021 00:56+2В некоторых компаниях готовы переписывать код и тратить на это большие ресурсы, если это повысит надёжность кода. Поэтому я вполне могу предположить, что какая-нибудь крупная компания скажет - "окей, наша задача - портировать проект на Эльбрус в защищённом режиме. Если что-то не работает - значит это ошибка и мы переписываем код". Потом полученный результат возвращается обратно на родную систему и там уже компилируется в итоговый продукт. Безусловно, мало кто на такое пойдёт (я потому и написал, что потенциал рынка небольшой). Но в теории это возможно. Насколько для таких задая valgrind и/или sanitizer лучше - вопрос открытый. Возможно, что лучше. Тогда действительно защищенный режим будет никому не нужен.

OpenA

04.10.2021 23:09Там принципиальная проблема: в защищенном режиме 128-битовый указатель содержит размер выделенного блока, тэги, адресс начала блока и offset.

В коде часто встречается присвоение целому значению указателя, потом какая-то арифметика над этим целочисленным значением, а потом присвоение нового значения обратно в указатель.

Если речь про что то типа такого:

int *arr = malloc(sizeof(int) * n), start = (int)arr; ... if (index > n) { arr = start + (index - n); }То это скорее всего работать не будет, но будет работать вот так:

int *arr = malloc(sizeof(int) * n), *start = arr; ... if (index > n) { arr = start + (index - n); }Причина не в 128и битных указателях. В ассемблере адрес все равно ложится в виде числа на регистр, обращение к памяти происходит специальными командами, в том числе поддерживающими обращение по смещению. А вот сохранить на стек в виде указателя то что не является указателем уже нельзя, банально потому что указатель в безопасном режиме - это тип, а у типов строгие правила преобразования в (зависимости от языка).

В данном примере указатель складывается с целым, что по правилам Си дает указатель. Но вообще оказалось что работает и в первом случае, если расставить явные преобразования типов https://ce.mentality.rip/z/PcrYGM

К слову указатель на процедуру отличается, полагаю и работа с ним тоже. В любом случае весь вот этот безопасный режим это просто как аппаратная виртуальная машина для Си привносящая в него безопасность уровня джавы. И это не такой режим как в интеле при переключении 32/64 адресации, он работает как отдельное адресное пространство работа с которыми происходит через специальные команды. Функции из него наверное даже можно из небезопасного режима вызывать с некоторыми ограничениями, надо только в ОС реализовать поддержку.

a1batross

05.10.2021 02:40+2Представьте себе код в котором норма кастовать указатель в какой-нибудь int, считать это нормой и надеяться что это не выстрелит.

Ну ладно, кому-то и так сойдет.

vakhramov

03.10.2021 16:50+1Рынок персоналок? Есть места, где надо много вычислительных мощностей разного характера применять. Так что рынок процессоров - это не только рынок ПК.

Wan-Derer

05.10.2021 07:05+1всем чиновникам в России

Добавь школы/ВУЗы

в некоем экспортном потенциале.

Соседние страны, которым тоже постоянно грозят сцанкциями.

Страны, которые тоже хотят получить хоть что-нибудь неамериканское. Вспомним скандал с "прослушкой" германского начальства. Прекрасный был повод подкатить к бабуле и предложить! Почему не сделали - непонятно. Хотя может и сделали, просто нам не сказали.

ЗЫ: конкретно у Эльбруса тут м.б. внутренняя конкуренция. Вон, Байкал уже запилил десктопный проц и грозят серверным...

anonymous

00.00.0000 00:00

Armmaster Автор

03.10.2021 00:29+1Я потому и написал - в теории. Там на самом деле можно вокруг этого играться и доводить до чего-то удобоваримого, наверное. По-крайне мере какие-то идеи были в эту сторону, но актуальной ситуации я не знаю. В конце концов, это не моя головная боль, пусть МЦСТ думает.

a1batross

05.10.2021 15:08Да куда отводить-то разговор? Я не читал ветку, мне в целом всё равно. :)

Но вот про uintptr_t я не знал. Как-то странно что его тоже не расширили. Подстава, однако.

Но я всё же про каст адреса в int где гарантии что адрес поместится нет. И вот тут будут проблемы не только с защищенным режимом, но и с LP64.

a1batross

05.10.2021 18:41+1Я повторюсь.

int, не long. И даже так, long не говорит о том, что указатель в него уместится.

Для этих вещей придумали (u)intptr_t и да, очень неочевидно что он не совпадает с указателем в режиме ptr128. Наверное это баг.Если бы я имел отношение к МЦСТ, я бы завёл им баг. Но на самом деле мне лично всё равно.

LiauchukIvan

03.10.2021 00:49+1Спасибо большое за очередную интереснейшую статью. Очень приятно, будучи чайником в вопросах архитектур ЦПУ, всё-таки понимать куда, как и почему мы движемся в данном направлении.

Касаемо практического применения Эльбрусов, какое у вас мнение о так называемых Горынычах, которые сейчас поставляются на базе этих процессоров, и вроде бы вполне успешно занимают свою нишу.

Armmaster Автор

03.10.2021 01:04Я не очень понимаю этого кадавра. Возможно, где-то "многоместные рабочие станции" имеют смысл, но со стороны они выглядят странно. Уж делать тогда нормальные тонкие клиенты на сервер. А тут полурешение какое-то.

В любом случае, для таких применений любой GP CPU будет лучше - это его нагрузка. Да тот же Байкал-М там превзойдёт Эльбрус-8С.

Civil

03.10.2021 02:10+1Я не очень понимаю этого кадавра.

Я могу предположить, что этот кадавр появился только потому, что Эльбрус - редкий зверь. Так можно попытаться представить что он стоит дешевле (в 4, кажется, раза, на 1 рабочее место). Главное не обострять внимание на том, что это обычное разделение одной машины (и на том, что это не уникальная для Эльбрусов вещь).

a1batross

04.10.2021 18:40+2А 8СВ нет.

Civil

05.10.2021 01:53В типичных для людей задачах - и его тоже, в несколько раз притом.

a1batross

05.10.2021 02:36+2Что такое типичные задачи? A57 не вытянет мои ежедневные типичные задачи. :)

Civil

05.10.2021 10:30-1Ну посмотрите чем типично люди занимаются (как на работе так и дома). Вот обобщенно-собирательный образ и будет этим "типичные задачи" (строго говоря большая часть это браузер и js для среднестатистического юзера).

И я не говорил что А57 их будет хорошо тянуть, просто 8СВ будет еще хуже.

a1batross

05.10.2021 13:07+2Кроме специфичного софта который прибит к x86, я не вижу чего-то сложного.

8СВ к вашему сожалению не настолько плох, я его видел в работе и поставил бы рядом с основным десктопом. За одним работать, а другому оставить роль аппаратного ускорителя вебни.

VLev

03.10.2021 01:08+1Спасибо за статью.

В отличие от двух предыдущих -- тут практически со всем согласен без оговорок.

Единственный вопрос (боюсь, риторический):

Почему за 20 лет существования микроархитектуры (например, в Verilog) и 12 лет существования Эльбрусов 6 чтоли поколений в железе так и не были реализованы указанные улучшения в микроархитектуре, а сильные стороны (FLOPs-ы) не были проявлены хотя бы в демонстрационном супере?

Про кластер в ЦИАМ знаю, но он ни разу не демонстрационный. Это всё равно как в чёрной дыре установить.

Armmaster Автор

03.10.2021 01:37+2Почему за 20 лет существования микроархитектуры (например, в Verilog) и 12 лет существования Эльбрусов 6 чтоли поколений в железе так и не были реализованы указанные улучшения в микроархитектуре

Сначала были объективные кадровые проблемы, после покупки МЦСТ Интелом. Опытных людей практически не осталось. Потом уже была просто боязнь руководства что-то радикально менять. Боялись, что не потянут.

а сильные стороны (FLOPs-ы) не были проявлены хотя бы в демонстрационном супере

Потому что PR отдел МЦСТ мало на что реально влияет, а руководство видит свою задачу в своевременной сдаче ОКРов.

livelace

03.10.2021 01:22+6Мне показалось, что ваша серия статей о процессорах Эльбрус несколько предвзята (я три дня гналась за вами, чтобы сказать,

как вы мне безразличныкак ваша архитектура неудачна).

Тем временем. Я не припомню, чтобы где-то заявлялось о завоевании рынка Intel/AMD. Напротив. Все заявления крутятся вокруг специализированных решений для государства/бизнеса. Если компания не ставит себе таких задач, то может не стоит от неё ждать преодоления воображаемых рубежей?

Я подверился и посмотрел свежее видео (https://www.youtube.com/watch?v=OXN_YfbfeBg&t=1219s), где все тезисы (звучащие многие года) остались прежними. Из изменении для себя отметил: появление СХД, работа в энергетике/газотранспорте, ноутбуки и т.д.

Давайте не будем «драматизировать» раньше времени. Процессоры, это ведь не только архитектура в вакууме, но и технологические решения и производственные мощности. Развернуть диван в сторону x86 всегда можно, особенно когда компетенции «вдруг» появились.

le2

03.10.2021 02:04я вижу такую киллер-фичу отечественных процессоров — у всех есть поддержка ecc-памяти из коробки.

Маркетологи Intel (и AMD) простым решением перевели свои массовые процессоры в разряд «детских», лишив их ecc.

Civil

03.10.2021 02:16+3У AMD, кроме их APUшек, поддержка ECC есть везде. Этим они отличаются.

Дальше про массовые процессоры - каждому Core i есть соответствующий Xeon, у которого с ECC проблем нет. Например тому же i9-9900k соответствует Xeon E2288G и разница в рекомендованных ценах у них 50$ (539$ против 489$).

Плюс "детскость" относительная. Дома ECC не то чтобы нужен обычным пользователям.

sherbinko

03.10.2021 02:45Почему не нужен? В моих 32 G возникает в среднем 4 ошибки за день (по статистике).

Это довольно-таки ощутимо на мой взгляд. По крайней мере, синий экран периодически наблюдаю.

Civil

03.10.2021 03:01Потому что для решения такой проблемы есть замечательное слово: гарантия.

Для 32 ГБ 4 ошибки за день это чрезмерно много (должно быть около 0) и свидетельствует о проблемах с настройкой системы или битом железе. В такой же ситуации с ECC следует понимать, что шанс на более чем 1 одновременную ошибку - тоже очень не нулевой.

sherbinko

03.10.2021 20:55+1Никто не гарантирует корректную работу не-ECC памяти. Поэтому гарантия не поможет.

Согласно статистике, космическое излучение вызывает 4 переключения битов в день и это не много, а самый что ни на есть стандарт.

Если бы бы жил в Гималаях или Андах, ошибок я думаю было бы больше.

Понятно, что не все эти 32 G заняты данными и значимы, но тем не менее ...

edo1h

03.10.2021 22:47+1Согласно статистике, космическое излучение вызывает 4 переключения битов в день и это не много, а самый что ни на есть стандарт.

напомню, что стандартный ECC гарантированно обнаруживает и исправляет один искажённый бит в блоке из 72 бит (64 полезных), гарантированно же обнаруживает (но уже не может исправить) 2 искажённых бита.

блоки с большим числом искажённых бит могут ошибочно быть приняты за верные, но вероятность этого достаточно мала (если я правильно понимаю, не больше 1/256).

то есть нулевое число ошибок ECC в мониторинге фактически говорит о том, что искажений в читаемых из памяти данных не было.так вот, мой опыт не подтверждает вашу статистику: перед глазами десятки серверов с суммарно несколькими терабайтами памяти, на которых ECC за всё время эксплуатации не обнаруживает ни одной ошибки.

есть, разумеется, и сервера, на которых такие ошибки обнаруживаются, но пока все случаи обнаружения ошибок были типа «раньше ошибок совсем не было, сегодня начали сыпаться» и решались заменой оборудования (что никак не может быть объяснено космическими лучами).

sherbinko

04.10.2021 01:13+1Очевидно под ошибками вы понимаете неисправленные ошибки (с 2-ми дефектными битами), иначе непонятно как вы умудрились ни одну исправленную поймать, вы же не в свинцовом саркофаге сервера держите.

Так что, сколько у вас исправленных ошибок - непонятно, очевидно их количество не может быть равно 0. В обычной памяти они бы привели к сбоям.

edo1h

04.10.2021 01:54+1Очевидно под ошибками вы понимаете неисправленные ошибки (с 2-ми дефектными битами),

нет, считаются все ошибки, вот вам пример с сервера с ошибками:

# edac-util -v mc0: 0 Uncorrected Errors with no DIMM info mc0: 0 Corrected Errors with no DIMM info mc0: csrow0: 0 Uncorrected Errors mc0: csrow0: mc#0csrow#0channel#0: 0 Corrected Errors mc0: csrow0: mc#0csrow#0channel#1: 0 Corrected Errors mc0: csrow1: 0 Uncorrected Errors mc0: csrow1: mc#0csrow#1channel#0: 0 Corrected Errors mc0: csrow1: mc#0csrow#1channel#1: 0 Corrected Errors mc0: csrow2: 0 Uncorrected Errors mc0: csrow2: mc#0csrow#2channel#0: 0 Corrected Errors mc0: csrow2: mc#0csrow#2channel#1: 405 Corrected Errors mc0: csrow3: 0 Uncorrected Errors mc0: csrow3: mc#0csrow#3channel#0: 0 Corrected Errors mc0: csrow3: mc#0csrow#3channel#1: 0 Corrected Errorsвы же не в свинцовом саркофаге сервера держите.

я думаю, что вы слишком близко к сердцу принимаете проблему космических лучей.

sherbinko

04.10.2021 03:29я думаю, что вы слишком близко к сердцу принимаете проблему космических лучей.

Вы думаете или знаете?

According to an Advanced Micro Devices, Inc. (AMD) study on soft error rates (SER), “a typical SER might be one bitflip per 2-4 weeks per gigabyte of DRAM.

Есть похожие статьи от гугла, церна со статистикой.

То что показывает 0 ошибок имхо может означать, что память простаивает и нет необходимости что-то проверять или корректировать.

Civil

04.10.2021 10:46Вы не учитываете условия и что старые статьи (статья гугла это 2009 год) не разделяла типы сломанного железа (ошибки контроллера памяти принимались за ошибки планки памяти). Есть более новая статья Facebook'а где эта проблема в методологии исправлена. И с ее учетом (после исключения из данных тех железок, где были проблемы с другими частями железа) выходит примерно 1 CE в 3 с небольшим дня на сервер (не на гигабайт).

И эта статистика в общем-то коррелирует с тем, что я наблюдал на прошлых работах (когда проблемы с железом были в моей зоне ответственности, статистики там конечно не так много - сотни и в лучшем случаи тысячи серверов и в среднем 128 ГБ всего оперативки на сервер).

Civil

04.10.2021 12:47Легко. Всю статью читать не обязательно важные выдержки следующие:

correctable errors among machines at the end of this section. To compare against prior work, we measured the correctable error incidence rate over the course of twelve months (7/13 up to and including 7/14, excluding 1/14) and found that, cumulatively across all months, around 9.62% of servers experience correctable memory errors. This is much lower than the yearly correctable error incidence rate reported in work from the field seven years ago

Figure 2 (left) shows the distribution of correctable errors among servers that had at least one correctable error. The x axis is the normalized device number, with devices sorted based on the number of errors they had during a month. The y axis shows the total number of errors a server had during the month in log scale. Notice that the maximum number of logged errors is in the millions. We observe that a small number of servers have a large number of errors. For example, the top 1% of servers with the most errors have over 97.8% of all observed correctable errors

However, if we examine the error rate for the majority of servers (by taking the median errors per server per month), we find that most servers have at most 9 correctable errors per server per mont

То есть на базе этого - для работоспособного железа 9 CE в месяц или 1 ошибка примерно раз в 3 дня.

В целом советую почитать исследование, оно обстоятельное и чуть ли не первое, которое пытается корректно отделить ошибки памяти от ошибок всего остального (например контроллера памяти). Чего не было в той работе, на которую Вы ссылались.

edo1h

04.10.2021 16:07+1То есть на базе этого — для работоспособного железа 9 CE в месяц или 1 ошибка примерно раз в 3 дня.

не совсем.

To compare against prior work, we measured the correctable error incidence rate over the course of twelve months (7/13 up to and including 7/14, excluding 1/14) and found that, cumulatively across all months, around 9.62% of servers experience correctable memory errors

у более чем 90% серверов за год не было ни одной ошибки, все остальные подсчёты (медианные 9 ошибок в месяц) относятся к серверам у которых ошибки были.

ИМХО в этом случае надо не считать ошибки, а менять железо )

Civil

04.10.2021 17:43Блин, я что-то когда читал этот момент упустил. Спасибо за поправку. Так что да, еще меньше выходит.

sherbinko

05.10.2021 20:27То есть на базе этого - для работоспособного железа 9 CE в месяц или 1 ошибка примерно раз в 3 дня.

Здесь вы просто выкинули сервера с большим количеством ошибок и после этого считаете среднее. Нормально, чо. Очень качественный подход :D. Очевидно, что на самом деле среднее арифметическое и даже геометрическое будет выше.

В самой статье, кстати, написано, что на 56 процентах серверов ошибки были Spurious, например, из-за излучения. И, кроме того, на "сбойных" серверах Spurious ошибки тоже могли быть, но они их не считали.

Если сервер не использует память и все его 128G простаивают или просто только пишут в память, но не читают, то никакой ошибки мы в этом случае не поймаем.

Или я ошибаюсь и контролёр памяти сам периодически опрашивает ячейки для проверки контрольной суммы?

Если же ошибки ловятся только когда софт пытается их прочитать, то какая ценность от этой статьи для оценки влияния излучения? Надо закреплять планки на стенде и гонять тесты.

edo1h

05.10.2021 21:38Здесь вы просто выкинули сервера с большим количеством ошибок и после этого считаете среднее. Нормально, чо. Очень качественный подход :D. Очевидно, что на самом деле среднее арифметическое и даже геометрическое будет выше.

нет же. сначала они выкинули >90% серверов, на которых ошибок не было вообще, потом на оставшихся посчитали медианное количество ошибок. что должно символизировать полученное число я не понимаю.

и да, выбрасывание серверов с большим количеством ошибок у меня не вызывает протеста: какой смысл их учитывать, очевидно же, что в их случае дело не в активности космических лучей, а в банальной неисправности оборудования.

а вот выбрасывание серверов без ошибок… иначе как желанием высосать статью из ничего я объяснить не могу. ибо с их учётом получается, что на исправном оборудовании вероятность ошибки << 1 в год, и именно эти ошибки мы можем попытаться связать с космическим излучением (но только попытаться, это лишь одна из множества причин, которые могут вызвать ошибки).

Или я ошибаюсь и контролёр памяти сам периодически опрашивает ячейки для проверки контрольной суммы?

такая опция есть, обычно называется patrol scrubbing. в статье написано, что на некоторых серверах она была включена.

ЕМНИП зависимость количества ошибок от этой опции в статье не изучалась.Если сервер не использует память и все его 128G простаивают или просто только пишут в память, но не читают

ну это не то, чтобы принципиально невозможный, но крайне маловероятный вариант.

Civil

06.10.2021 09:02+1Здесь вы просто выкинули сервера с большим количеством ошибок и после этого считаете среднее. Нормально, чо. Очень качественный подход :D. Очевидно, что на самом деле среднее арифметическое и даже геометрическое будет выше

Моя ошибка в другом - я выкинул 90% серверов где было 0 ошибок.

Хотя на базе этого можно сказать, что космическое излучение вызывает меньше 1 ошибки в 14 месяцев. (Насколько меньше- нужно знать количество серверов).

То есть все ошибки памяти - это строго брак железа.

Ну и среднее арифметическое по опредению бесполезно в такого рода исследованиях, о чем там пара абзацев и есть (оно склонно переоценивать вклад единичных выбросов, то есть в случае статьи это сервера с серьёзно побитой памятью)

beeruser

05.10.2021 16:38так вот, мой опыт не подтверждает вашу статистику: перед глазами десятки серверов с суммарно несколькими терабайтами памяти, на которых ECC за всё время эксплуатации не обнаруживает ни одной ошибки.

Так ваш опыт тоже даёт сильно специфическую картину мира.

Вы смотрите на планомерно обслуживаемые серверы с отобранной памятью одного вендора, работающей на стоковой частоте в тепличных условиях.

Это совсем другая ситуация по сравнению с тем, что имеют обычные юзвери.

В частности разработчики онлайн игр сталкиваются со всем зоопарком, собранным неизвестно из каких комплектующих, в т.ч. с разогнанными системами. В итоге ошибки памяти — частый гость. Банально, прилетает дамп, а там битик в команде перехода поменялся на противоположный и переход выполняется по другой ветке.

Маркетинг Интел настолько тупорылый, что они лишают ECC памяти людей, которым она на самом деле нужна =)

edo1h

05.10.2021 17:50лишают ECC памяти людей, которым она на самом деле нужна =)

вы напрасно пытаетесь меня переубедить, я уже написал в соседнем комментарии, что мой следующий домашний компьютер будет с ecc.

просто я не хочу передёргивать и пугать массовыми битфлипами.

проблемы cо стабильностью работы памяти есть, но, как я опять же писал ранее, они больше не в том, что стабильная работа памяти без ECC невозможна, а в том, что без ECC сложно понять стабильно работает память или нет.P. S. видимо, таких как я недостаточно много, чтобы создать достаточный спрос на десктопные компьютеры с ECC.

amartology

05.10.2021 16:47+2(что никак не может быть объяснено космическими лучами).

Как специалист по космическим лучам и их взаимодействию с микросехмами, могу подтвердить, что четыре ошибки в день в 30 Гбайт на уровне моря не могут объясняться космическими лучами. Такого рода цифры возможны только высоко в горах или на самолетах.

sherbinko

05.10.2021 20:34Какая норма будет для 32G?

amartology

05.10.2021 20:58+1Разумный уровень — где-то в районе 1e-12 upset/bit/day, то есть для 32 Гбайт памяти, выставленной чипами на свежий воздух на уровне моря, стоит ожидать цифры порядка одного сбоя в четыре дня. Если память находится в корпусе ПК, то можно смело увеличивать время ожидания на порядок. Если в корпусе ПК в помещении — то может и на два порядка.

Civil

04.10.2021 10:44+1Никто не гарантирует корректную работу не-ECC памяти.

Гарантирует закон. 4 бит-флипа в сутки - повод обратиться в гарантийку, вам не откажут и новая память будет работать лучше. Так было всегда и так остается до сих пор. Для не-ECC памяти должно быть строго меньше 1 бит-флипа в сутки.

Согласно статистике, космическое излучение вызывает 4 переключения битов в день и это не много, а самый что ни на есть стандарт.

Согласно современной статистике меньше 1 бит-флипа в день. В зависимости от исследования люди замечали от 1 ошибки в 2 дня (технически в 41 час) до 9 ошибок в месяц, на современном железе (1 ошибка в 3 дня).

sherbinko

04.10.2021 12:07Понятно, значит мои данные устарели. А что за закон, на который вы ссылаетесь?

К счастью, эти битфлипы легко проверить. Я написал простенькую программку, с огромным массивом на 2 миллиарда 64-bit integer-ов. Было бы интересно воочию увидеть хотя бы один битфлип )

Civil

04.10.2021 12:54А что за закон, на который вы ссылаетесь?

Обычный закон о защите прав потребителя в стране вашего проживания. 4 ошибки в день если вы их можете показать - основание для гарантийного случая (строго говоря 1 ошибка в день тоже), так как устройство нерабочее и если дело дойдет до суда то суд вы выиграете без проблем.

К счастью, эти битфлипы легко проверить. Я написал простенькую программку, с огромным массивом на 2 миллиарда 64-bit integer-ов. Было бы интересно воочию увидеть хотя бы один битфлип )

Строго говоря memtest такое умеет. Обычно для пользовательского железа достаточно воспроизводимых результатов на 24-х часовом прогоне теста, чтобы сервис-центр признал это проблемой.

sved

04.10.2021 13:144 ошибки в день если вы их можете показать - основание для гарантийного случая (строго говоря 1 ошибка в день тоже), так как устройство нерабочее и если дело дойдет до суда то суд вы выиграете без проблем.

Почему именно такие цифры? Это в законе написанно?

Civil

04.10.2021 13:33Почему именно такие цифры? Это в законе написанно?

Спросите у автора выше, я использовал его пример с 4-я ошибками в день.

Про 1 ошибку за сутки - если обращаться по гарантии к производителям памяти напрямую это примерно практическая граница когда они готовы поменять модули памяти без вопросов (речь идет о десктопных модулях). Так строго говоря я не удивлюсь, если по закону даже 1 ошибка за неделю будет основанием для гарантийного случая, если ты сможешь доказать что причиной ее возникновения является память.

edo1h

03.10.2021 04:08+1Почему не нужен? В моих 32 G возникает в среднем 4 ошибки за день (по статистике).

а как вы посчитали?

по серверам с ECC могу сказать, что норма — работа без ошибок, если появляется хотя бы ошибка в месяц, то модуль надо менять.проблема десктопов без ECC не в том, что на исправной памяти возникают ошибки, а в том, что:

- неисправная память встречается не так уж и редко;

- некогда исправная память может со временем стать неисправной;

- диагностика памяти — это многочасовые тесты, во время которых компьютером обычно нельзя пользоваться;

- каких-то специфичных симптомов, говорящих о том, что память надо бы протестировать, нет (симптомами могут быть и редкие вылеты программ, и зависания/перезагрузки, и порча файлов — всё это может вызываться кучей разных причин).

Дома ECC не то чтобы нужен обычным пользователям.

мне нужен. именно потому, что я хочу работать на компьютере, не не тестировать сутками память.

BugM

03.10.2021 04:13DDR5 только ECC. Проблема уже решена. Осталось подождать лет 10.

edo1h

03.10.2021 04:16увы, AFAIK не решена — в DDR5 ECC в памяти работает независимо от процессора, о скорректированной ошибке он просто не узнает.

хотя, возможно, как-то статистику ошибок с модулей памяти можно прочитать, есть же сейчас SPD, почему его нельзя расширить?

BugM

03.10.2021 04:28Лично не сталкивался, и даже стандарт не читал полностью.

Но почему совсем независимо? Логично улучшить то что есть. А сейчас об ошибках ECC узнать можно. Зачем убирать эту возможность?

edo1h

03.10.2021 06:58так никто и не убирает, опциональный ECC сохраняется в том же виде, что и был. и всё так же остаётся опциональным.

Civil

04.10.2021 10:59+1Не надо путать on-die ECC с side-band ECC, почитайте небольшой обзор. Первое - да, будет в DDR5, так как первый покрывает бит-флипы в рамках чипа, но не в рамках передачи данных (когда про память говорят ECC то это именно inline ECC).

Осталось подождать лет 10.

Интеловский Alder Lake с DDR5 будет в этом году, AMDшный Zen 4 по слухам в начале следующего. Это таки меньше 10 лет.

sherbinko

03.10.2021 20:57по серверам с ECC могу сказать, что норма — работа без ошибок, если появляется хотя бы ошибка в месяц, то модуль надо менять.

На так о том и идёт речь - если нужно 0 ошибок, то нужно ECC. Без ECC ошибки неизбежны

edo1h

03.10.2021 21:44+1нет, опять не то.

я пытался сказать, ECC ценно в первую очередь не исправлением, а обнаружением ошибок.

Civil

04.10.2021 10:54+1мне нужен. именно потому, что я хочу работать на компьютере, не не тестировать сутками память.

Ну так и не тестируйте. Для домашнего использования ошибки памяти достаточно редки, что ими можно пренебречь.

каких-то специфичных симптомов, говорящих о том, что память надо бы протестировать, нет (симптомами могут быть и редкие вылеты программ, и зависания/перезагрузки, и порча файлов — всё это может вызываться кучей разных причин).

И да и нет - когда система была стабильна, а потом перестала - это повод усомниться в качестве оперативной памяти. Опять же это случается не так часто, чтобы на этот счет волноваться в рамках единичных компьютеров.

edo1h

04.10.2021 15:25Для домашнего использования ошибки памяти достаточно редки, что ими можно пренебречь.

вот буквально этим летом столкнулся с ошибками на домашнем компьютере, определение сбойного модуля, потом тестирование после замены — на это ушло в сумме не меньше 2 дней.

И да и нет — когда система была стабильна, а потом перестала — это повод усомниться в качестве оперативной памяти.

после любого вылета программы запускать суточный тест памяти?

нет, понятно, что с этим можно жить, но я давно решил для себя, что следующий домашний компьютер будет с ECC памятью.

Civil

04.10.2021 15:45после любого вылета программы запускать суточный тест памяти?

Если прям есть уверенность в безбажности софта - то не такой и плохой вариант. Так у подсистемы памяти характерная проблема в том что софт вылетает случайны и случайным образом и чаще всего всегда чуть по-разному (включая выдачу некорректных результатов).

вот буквально этим летом столкнулся с ошибками на домашнем компьютере, определение сбойного модуля, потом тестирование после замены — на это ушло в сумме не меньше 2 дней.

Да, это не очень удобно и не очень приятно, но я для себя не вижу проблем потратить два дня раз в несколько лет (я за несколько десятков лет владения ПК и ноутами помню ровно три случая неожиданных проблем с памятью (один раз было неприятно, на рабочем ноуте, но довольно очевидно - бит-флипы приводили к изменению текста в том числе в dmesg :), но так как это был ноут с распаяной памятью я так никогда и не узнал это память или что-то еще было виновато), а один раз проблемы были ожидаемы (умерший БП с искрами и дымом, который повредил вообще почти все, включая память, процессор и мать и половину жестких дисков).

В принципе еще лайф-хак - это махнуть память с какой-нибудь соседней системой, если возникли подозрения на проблемы. Иногда бывает проще чем гонять мем-тест.

AlexAV1000

04.10.2021 12:14Приветствую. Подскажите, где в системе посмотреть статистику, по ошибкам в ECC памяти?

edo1h

04.10.2021 15:47в серверах в веб-интерфейсе BMC обычно есть. или можно получить через ipmi лог ошибок, что-то вроде

ipmitool sel elistили в линуксе (уже не требует ipmi):

edac-util -vв windows тоже как-то можно, windows-машин без ipmi у меня нет, поэтому не смотрел.

BugM

03.10.2021 03:38+2NB: Я не являюсь специалистом в разработке процессоров. Хотя диплом на эту тему есть.

Я удивлен почему разработчики Эльбруса так провалили JIT подход. Казалось бы он идеален для них. Берем профиль с рантайма и оптимизируем код под ядро которое отлично умеет работать с оптимизированным кодом, но плохо работает со всем остальным. Профиль можно собирать сколь угодно долго, сохранять и использовать при следующих запусках. Хоть нейронки в оптимизатор прикручивай. Для general purpose софта крутящегося в проде годами и десятилетиями все расходы на рантайм оптимизацию все равно незаметными выйдут.

Из проблем видна проблема параллелизации алгоритмов (на уровне инструкций) и проблема сложности оптимизатора. И та и другая проблемы выглядят решаемыми. Сложно, местами очень сложно. Но ничего запрещенного математикой нет.

Потенциальный объем рынка для процессора для JIT софта безграничен. Деньги тут есть.

Armmaster Автор

03.10.2021 16:15Потому что хороший JIT очень непросто сделать, особенно в условиях Эльбруса. Да и долгое время была же концепция статического планирования. А делать JIT это фактически признать, что статический подход не работает. Но тогда логичный вопрос, зачем делать в софте то, что проще и эффективнее делать в железе? Это если кратко.

checkpoint

03.10.2021 04:03+2Хочу попросить автора статьи рассказать как в Эльбрусе осуществляется переключение контекста при работе в многозадачных ОС (Linux), а именно - что происходит с его регистровым файлом в котором 256 регистров. Логика посдказывает, что переброс такого объема данных в стек и обратно при переключении задач обходится не бесплатно.

Sabubu

03.10.2021 14:39+1Тормоза при переключении контекста (по крайней мере на Интел x86) обычно возникают не из-за необходимости выгружать регистры в стек, а из-за опустошения кешей данных, инструкций и TLB.

Выгрузка регистров в стек это операция последовательной записи и память при ней работает более-менее в оптимальном режиме.

checkpoint

03.10.2021 22:10На сколько я понимаю, выгрузка регистров в стек осуществляется через кеш всех уровней, что при уже совсем небольшом числе задач (нитей) приведет к загрязнению кеша (cache thrashing). Или же в системе команд Эльбруса имеется спец инструкция для выгрузки/загрузки блока регистров минуя кеш ? Если нет, то мы должны наблюдать интресный эффект - как только число задач превысит опредленный порог, произвоительность системы должна резко упасть, так как постоянная выгрузка/загрузка регистров будет опустошать кеш до такого состояния, что он будет непрерывно синхронизироваться с медленной памятью. Мне бы хотелось проверить это на пратике. К сожалению, доступа к машине с Эльбрусом сейчас нет.

Armmaster Автор

03.10.2021 22:29+1Можно выгружать регистры в память специальной операцией записи, минуя кэши. Но это приводит к другой проблеме - при переключении контекста обратно, придётся доставать их из памяти, что небыстро. Вообще, скорость переключения контекста в Эльбрусе это известная проблема. Кто-то на Elbrus Tech Day даже цифры приводил, по-моему. Можете там поискать, если очень интересно.

Armmaster Автор

03.10.2021 16:17+1Не бесплатно. Поэтому(и ещё из-за сложности ШК) обработка прерываний и переключения контекста на Эльбрусе существенно медленнее, чем на Risc/Cisc процессорах

unv_unv

03.10.2021 09:20+7Максим, очень жаль, что вы никак не отреагировали на разбор вашего реального примера с компиляцией внутреннего цикла из сортировки со вставками под Эльбрус. Вы и ваши единомышленники в комментариях утверждали, что скомпилированный вами результат в 13 тактов на итерацию является принципиально неустранимым недостатком эльбрусовского компилятора.

Однако пользователи antag и Дмитрий Щербаков разобрали данный фрагмент (https://habr.com/ru/post/576420/comments/#comment_23456356). Сначала оказалось, что с опцией оптимизации -O2 внутренний цикл компилируется уже в код с 7 тактами на итерацию (вы ещё забыли включить другую рекомендуемую для Эльбруса оптимизацию -ffast). Далее оказалось, что эвристика компилятора неверно определила цикл как выполняющийся с небольшим количеством итераций, что можно было обойти, добавив в исходник комментарий с подсказкой для компилятора — и в итоге внутренний цикл скомпилировался в код, выполняемый за 1 такт — втрое быстрее, чем код для Intel/AMD.

И очень разочаровывает, что вы ни в той статье не добавили Post Scriptum с указанием на этот разбор, ни в этой статье не обмолвились. При том, что это можно было хорошо обыграть в вашей парадигме — дескать, вот какие танцы с бубнами нужны, чтобы хорошо скомпилировать простую сортировку. Но даже это не интересно, не интересна реальность — интересны теоретические рассуждения в вакууме. Вот вы претендуете в своих текстах на поиск истины, а по факту оказывается, что истина не интересует, а интересует лишь пропаганда.

Armmaster Автор

03.10.2021 16:39+6является принципиально неустранимым недостатком эльбрусовского компилятора.

Нет, я не это утверждал, вы невнимательно читали статьи. Я утверждал, что принципиально невозможно эффективно откомпилировать код для Эльбруса без профиля (да и с профилем многие проблемы остаются). И чтобы добиться вменяемого перфа, надо лезть руками в код, его анализировать и оптимизировать. Что данный пример как раз отлично демонстрирует. Это был ответ на рассуждения Алексея, что в реальности всё неплохо, когда в реальности мы простейшую сортировку соптимизировать нормально.

Сначала оказалось, что с опцией оптимизации -O2 внутренний цикл компилируется уже в код с 7 тактами на итерацию (вы ещё забыли включить другую рекомендуемую для Эльбруса оптимизацию -ffast).

Всё это прекрасная демонстрация моих тезисов. Компилятор на -O4 генерирует код хуже, чем на -O2, а должно быть наоборот. А происходит это потому, что компилятор не понимает, какие участки надо реально оптимизировать, и начинает гадать.

- ffast я специально не включал, потому что она включает некоторые не совсем корректные оптимизации и ей часто не пользуются по данной причине. Да и в контексте данного примера она ни на что не должна влиять особо

Далее оказалось, что эвристика компилятора неверно определила цикл как выполняющийся с небольшим количеством итераций, что можно было обойти, добавив в исходник комментарий с подсказкой для компилятора

И снова прекрасная иллюстрация моей позиции - даже здесь компилятор не смог понять, что происходит (и это понятно, откуда ему знать?). Надо лезть в код и ставить подсказки.

втрое быстрее, чем код для Intel/AMD.

Насколько всё быстрее работает на мало мвльски реальном коде даже с подсказками (профилем) мы смогли увидеть на основе цифр Spec Cpu2017

При том, что это можно было хорошо обыграть в вашей парадигме — дескать, вот какие танцы с бубнами нужны, чтобы хорошо скомпилировать простую сортировку.

Мне казалось, что мой пример эту проблему и обыгрывает.

Вот вы претендуете в своих текстах на поиск истины, а по факту оказывается, что истина не интересует, а интересует лишь пропаганда.

Я ни на что не претендую, я лишь пытаюсь объяснить людям технические проблемы Эльбруса, из-за которых он не может и не сможет стать массовым gp cpu. А интересует меня одно - я хочу дожить до того момента, когда российские процессоры будут производиться в России десятками миллионов, а вести дискуссии на хабре я буду с компа с отечественным процом. И проблема в том, что если идти уже понятно что тупиковыми путями, то до такого момента могу не дожить не то, что я, но и мои дети

Thall

03.10.2021 19:40-3Хуавей не можем быть никак российским процессором )

Armmaster Автор

03.10.2021 19:40+1Хуавей здесь вообще непричём.

Thall

03.10.2021 23:04-3Я к тому что вы работает там ) ну либо в дочке его ядро ) поэтому и топите за риск 5 )

Armmaster Автор

03.10.2021 23:28+1Где я работаю и почему, можете спросить у Александра Кирыча. А то если я начну свою версию рассказывать, истории про проблемы архитектуры Эльбрус на этом фоне будут добрыми детскими сказками.

За Risc-V я не то, чтобы топлю. Я топлю за связку ARM-RISC-V на данном этапе. По той простой причине, что это объективно оптимальный вариант для России сейчас. Я бы с радостью поменял бы любую аббревиатуру на Эльбрус, но не привык заниматься самообманом. И всё вышесказанное никак не связано с тем, где и как я работаю.

Thall

04.10.2021 00:08-3Теперь я расскажу как это выглядит в моих глазах , аккаунт был зарегистрирован в 2014 году и был мертвым , с 2021 начали выходить ролики с Эльбрусом с просмотрами по 500 и более тысяч и тут бац и появился бывший сотрудник мцст который работает в другом месте и задвигает про Эльбрус … ну а дальше пусть люди сами размышляют что и как ) .

Armmaster Автор

04.10.2021 00:45+4Из перечисленных фактов можно напридумывать всё, что угодно. У вас есть что сказать по существу?

amartology

04.10.2021 12:20А как так вышло, что принадлежащая Алишеру Усманову компания Yadro у вас стала дочкой Huawei? Это Huawei тоже принадлежит Усманову, или Усманов принадлежит Huawei?

В первом случае Эльбрус не нужен, потому что Усманов с таким активом очень скоро решит вообще все проблемы российской микроэлектроники. Во втором случае, в общем, тоже.

А вот если Yadro и Huawei никак не связаны, то сотруднику Huawei нет никаких причин вставать на чью-то сторону в борьбе МЦСТ и Ядра.

bircoph

03.10.2021 23:17+3Исходный автор статьи перегибает палку и приукрашивает ОоО, мы это уже обсуждаем в соседних комментариях. Но и Вы, увы, лукавите и перегибаете палку.

Сначала оказалось, что с опцией оптимизации -O2 внутренний цикл компилируется уже в код с 7 тактами на итерацию (вы ещё забыли включить другую рекомендуемую для Эльбруса оптимизацию -ffast).

Ну давайте вместе почитаем документацию к -ffast из man lcc:

-ffast Включает опции -fstdlib, -faligned, -fno-math-errno, -fno-signed-zeros, -ffinite-math-only, -fno-rounding-math, -fcx-limited-range. -fprefetch, -fmalloc-opt, -floop-apb-conditional-loads, -fstrict-aliasing, -fext-strict-aliasing. Данная опция выключена по умолчанию, поскольку включает преобразования с вещественной арифметикой, которые могут приводить к некорректным результатам в случае программ, предполагающих строгое соблюдение стандартов IEEE или ISO для вещественных операций и функций. Тем не менее, она может существенно увеличить скорость программ, не требующих строго соблюдения этих стандартов. Кроме того, опция включает некоторые потенциально опасные оптимизации (такие как loop-apb для чтений под условием, malloc-opt, удаление операций целочисленного деления), которые в определённых случаях могут приводить к некорректному поведению программы.А заодно и -faligned, взводимого -ffast:

-faligned (-fno-aligned) Разрешить оптимизации, рассчитывающие исключительно на выровненные обращения в память. Смысл опции заключается в том, что программист как бы говорит компилятору "я обязуюсь, что в исходнике программы все обращения в память являются выровненными на свой формат", в результате чего компилятор может более эффективно выполнять некоторые оптимизации. Такими оптимизациями являются: apb (аппаратная подкачка массивов) и arracc (аппаратная поддержка доступа к массивам) для архитектур до elbrus-v4 включительно, автоматическая векторизация (в небольшой степени) и crp_opt (динамический разрыв зависимостей между чтениями и записями в память). Необходимость в данной опции вызвана аппаратными особенностями Эльбруса. В архитектурах до elbrus-v5 включительно невыровненные обращения в память работают значительно медленнее выровненных. В архитектурах до elbrus-v4 включительно аппаратная подкачка массивов не умеет работать по невыровненным адресам; в elbrus-v5 это ограничение снято для всех операций, кроме 16-байтных; начиная с elbrus-v6 ограничение снято полностью. Таким образом, для elbrus-v6 и выше опция -faligned имеет смысл только для оптимизации crp_opt. Использование опции -faligned при компиляции программы, содержащей невыровненные обращения в память, может привести к некорректному поведению программы. Для проверки выровненности обращений в память можно использовать опцию -faligned-check По умолчанию для языков C/C++ включен режим -fno-aligned, для Фортрана -falignedПо-моему, совершенно очевидно, что эта -ffast применим лишь в очень узких, специфических случаях; скорее всего, на специализированных числодробилках. А остальной софт будет страдать. Попробуйте собрать с -ffast, скажем, firefox.

рекомендуемую для Эльбруса оптимизацию -ffast

Ввиду выше процитированной официальной документации lcc, Ваше утверждение о рекомендуемости -ffast выглядит как издёвка. Да, это сильная оптимизация, но она ломает код, если не выполняется большое количество ограничений и условия. Так что называть её рекомендуемой — так себе рекомендация. Это полезно учитывать при написании кода под Эльбрус, но мало толку при адаптации уже существующего.

sabaca

03.10.2021 09:27+2Поэтому намного проще взять обычную RISC архитектуру и сделать на её основе современный процессор с ОоО-исполнением. Это будет проще, быстрее, дешевле, а в итоге получится более быстрый и удобный для пользователей процессор.

Спорное заявление. Сделать быстрый ОоО процессор совсем не просто и не дешево.

antag

03.10.2021 11:23+7При этом из предыдущих статей помним, что верхний предел микроархитектурной скорости на Эльбрусе, рассчитанный по данным запусков на Spec CPU2017, в 3-4 раза уступает современным RISC/CISC процессорам с ОоО исполнением.

Есть современный OoO процессор Ampere Altra. Для него есть результаты Spec CPU2017.

Сравниваем эту вашу "микроархитектурную скорость":

Ampere Altra: int: 1.20, fp: 0.875

Эльбрус-8СВ: int: 0.89, fp: 1.38

Так где тут 3-4 раза?

Для fp у эльбруса эта "микроархитектурная скорость" оказалась даже выше, чем у Altra Neoverse-N1. Или Neoverse-N1 - это тоже плохой представитель современного OoO процессора?

creker

03.10.2021 16:22-2Опять путаете карты, пересчитывая все на мегагерцы. Не нужно мутить воду, считайте на максимальных частотах. Altra действительно не самый лучший представитель. Последнее поколение амд эпик будет быстрее.

dubm