Напоминаю, что я продолжаю идти к цели — сделать свой собственный Отечественный Процессор (TM). Продолжение процесса разработки можно посмотреть под катом.

- Часть 1. Теория

- Часть 2. Установка программного обеспечения

- Будет доступна 09.12.21: Часть 3. Схемотехническое представление и Layout

- Будет доступна 10.12.21: Часть 4. DRC/LVS/PEX

Установка необходимых инструментов.

За основу возьмём Ubuntu 21.04. Если у вас другой дистрибутив рекомендую установить именно Ubuntu 21.04 в виртуалку. С другими дистрибутивами, либо версиями вы сами по себе.

Установите систему и проверьте, чтобы у вас было хотя бы 20GB свободного места в /opt

Я установил build-essential и VirtualBox extension, поскольку я установил систему в виртуальной машине.

ВАЖНО! Сохраняйте очерёдность

Я установил Docker

Я установил Magic VLSI и KLayout

Я установил Netgen

Затем я установил XSCHEM используя шаги снизу.

Я установил NGSPICE:

sudo apt install ngspiceИ напоследок я установил OpenPDK и caravel_user_project

Также мы рассмотрим работу транзисторов MOSFET и логику CMOS.

▍ Docker

Для установки Docker я использовал данный скрипт.

sudo apt-get update

sudo apt-get install \

apt-transport-https \

ca-certificates \

curl \

gnupg \

lsb-release

curl -fsSL https://download.docker.com/linux/ubuntu/gpg | sudo gpg --dearmor -o /usr/share/keyrings/docker-archive-keyring.gpg

echo \

"deb [arch=amd64 signed-by=/usr/share/keyrings/docker-archive-keyring.gpg] https://download.docker.com/linux/ubuntu \

$(lsb_release -cs) stable" | sudo tee /etc/apt/sources.list.d/docker.list > /dev/null

sudo apt-get update

sudo apt-get install docker-ce docker-ce-cli containerd.io

sudo groupadd docker

sudo usermod -aG docker $USER

Затем я перезагрузился и выполнил следующую команду, чтобы проверить Docker.

docker run hello-world # Run a test image

Источник

▍ KLayout

Для компиляции KLayout из папки /opt:

git clone -b v0.27.4 --depth 1 https://github.com/KLayout/klayout.git klayout-v0.27.4

sudo apt-get install gcc g++ make qtcreator build-essential python3 python3-dev libz-dev ruby ruby-dev

cd klayout-v0.27.4

./build.sh -qt5 -j2

Если у вас многоядерный процессор поменяйте -j2 на количество ваших процессорных потоков. К сожалению, у меня очень медленный процессор, поэтому сборка у вас точно займёт значительно меньше. Эта команда скомпилирует KLayout, для меня это процесс занял 2 часа. Но для того, чтобы запустить его вам нужно использовать следующую команду, поскольку линкер не знает местонахождения динамических библиотек:

LD_LIBRARY_PATH=/opt/klayout-v0.27.4/bin-release /opt/klayout-v0.27.4/bin-release/klayout -e -nn $PDK_ROOT/sky130A/libs.tech/klayout/sky130A.lyt -l $PDK_ROOT/sky130A/libs.tech/klayout/sky130A.lyp /home/armleo/Desktop/armleo_io/gds/armleo_io.gds

Учтите, что вы должны были выполнить

source sourceme.sh, до того, как вы запустите KLayout, иначе при запуске будет ошибка. Так же стоит указать правильный путь к .gds файлу, поскольку у вас он будет отличаться.Если Klayout запустился, то закрываем его и идём дальше. Если будут проблемы с библиотеками QT, в вашем дистрибутиве, то разберитесь сами как её установить.

Источники установка QT, сборка KLayout и документация по LD_LIBRARY_PATH.

▍ Magic VLSI

Для компиляции Magic VLSI из папки /opt:

sudo apt-get update && sudo apt-get upgrade

sudo apt-get install m4 tcsh csh libx11-dev libcairo2-dev mesa-common-dev libglu1-mesa-dev

git clone -b 8.3.227 https://github.com/RTimothyEdwards/magic magic-8.3.227

cd magic-8.3.227/

./configure

make && sudo make install

Учтите, что без ключа

-b 8.3.227 гит скопирует последний стабильный билд. Тут вы сами по себе, ибо весь код протестирован именно в этой версии.▍ Netgen

Для Netgen я использовал следующий скрипт:

git clone -b 1.5.210 https://github.com/RTimothyEdwards/netgen

cd netgen

./configure

make

sudo make install

У Netgen есть требования, которые были установлены во время установки Magic VLSI/KLayout. Инструкции я нашёл тут.

▍ NGSPICE

Для установки вполне подойдёт версия из репозитория Ubuntu. Если у вас другой дистрибутив удостоверьтесь, что ngspice имеет версию 34.

sudo apt install ngspice

▍ XSCHEM

Для XSCHEM я использовал следующий скрипт:

sudo apt-get install -y libx11-6 libx11-dev libxrender1 libxrender-dev libxcb1 libx11-xcb-dev libcairo2 libcairo2-dev tcl8.6 tcl8.6-dev tk8.6 tk8.6-dev flex bison libxpm4 libxpm-dev gawk

git clone -b 2.9.9 https://github.com/StefanSchippers/xschem.git

cd xschem

./configure

make

sudo make install

Источник

▍ Установка caravel_user_project.

Давайте скопируем репозиторий с изменениями, которые я опишу внизу. Из папки /opt запускаем следующие команды:

git clone https://github.com/armleo/habr_nand_sky130.gitЗа основу взял caravel_user_project_analog. Я создал

sourceme.sh с переменными. Переменные взял отсюда. Исходный код можно взять на GitHub-е вот тут.Затем я модифицировал

xschemrc, чтобы он ссылался на файл в папке $PDK_ROOT/xschemrc. Это необязательно, тем не менее далее туториал предполагает, что данное изменение уже сделано. Взглянуть на него можно тут.С репозиторием и его изменениями познакомились. Теперь к установке.

OpenPDKs и Google говорят, что они не будут предоставлять билды PDK, потому что «it's too big after it was built».

Все пути установки абсолютные, поэтому нужно установить его именно в папку /opt. В итоге у вас должна быть папка

/opt/pdk_root/sky130A/libs.tech. Проверьте его наличие. Если её нет, значит вы что-то сделали не так. Удостоверьтесь, что в папке Caravel есть файлы. Проблемы с символами резисторов исправлены в последней версии, но возможности собрать PDK с новыми символами у меня не было, поэтому рекомендую собрать PDK с нуля.Для того, чтобы собрать с нуля։

cd habr_nand_sky130

source sourceme.sh

make install

sudo chown -R $USER /opt/

make pdk-nonnative

Иногда pdk build вылетает с ошибкой. Для того, чтобы обойти этот баг, я использую коммиты, которые не содержат этого бага. Если пожалуется на Permission во время запуска докера, значит вы что-то сделали не так во время установки докера.

Давайте распакуем .gds файлы. Для того, чтобы распаковать .gds файлы:

make uncompressЧтобы упаковать .gds файлы, для того, чтобы отправить их в Гит репозиторий:

make compressНам нужны пока распакованные .gds файлы, так что вторую команду упаковки не нужно выполнять.

Установка OpenLane и тестовый запуск

export PDK_ROOT=/opt/pdk_root

Переходим в папку /opt и выполняем следующий шаг:

git clone -b 2021.08.17_03.26.57 --depth 1 https://github.com/The-OpenROAD-Project/OpenLane.git OpenLane_habr

sudo apt-get install python3-pip

python3 -m pip install pyyaml click

cd OpenLane_habr

make pull-openlane

Учтите, что это древняя версия OpenLane, если хотите установить новую версию, на гитхабе всё очень подробно описано.

Если у вас возникли проблемы в этом шагу, дальше идти не имеет смысла, поскольку у вас есть проблема в вашей установке.

PDK ранних версий, которые мы использовали наверху имеют несовместимости с OpenLane последних версий. А ещё в OpenLane, который я использовал есть баг, из-за чего у вас будут проблемы с таймингами, которые у вас не будут отображаться. Поэтому если вы захотите установить последнюю версию используйте скрипт внизу:

export PDK_ROOT=/opt/openlane_pdk_root

Устанавливаем, например эту версию:

git clone -b 2021.11.20_01.52.16 --depth 1 https://github.com/The-OpenROAD-Project/OpenLane.git OpenLane_habr

sudo apt-get install python3-pip

python3 -m pip install pyyaml click

cd OpenLane_habr

make pull-openlane

make pdk

Она скачает и установит последнюю версию + PDK доступную на момент публикации статьи. Если хотите получить САМУЮ последнюю стабильную версию уберите ключ -b 2021.11.20_01.52.16, но тут вы уже на свой страх и риск.

Наконец для того, чтобы запустить тест выполните:

make test

Если же у вас нет проблем мы увидим, что OpenLane сгенерировал нашу цифровую макро ячейку. Её можно найти в папке designs/spm/openlane_test/results/magic/spm.gds. Давайте откроем KLayout-ом наш .gds файл:

source /opt/habr_nand_sky130/sourceme.sh

LD_LIBRARY_PATH=/opt/klayout-v0.27.4/bin-release /opt/klayout-v0.27.4/bin-release/klayout -e -nn $PDK_ROOT/sky130A/libs.tech/klayout/sky130A.lyt -l $PDK_ROOT/sky130A/libs.tech/klayout/sky130A.lyp designs/spm/runs/openlane_test/results/magic/spm.gds

Видим результат:

В папке designs мы можем видеть, очень большое количество примеров, а документация очень подробно описывает все параметры. Да, OpenLane далёк от Fusion Compiler-а от Synopsys, но это первые, очень даже удачные, шаги Open-Source программного обеспечения, к тому, чтобы составить коммерческим инструментам конкуренцию.

Теперь перейдём, немного к теории, поскольку следующая статья будет уже практическая.

MOSFET транзисторы на пальцах

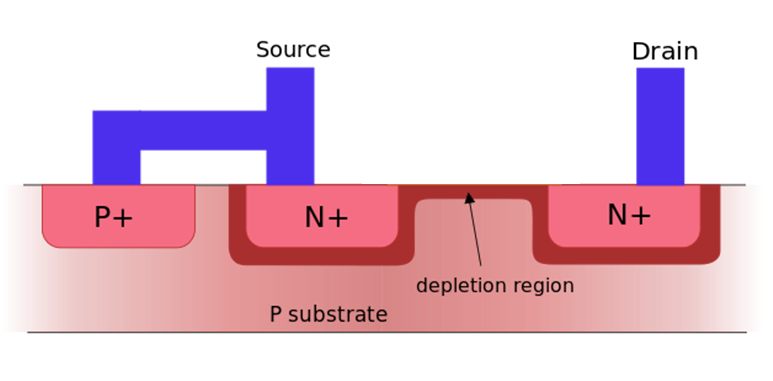

Как мы уже знаем, в микросхеме используются транзисторы, но как именно работает этот самый транзистор? Для этого возьмём NMOS транзистор. Как видим на картинке, NMOS состоит из трёх полупроводников: DRAIN, SOURCE, BULK и область между DRAIN и SOURCE.

Также мы можем заметить, что в регионе, который находится между DRAIN и SOURCE находится область с противоположным типом полупроводника. В случае NMOS области DRAIN и SOURCE имеют тип N, а область посередине имеет тип P. Очевидно, что если N тип имеет потенциал выше, чем P тип, то у нас образуется «закрытый» диод.

Если по какой-то причине на область P мы подадим электроны, то этот полупроводник начнёт проводить ток, ибо у нашего диода, почти равные (либо выше) потенциалы с полупроводником типа N. Таким образом управляя количеством электронов в области между DRAIN и SOURCE мы сможем управлять током, который проходит между DRAIN-ом и SOURCE-ом. Но, как именно этого достигнуть?

Для этого мы создаём очень тонкий слой диэлектрика, который состоит из оксида силикона (SiO2). Обычно для этого используется термическая обработка. Над этим тонким слоем диэлектрика, мы создаём металлический слой.

Если подать на этот металл называемый Gate-ом положительный заряд, то в полупроводнике, который находится прямо под Gate-ом образуется область с отрицательным зарядом, то есть скопление электронов, и как мы уже узнали, в этом случае между DRAIN-ом и SOURCE-ом образуется канал. Точка, когда количество электронов между DRAIN и SOURCE достигает равного значения с количеством «дырок» называется Vth.

Стоит отметить, что на самом деле «открытый» NMOS имеет два состояния, в зависимости от напряжения Drain-Source:

Также стоит отметить, что DRAIN и SOURCE у NMOS-ов симметричный, но SOURCE-ом обычно называют ножку, которая подключена к земле. У PMOS SOURCE-ом называется ножка, которая находится на линии питания.

Ещё стоит дополнить то, что значение напряжение BULK меняет характеристики транзистора. Подробнее можно узнать, загуглив Body effect.

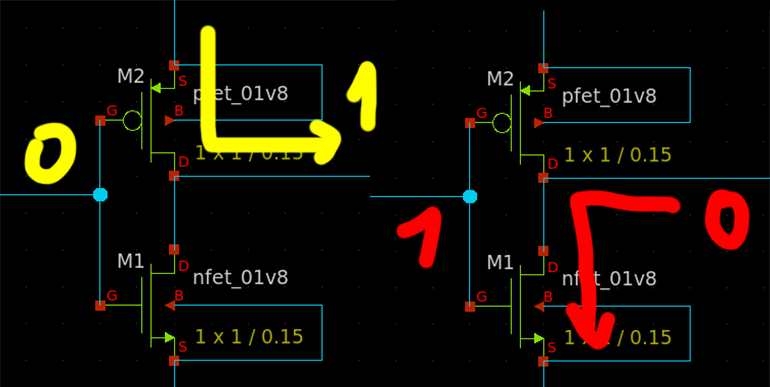

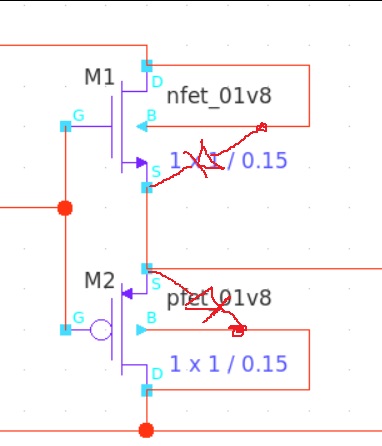

NMOS находится в открытом положении, когда значение Vgate-to-source ровно, либо больше, чем Vth. PMOS в отличие от NMOS состоит из двух полупроводников P типа и BULK, как и область между двумя P полупроводниками находится полупроводник N типа. Похожим образом работает PMOS, но PMOS находится в открытом состоянии только тогда, когда напряжение Vgate-to-source < Vth. Именно поэтому у транзистора NMOS символ не имеет кружочка над Gate-ом, а у PMOS-а этот кружочек присутствует.

Важно отметить, что всё это объяснение на пальцах ОЧЕНЬ не соответствует реальности. Если вас интересует физика, то рекомендую почитать книжки по этой тематике. Лично я запоминаю только объяснение на пальцах, ибо так проще.

CMOS логика на пальцах

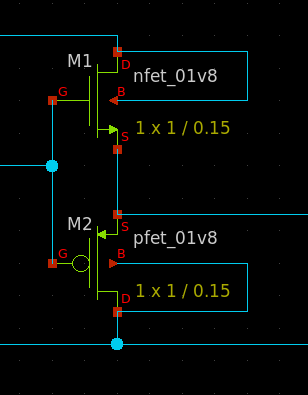

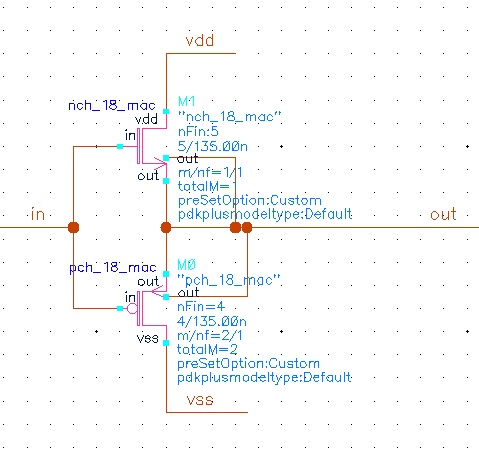

Мы научились управлять током используя транзистор, теперь давайте попробуем сделать из этого транзистора, что-то полезное. Например инвертор.

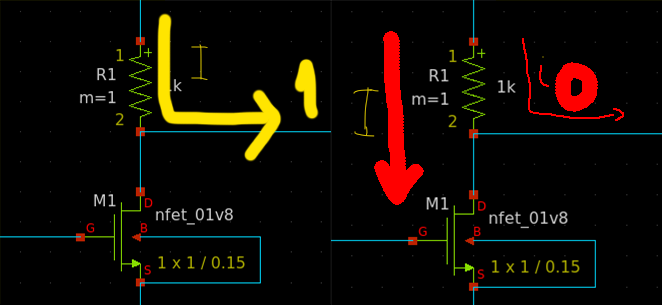

Возьмём транзистор NMOS и подключим резистор. Когда NMOS выключен, ток течёт из резистора в подключенный вход дальнейшей логики. Если включить NMOS подав на Gate напряжение — NMOS откроется и ток из резистора практически полностью пройдёт через транзистор к земле.

НО! Есть одна неприятная проблема. Ток через транзистор будет идти даже тогда, когда выход находится в нулевом состоянии. Ах, если бы у нас был бы транзистор, который бы закрывался, когда ты подаёшь на вход единицу… Он называется PMOS. Очевидно, что когда на входе единица, то PMOS выключен, и на выход подаётся нулевое значение, поскольку NMOS в свою очередь открыт.

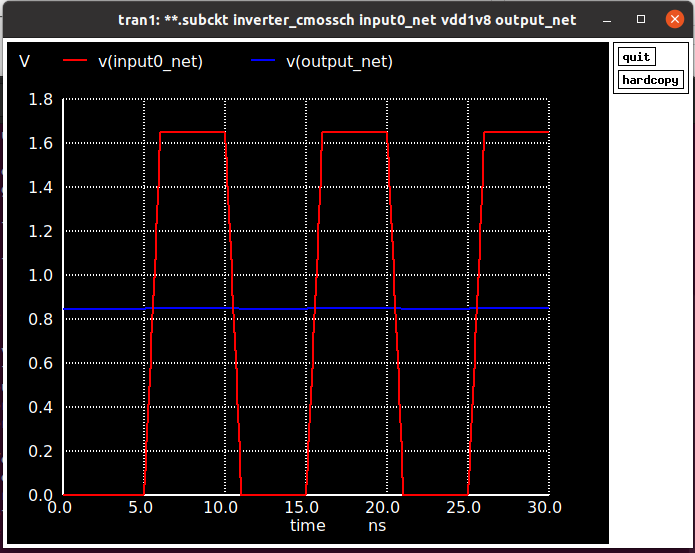

А давайте по той же логике сделаем буфер. Подключаем NMOS к VDD и PMOS к VSS. По нашей логике, когда на входе мы подадим единицу, то на выходе мы получим также единицу, круто получается, правда?

Симулируем и получается…

Эмм… Че-то у нас выходы имеют напряжение меньше, чем VDD и выше, чем VSS. Это связано с тем, что NMOS плохо проводят единицу, поскольку SOURCE-ом становится выход, и NMOS будет открыт до тех пор, пока Vgs выше Vth. Если Vsource (выход) достигает значения VDD-Vth, то транзистор закроется, оставив на выходе напряжение VDD-Vth, что очень плохо. Аналогично, для PMOS.

Как мы будем решать эту проблему? Давайте решим, что NMOS всегда подключен к нулю, а PMOS всегда будет подключён к единице. Идея отличная, но как нам сделать буфер используя эту логику?

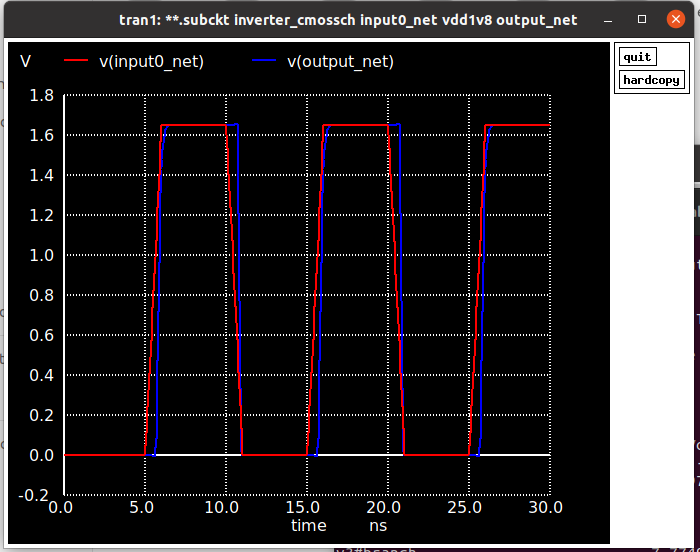

Помните булеву логику, две инверсии на выходе дают такое же значение, что и на входе. Давайте просто подключим два инвертора подряд:

Наконец-то!

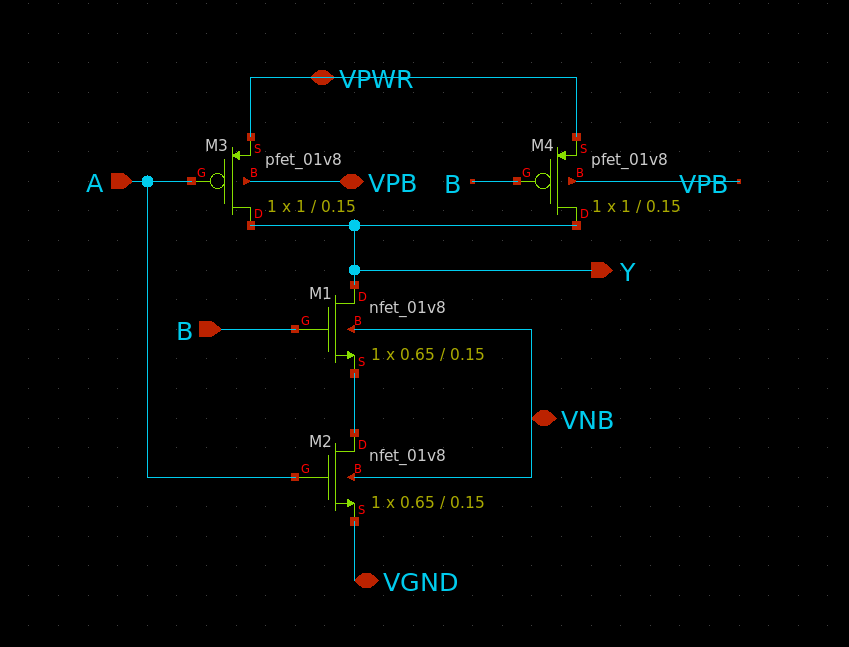

Ну научились мы делать инверторы и буферы, давайте сделаем простые логические ячейки вроде NAND и NOR.

Если подключить два NMOS последовательно, то земля на выход пойдёт, только когда оба входа имеют высокое напряжение. Также давайте подключим два PMOS параллельно. Если хотя бы один из транзисторов имеет на Gate значение ноль, тогда транзистор PMOS открыт, а значит на выходе находится единица.

Ничего не напоминает? Правильно, это NAND:

Получившееся схема:

Если вы поставите PMOS последовательно, а NMOS параллельно, очевидно у вас будет NOR.

У вас возникнет логичный вопрос: «Что если и NMOS, и PMOS будут открыты?». Ответ прост: ваша схема должна иметь такую структуру, чтобы NMOS и PMOS никогда не оставались одновременно открытыми на долгое время. Если вы нарушите это правило, ваша схема будет потреблять большой ток и нагреваться, а если оставить транзистор с большим током, то ваша микросхема скоро сломается из-за электромиграции.

В следующей статье рассмотрим схемотехническое представление и Layout.

Об автореМеня зовут Арман и я окончил институт Synopsys по профилю VLSI разработки микросхем. В основном я занимаюсь разработкой цифровых компонентов для микросхем и IP для ПЛИС. В прошлом я был программистом, писал бекенд на Node.js и разрабатывал под микроконтроллеры, но решил пересесть на что-то сложнее, попробовать себя, так сказать.

Я открыт к найму, поэтому, если вас интересует найм разработчика цифровых микросхем с тремя годами опыта и очень интересными проектами (Радио модемы, преобразователи интерфейсов, процессоры и очень многое), напишите мне в личку.

- Часть 1. Теория

- Часть 2. Установка программного обеспечения

- Будет доступна 09.12.21: Часть 3. Схемотехническое представление и Layout

- Будет доступна 10.12.21: Часть 4. DRC/LVS/PEX

Комментарии (18)

mikki33_2000

08.12.2021 23:04Там где "Симулируем и получается…" есть два открытых диода, поэтому выход получается 1/2 VDD

Можно по-другому подсоеденить балки и будет что-то похожее нв бафер. Вот так:

Только не забыть, что N транзистор нужно засадить в Deep NWell. В DC получается бафер.

Так выглядит выход как функция входа

А вот транзиент показывает, что N не проводит VDD, а Р не проводит VSS

Всем удачи в аутешествии по чип дизайну.

checkpoint

09.12.2021 00:44Там где "Симулируем и получается…" есть два открытых диода, поэтому выход получается 1/2 VDD

Там получается два закрытых диода. Эти диоды включены в обратном направлении и имеют высокое сопротивление, т.е. получается резисторный делитель напряжения. Такая схема включения используется для защиты входов микросхем от статики: https://blog.mbedded.ninja/electronics/circuit-design/esd-protection/

UPD: Аналогичным образом организуются резисторы подтяжек (pull-up/pull-down) - это диоды полученные из транзисторов включенных в обратном направлении (или пара встречных друг к другу). Если смотреть на дизайн цифровых микросхем с высоты, то все элементы в ней это транзисторы, меняя схему включения которых можно получить все остальные компоненты: диоды, резисторы, емкости.

mikki33_2000

09.12.2021 01:02два закрытых диода

Извините, но вы перепутали. Верхний транзистор - N типа и в нем P-Well это VDD, а N+ это выход (<VDD). И это значит, что диод открыт.

В схемах ESD - N-Well (или N+) всегда VDD и диоды закрыты при нормальной работе и открываются только когда входное напряжение превышает VDD на Vt.

checkpoint

09.12.2021 01:18Извините, но вы перепутали. Верхний транзистор - N типа и в нем P-Well это VDD, а N+ это выход (<VDD). И это значит, что диод открыт.

Да, пожалуй, Вы правы. В таком случе данная схема моментально "бахнет" при включении. :)

nixtonixto

09.12.2021 09:30+1Такая схема включения используется для защиты входов микросхем от статики

Это поразитные диоды, возникающие из-за того, что подложка МОСФЕТ электрически соединена с истоком. Конкретно от статики они защищают очень плохо, т.к. имеют низкую перегрузочную способность (у микросхем — десятки мА, когда ток разряда достигает десятка ампер), но от втекающего тока, способного вызвать тиристорный эффект, защищают хорошо.

amartology

09.12.2021 11:20+1Рабочий ток диодов пропорционален его размеру, и от защиты от статики регулярно применяются паразитные диоды, только очень большие.

amartology

09.12.2021 01:31Там где «Симулируем и получается…» есть два открытых диода, поэтому выход получается 1/2 VDD

Вы предположили, что на схеме снизу земля, а сверху питание. На обсуждаемом рисунке этого нет)

UPD виноват, нет на рисунке, есть в тексте. А я уже на автогенератор схеиматиков из нетлиста грешить начал, там и не такое в инверторе может быть.

Обсуждаемая схема, разумеется, прогорит очень быстро, но до этого будет вести себя так, как описано в статье, потому что сопротивление открытого транзистора очень мало, и он перетянет диод с другой стороны.

checkpoint

09.12.2021 00:23+1Все очень интересно, но что за "оксид силикона" ? ;)

Это связано с тем, что NMOS плохо проводят единицу, поскольку SOURCE-ом становится выход, и NMOS будет открыт до тех пор, пока Vgs выше Vth.

В такой схеме включения оба танзистора всегда будут закрыты: n-канальный МОП будет закрыт, так как потенциал на затворе всегда ниже потенциала на истоке, а p-канальный - потому, что потенциал на затворе всегда выше потенциала на истоке. В закрытом состоянии оба тарнзистора имеют высокое постоянное сопротивление канала (высокое, но не бесконечное). А значит, не зависимо от состояния входов, схема будет работать как обычный резисторный делитель напряжения. Что мы и наблюдаем на графике.

Armleo Автор

09.12.2021 00:45Вы расписали все идеально! Да, это так.

checkpoint

09.12.2021 01:09Рсскажите, у Вас был опыт размещения в SkyWatter/eFabless и чем все закончилось ? Судя по сайту ценник достаточно доступный, но очень много условий.

Armleo Автор

09.12.2021 01:18+1Пока не было. По идее через пару недель отправлю свою микросхему. А вот ребятам другим я помогал. Отправили ли они микросхему на производство или нет, мне не известно.

Бесплатно, вполне неплохая цена. Другие мне просто недоступны. Впрочем требования по сути одно: быть опен соурс.

checkpoint

09.12.2021 01:24Будет интересно узнать о результатах.

На сколько я понимаю, в сервис входит корпусирование и тестовая логика с каким-то простеньким МК ?

mikki33_2000

09.12.2021 02:00Вы расписали все идеально! Да, это так.

А вы проверьте ток в симуляции. Он будет сильно отличятся от утечек, которые бы получили при закрытых транзисторах.

mikki33_2000

09.12.2021 01:35+1Тоже неправильно. Каждый из транзистров подсоединен как source follower (также называется common drain stage). Для N - выходное напряжение меньше входного на Vt.

Для Р - наообот.

http://webpages.eng.wayne.edu/cadence/ECE7570/doc/cdrain3.pdf

Armleo Автор

UPD: Поправил гитхаб. Теперь должно git clone работать нормально.