Довольно долго от нас не было вестей — превращали схемы и чертежи сервера в реальное железо. Теперь у нас появилась рабочая первая ревизия, и в преддверии майских праздников можно порадовать вас рассказом, чем занимались наши разработчики последние полгода. И конечно, показать результат — в этой статье впервые опубликуем фотографии, а не только схемы и модели.

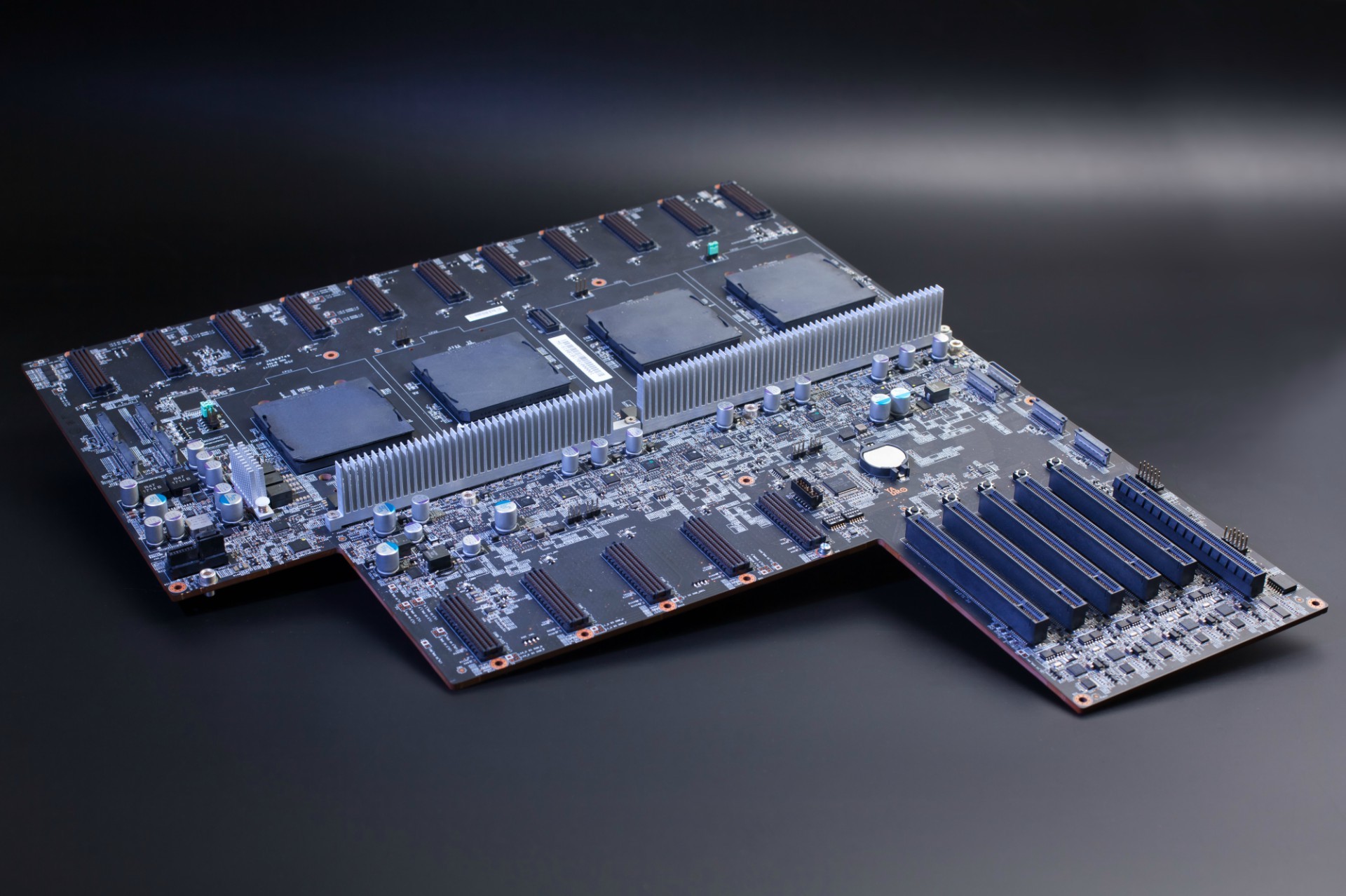

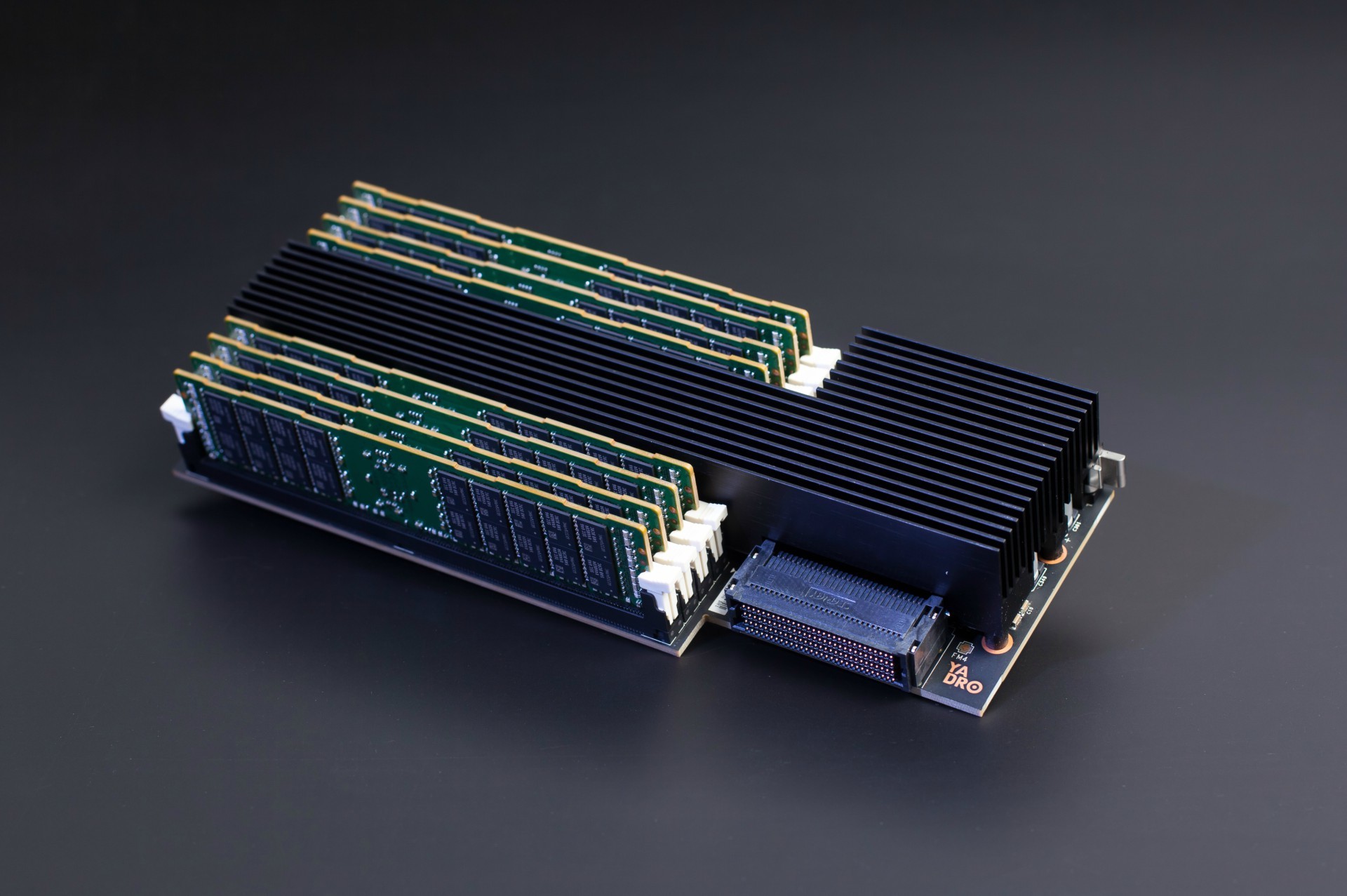

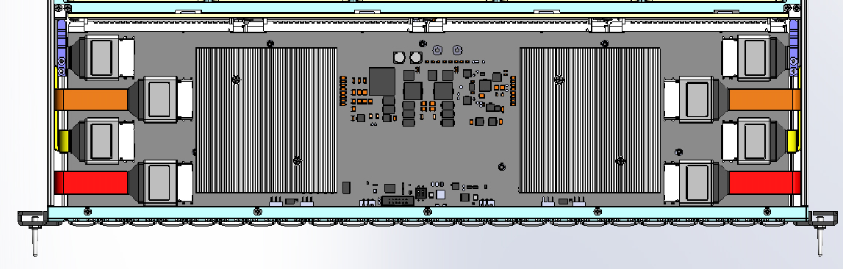

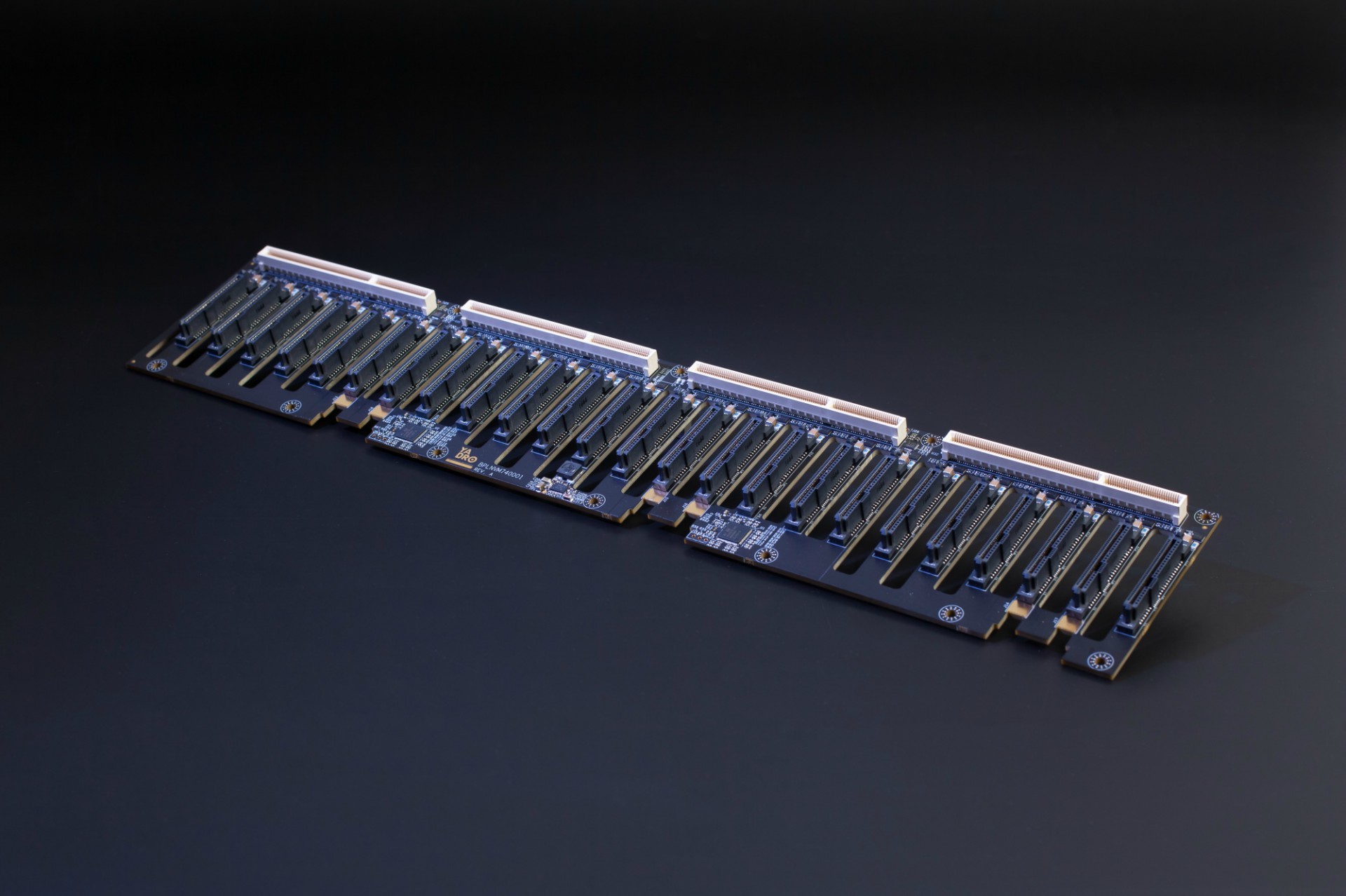

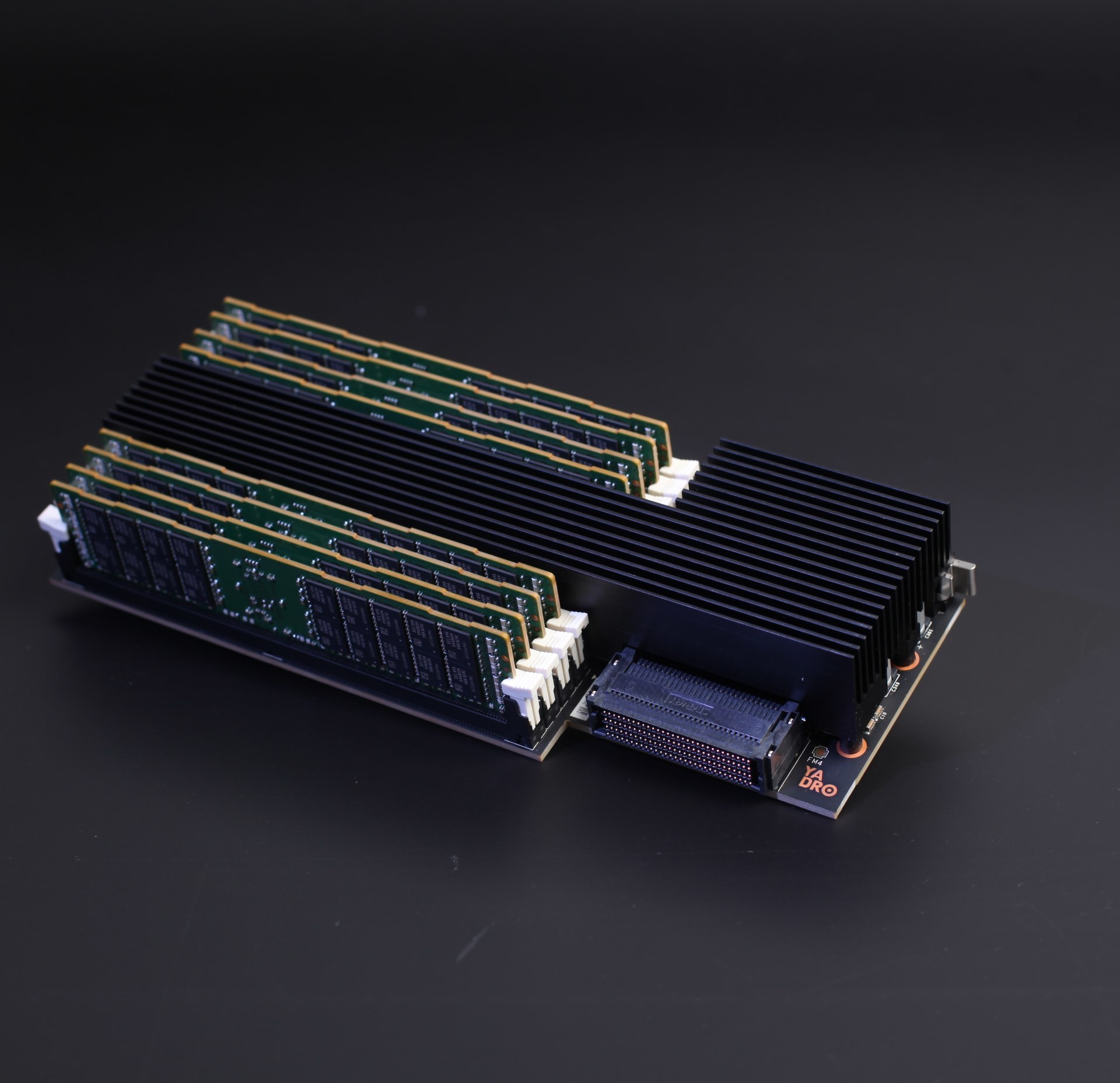

Райзеры с памятью в первой ревизии нашего сервера.

Сделали мы немало:

- Завершили трассировку и изготовили образцы материнских плат, плат управления и плат райзеров памяти.

- Разработали и отправили в производство платы коммутаторов PCIe, платы для вентиляторов и платы индикации и интерфейсов (с кнопками, разъёмами и светодиодами).

- Разработали и запустили в производство платы распределения питания от CRPS-источников и бэкплейны для NVMe-дисков.

- После приезда первых образцов прошли этап отладки материнской платы, платы управления и райзеров памяти.

- Доработали корпус сервера — во время проектировки плат потребовались небольшие изменения в нескольких местах.

Дальше расскажу про каждую тему по очереди, и для каждой подкину свежие порции стильной инженерной графики и фотографий. За хорошие фотки спасибо коллеге-программисту, увлекающемуся фотографией — поснимал компоненты вчера, пока был перерыв в тестах железа (фотку для шапки статьи пришлось снимать уже после его ухода домой).

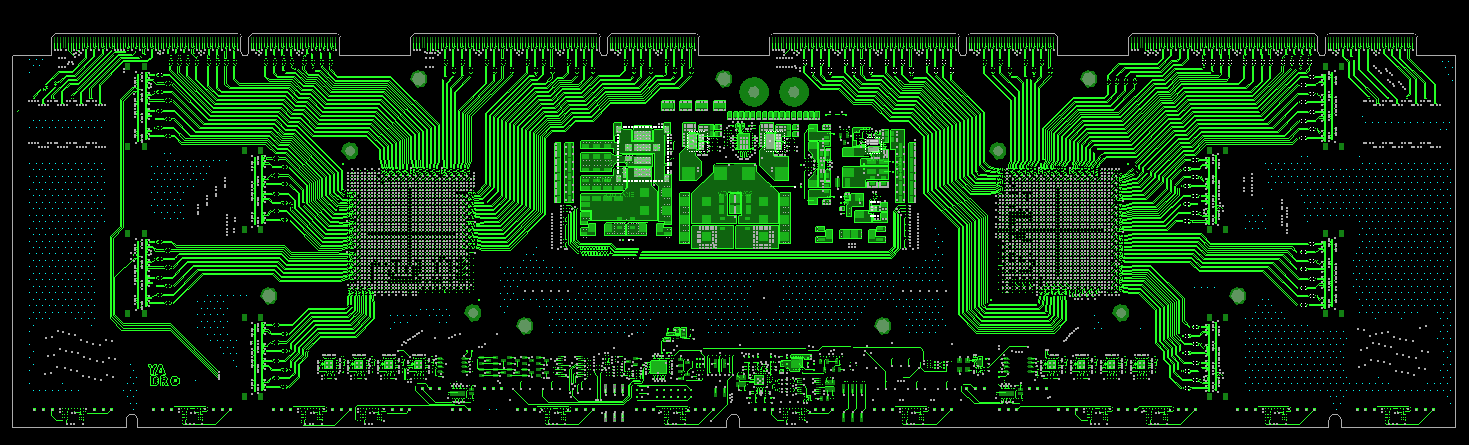

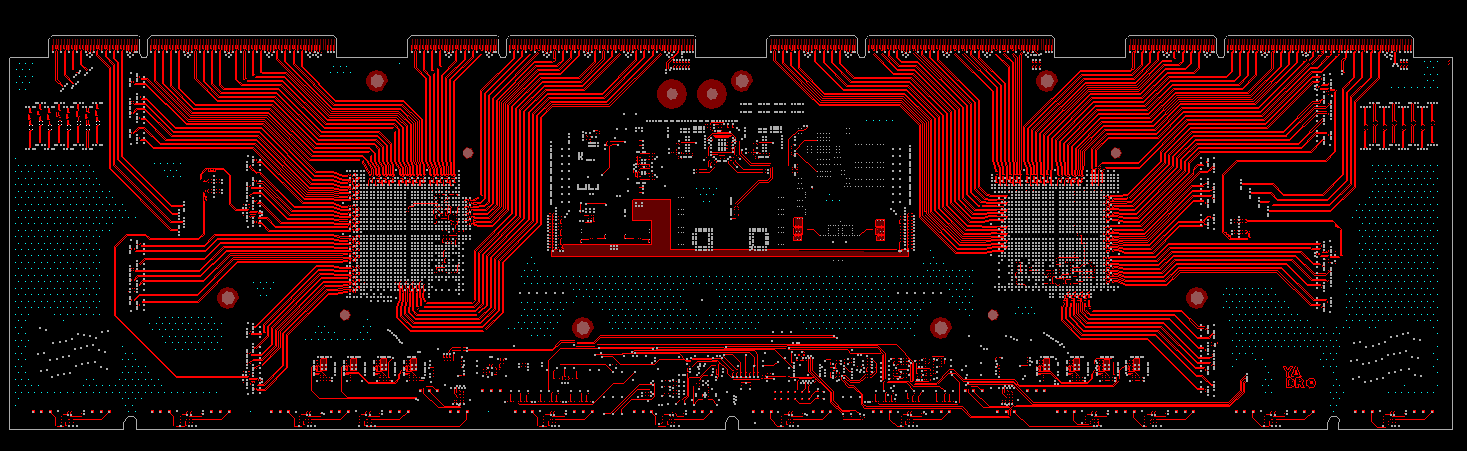

Материнская плата

С момента публикации нашей вводной статьи про материнку мы занялись окончательным согласованием всех требований к расположению шин питания и разъёмов. Также зафиксировали схемы райзера памяти — они влияют на pin-out разъёмов для райзеров на материнской плате. Утвердили схемы платы распределения питания от CRPS-блоков и распиновку разъёмов OCuLink (Nano-Pitch).

По питанию всё-таки получилось разместить и развести VRM для процессоров на материнской плате — дополнительные платы не понадобились. Учитывая плотность платы, необходимую площадь питающих полигонов и количество переходных отверстий, необходимых для прохождения большого тока, — пришлось повозиться. И после этого ещё выполнили тонкую настройку высокоскоростных цепей для наилучшего качества сигнала.

На выходе получилось могуче:

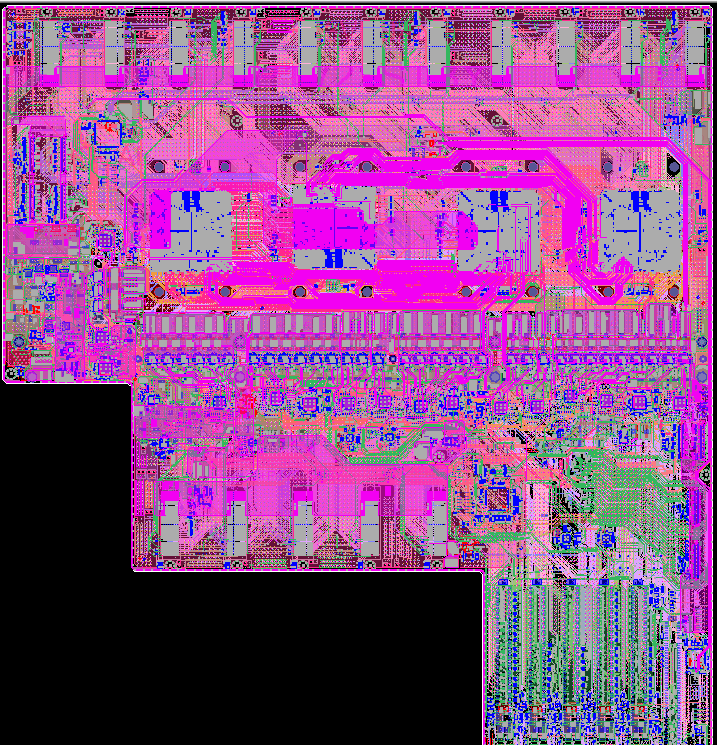

Материнская плата сервера во всей беспощадной для глаз красе.

Материнская плата сервера во всей беспощадной для глаз красе.Где-то трассировка была попроще:

Трассировка шины DMI рядом с разъёмами для райзеров памяти.

Трассировка шины DMI рядом с разъёмами для райзеров памяти.Где-то чуть посложнее:

Трассировка шины A-Bus между двумя процессорами. Немного тёмной магии и ловкости рук.

Трассировка шины A-Bus между двумя процессорами. Немного тёмной магии и ловкости рук.А на этой картинке видно, как упакованы те самые VRM-ы процессоров:

VRM процессоров в сплочённом ряду.

VRM процессоров в сплочённом ряду.И вот, наконец, можем предъявить результат работы над материнкой. Так она выглядит после изготовления и монтажа:

Первая ревизия материнской платы.

Первая ревизия материнской платы.Райзер памяти

Райзер памяти мы сделали на основе референсного дизайна OpenPOWER. Основное отличие заключается в том, что мы увеличили количество DIMM-разъёмов до двух на канал (был один) при приблизительно одинаковых габаритах платы.

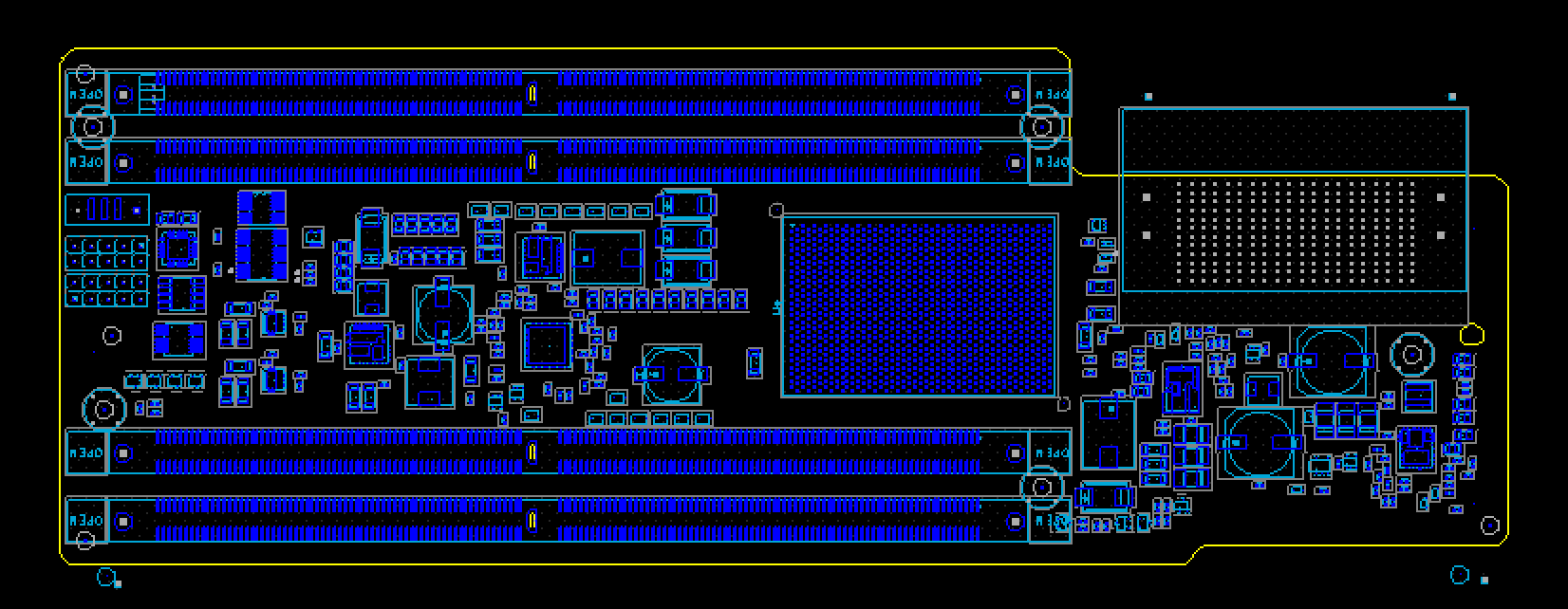

Вот иллюстрации райзера из референсного дизайна и нашего:

Референсный дизайн райзера.

Референсный дизайн райзера. А это наш дизайн райзера.

А это наш дизайн райзера.Чтобы разместить большее количество разъёмов, пришлось сразу по нескольким направлениям модифицировать референсный дизайн:

- Заменили SMD DIMM коннекторы на Press-Fit, так как их можно разместить гораздо ближе друг к другу.

- Приблизили слоты DIMM к чипу буфера памяти.

- Выкинули из схемы множество отладочных коннекторов.

- Оптимизировали схематику подсистемы питания, чтобы снизить площадь, занимаемую компонентами.

- Использовали более плотный коннектор для подключения к материнской плате.

В ходе разработки этой платы столкнулись с двумя основными сложностями:

1. Разводка стала более плотной

Основная проблема была с разводкой шины адреса и команд, так как при сближении DIMM и Memory Buffer мы не оставили себе места для выравнивания этой шины (она находится по центру DIMM сокета). Чтобы преодолеть эту проблему, мы вынесли часть шины адреса и команд на внешние слои (в референсном дизайне вся разводка осуществлена на внутренних слоях).

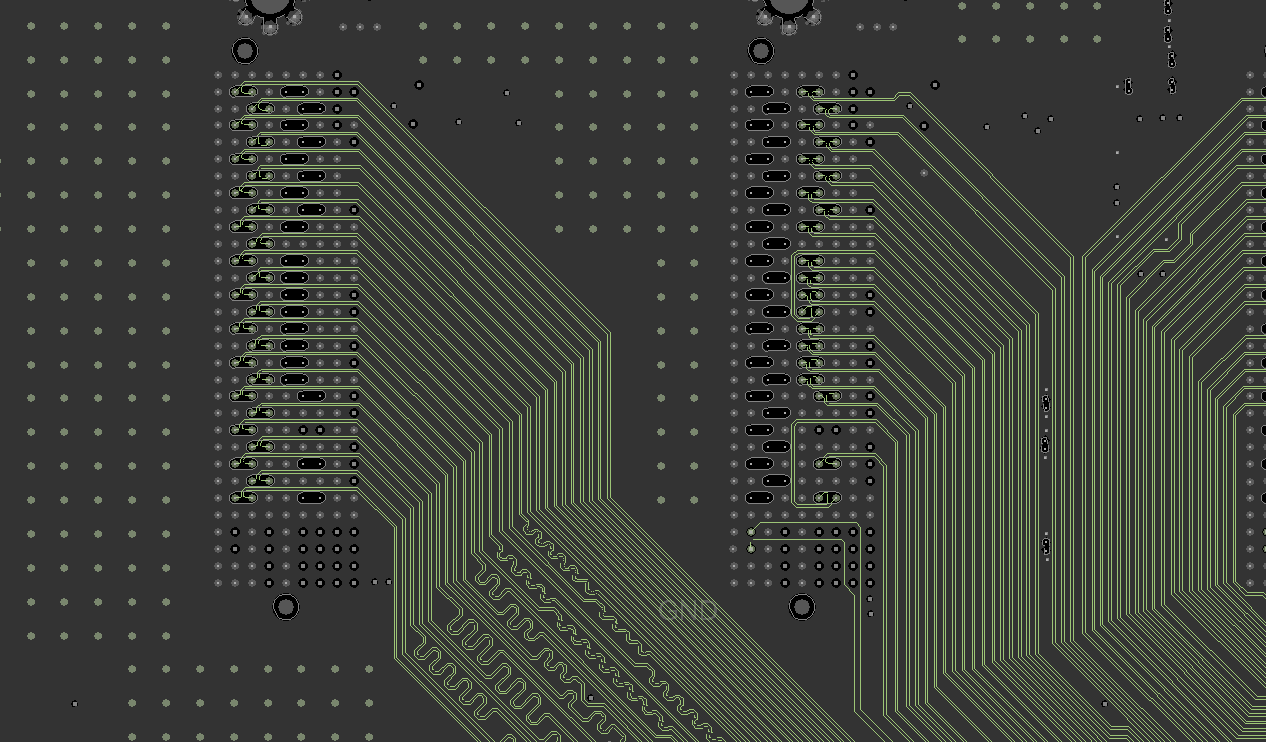

Разводка райзера памяти.

Разводка райзера памяти.Скорость распространения сигналов на внешних и внутренних слоях разная – поэтому выравнивание этой шины мы осуществляли в единицах времени, а не длины.

2. Ограничения коннектора

Вторая проблема заключалась в том, что используемый нами коннектор не имеет 85- Омной версии, только 100-Омную. В то время как быстрая шина DMI, проходящая через него имеет импеданс 85 Ом.

Однако мы пришли к выводу, что вследствие падения импеданса на пэдах коннектора примерно до 60 Ом, использование 100-Омного коннектора даже более предпочтительно, так как приводит к определенной компенсации данной неравномерности.

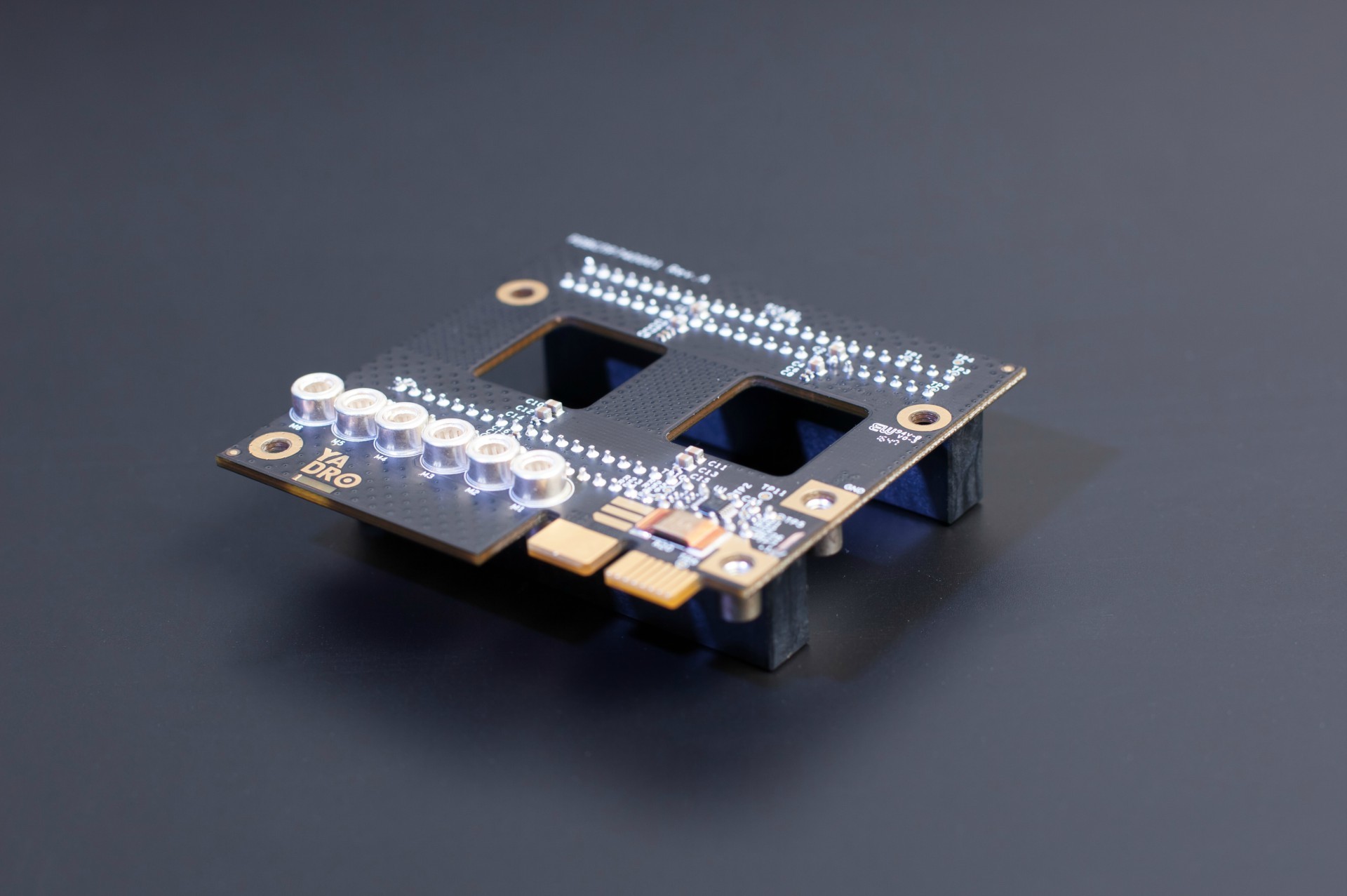

Вот что получилось в итоге:

Райзер памяти. Под радиатором прячется буфер памяти Centaur. Для экономии места использовали плотные 240-контактные разъёмы Samtec Searay SEAF-RA.

Райзер памяти. Под радиатором прячется буфер памяти Centaur. Для экономии места использовали плотные 240-контактные разъёмы Samtec Searay SEAF-RA.Плата для коммутаторов NVMe-дисков

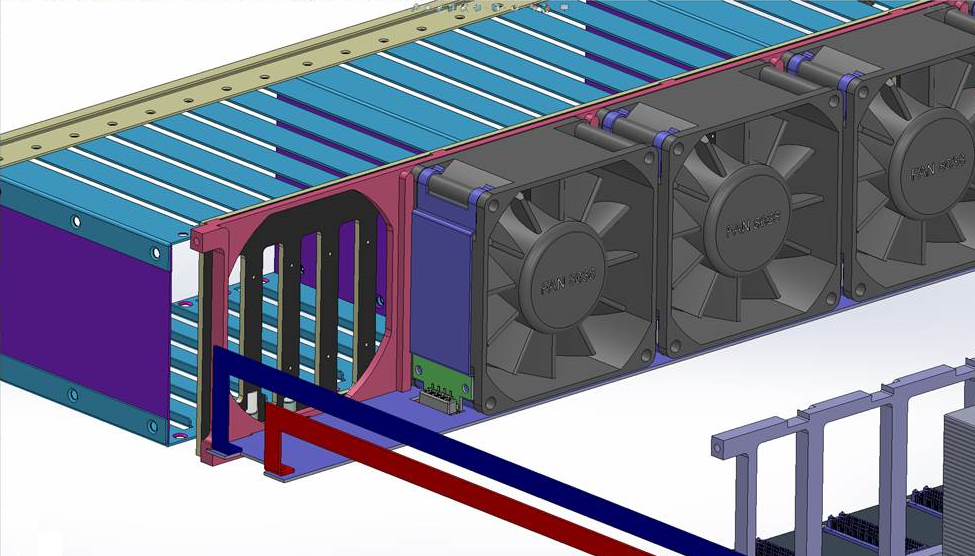

Плата с PCIe-коммутаторами в сервере находится над дисками — как писали в обзорной статье про сервер, на бэкплейне их разместить просто физически невозможно, слишком большие чипы. Уместили под самую крышку сервера.

На плате помещаются 2 чипа коммутаторов PCIe, и каждый из них в нашем случае может состоять из 2 независимых частей (партиций). Итого до 4 свитчей, и каждый из них подключен к своему процессору по шине PCIe Gen3 x16. Эти соединения мы сделали кабелями OCuLink. В случае если в системе установлено меньшее число процессоров — можно переконфигурировать разбиение свитчей чтобы обеспечить необходимую связь дисков с процессорами.

Во время разработки и трассировки пришлось учитывать множество ограничений по расположению компонентов на плате, вызванных жёсткими требованиями по высоте. Из-за того, что под платой находятся дисковые корзины, на нижнюю сторону платы мы могли поставить только пассивные компоненты размера 0402. На верхней стороне мы были ограничены высотой 9 мм.

Пришлось подумать и над относительным расположением разъёмов OCuLink и коммутаторов, чтобы удобнее было трассировать и подключать кабели при сборке сервера. Получилась такая схема расположения компонентов:

Схема платы коммутаторов для NVMe-дисков, внизу видны выступающие части дисковых корзин.

Такое расположение чипов и разъёмов потребовало сделать отдельный конфигурационный файл для каждого из чипов. Выбранные нами чипы коммутаторов имеют 5 блоков линий x16 (производитель чипов — Microsemi — называет их стеками), которые делятся между двумя партициями. Из-за того, что для удобства трассировки и монтажа чипы развёрнуты относительно друг друга, было удобно прописать разным чипам разные линии для подключения к хосту и к NVMe-дискам. Само по себе не вызывает сложностей, но на производстве придётся следить, чтобы в каждый из двух чипов была прошита предназначенная для него конфигурация.

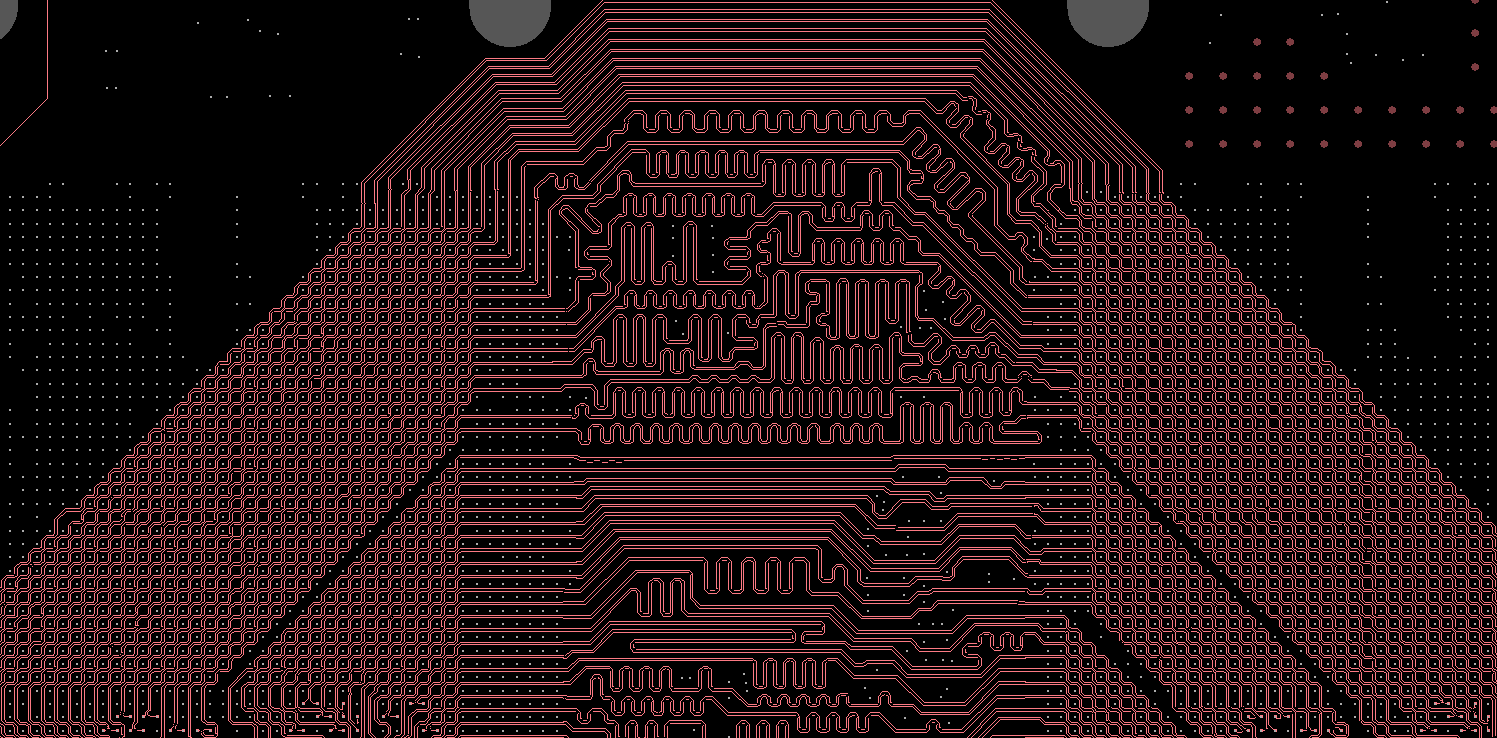

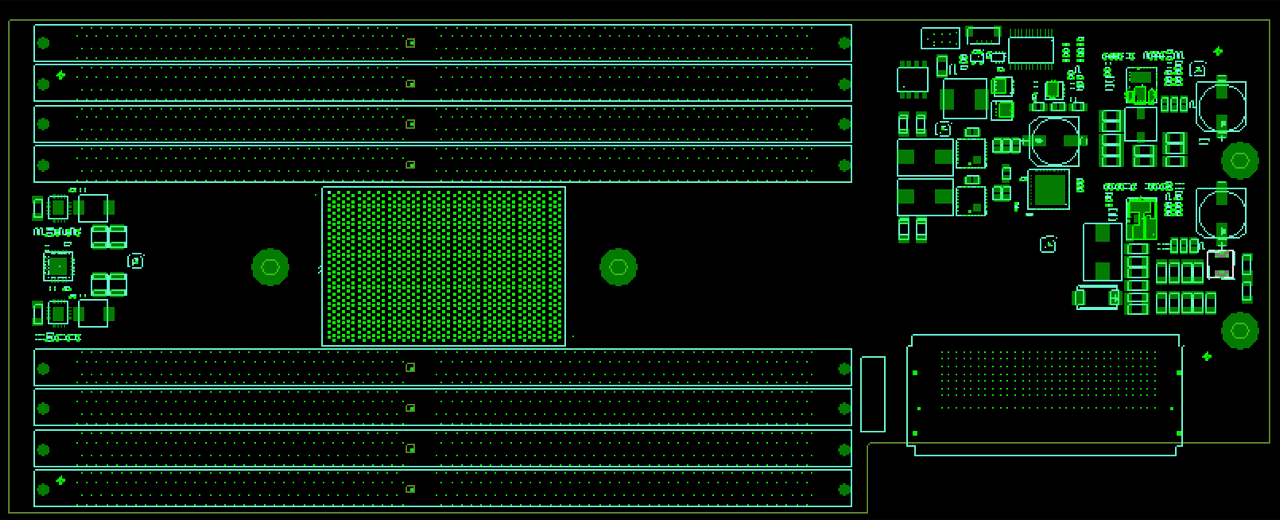

Верхний слой платы коммутаторов.

Верхний слой платы коммутаторов. Нижний слой платы коммутаторов. Welcome to the dark side.

Нижний слой платы коммутаторов. Welcome to the dark side.С внутренней стороны на краю платы находится линейка edge-коннекторов, через них плата подключается к дисковому бэкплейну. А с передней стороны мы разместили на ней сигнальные светодиоды для дисков — таким способом упростили конструкцию дисковых модулей и дискового бэкплейна. Сама плата ещё находится в производстве, её фотографии покажем в следующих статьях.

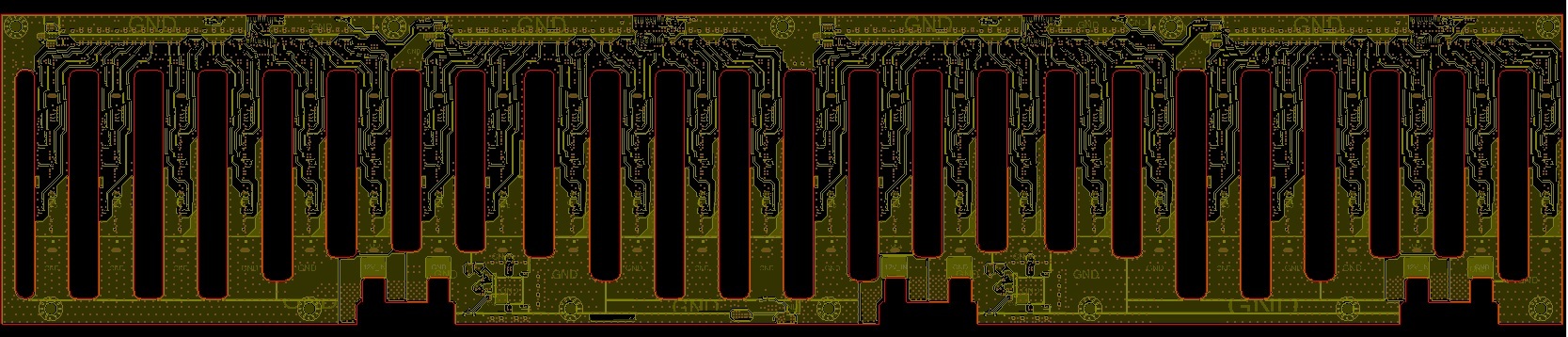

Дисковая объединительная плата (backplane)

В бэкплейн подключаются до 24 NVMe-дисков. Поскольку дисковые светодиоды мы вынесли на плату коммутаторов, не пришлось использовать световоды для вывода индикации на переднюю панель. Если бы светодиоды были на бэкплейне, то без 24 длинных световодов обойтись бы не получилось (они обычно размещаются в трее для дисков).

Плата бэкплейна стоит поперёк всего сервера перпендикулярно воздушному потоку. Чтобы обеспечивать хорошее охлаждение для процессоров и памяти, пришлось сделать в ней много равномерно расположенных отверстий. Старались и размер отверстий сделать побольше, увеличивая плотность трассировки и продумывая оптимальное расположение компонентов на плате. Но во время трассировки пришлось всё-таки немного уменьшить размеры прорезей для качественного прохождения высокоскоростных PCIe сигналов к дискам.

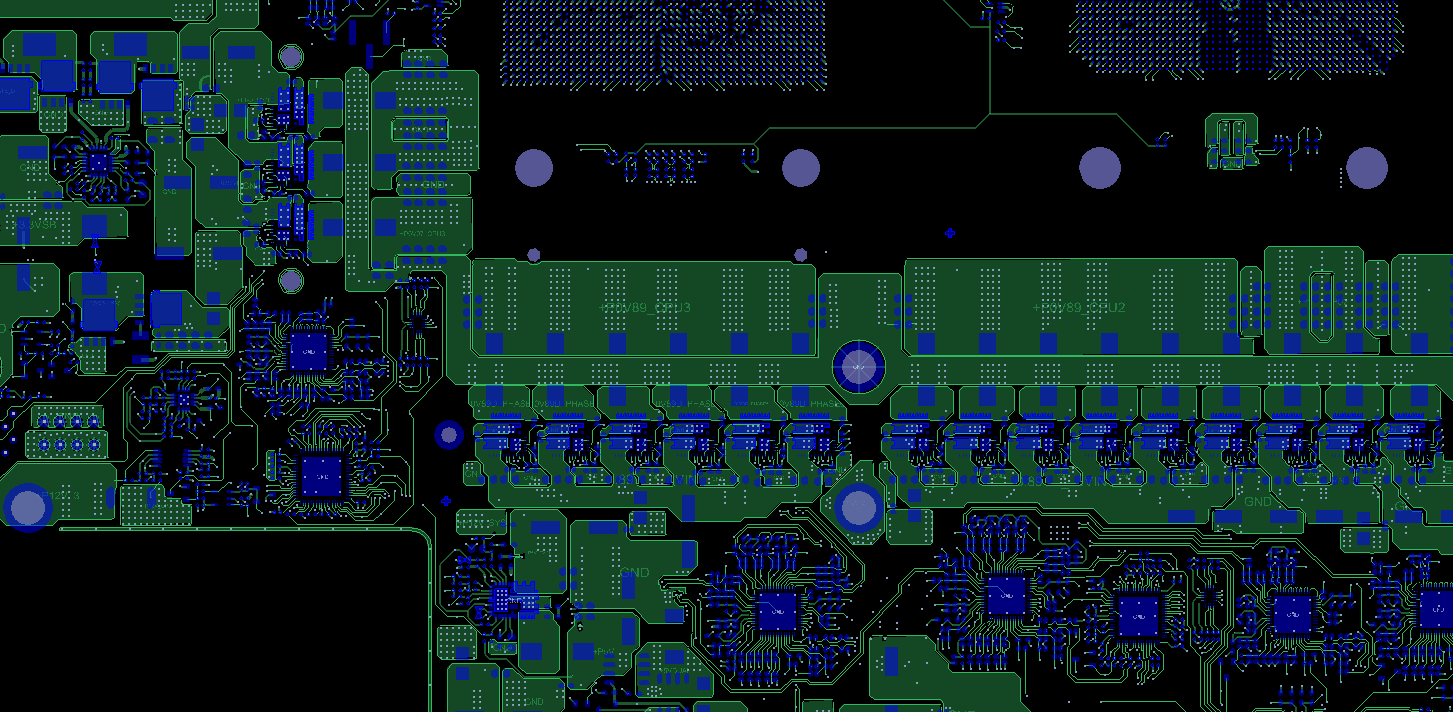

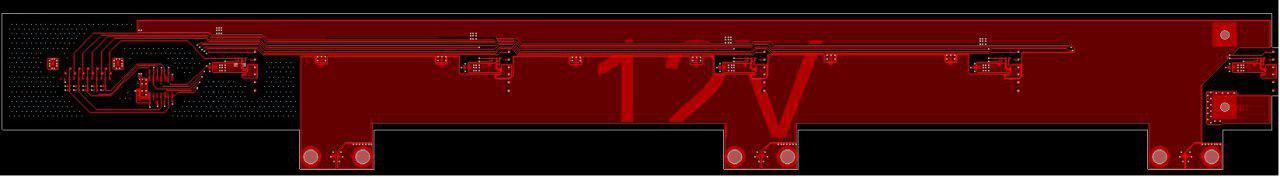

Cхема дискового бэкплейна. Дорожки навевают воспоминания о Гигере.

Cхема дискового бэкплейна. Дорожки навевают воспоминания о Гигере.Питание на плату поступает через 3 пары мощных пинов (RADSOK) — площадки для них хорошо видно на картинке внизу. Подается питание на диски, а также на плату коммутаторов через edge-разъёмы.

Дисковый бэкплейн, вид со стороны дисковых корзин.

Дисковый бэкплейн, вид со стороны дисковых корзин.Плата вентиляторов (fan midplane)

Сразу за дисковым бэкплейном в нашем сервере располагаются 5 вентиляторов. Они размещены в направляющих и подключены к мидплейну с помощью небольших плат, которые размещены на корпусе вентилятора.

Кроме передачи управляющего сигнала на вентиляторы и обратной связи от них, плата вентиляторов распределяет питание от CRPS-источников к вентиляторам, а также к дисковому бэкплейну. Общий ток достаточно высок (до 75 А в пике), а ширина платы не очень велика, поэтому пришлось создать мидплейн с увеличенной толщиной меди на слоях. Питание от CRPS-источников подвели через медные шины.

Плата вентиляторов. Несложная.

Плата вентиляторов. Несложная.Плата распределения питания

Это почти самая маленькая плата в сервере, но она играет важную роль – снимает электропитание от двух блоков и распределяет его на модули сервера. Передавать питание от этой платы в остальную систему мы решили через с помощью медных шин через мощные контакты (серия RADSOK).

Дежурное (Standby) питание передается через edge коннектор. Также через этот разъём идут сигналы на включение блоков питания, «power good» сигналы CRPS, а также данные от датчика тока, который измеряет потребление дисков и вентиляторов.

Плата распределения питания — маленькая, но мощная.

Плата распределения питания — маленькая, но мощная.Что дальше?

После майских праздников будем рассказывать более детально про тестирование и отладку разных подсистем. Следите за обновлениями!

Комментарии (41)

tehSLy

27.04.2017 15:57+4Ничто так не радует, как такая техника от отечественных компаний. Надеюсь, что когда-нибудь такие ребята как вы составят здоровую конкуренцию зарубежным брендам. Надеюсь на скорую следующую ревизию :)

SemenovNV

27.04.2017 17:09+1Спасибо! Приедут оставшиеся компоненты, соберём, потестируем всё тщательно, внесём изменения — в общем, шаг за шагом достигнем и второй ревизии.

Arxitektor

27.04.2017 18:24Отлично платы супер) Прямо как у яблока если не круче. Вот что значит талантливая команда в лексиконе которой нет слова невозможно.

Greendq

27.04.2017 19:54Круто! Несколько нестандартный вопрос — а сколько (в килограммах) весит плата? Там меди куча ведь? Меня в своё время удивил вес платы от биткоин-майнера — она несколько кг весит из-за медных дорожек.

Paging

27.04.2017 20:21Тяжелая, но я бы не сказал что несколько килограмм. Попозже взвесим, пока не озадачились этим еще. Она же толстая еще — 28 слоев, что-то около 3.5мм толщиной.

maxbrsw

27.04.2017 20:30+5Здравствуйте,

В первую очередь позвольте выразить почтение- очень респектовый дизайн, картинок хоть и немного, но уровень исполнения виден достаточно хорошо. Если не возражаете, несколько технических вопросов

— пользуетесь ли tabbed routing?

— сколько по времени занимает моделирование такой платы(или мажорных блоков) в плане SI/PI?

— как для таких дизайнов рассчитываете high-speed via structure/plane cut under passives?

— для Allegro используете ли какие-либо коммерческие productivity pack-и/наборы скриптов?

— используете ли встроенные компоненты для таких дизайнов, в т.ч. встроенные вертикально?

Напоследок хотелось бы чисто любопытства ради поинтересоваться- а как выглядят требования к вакансии PCB Designer-а в Вашей компании? Где в РФ Вы берете таких людей? Находите с нуля с таким опытом или обучаете? Что думаете о CID/CID+сертификации? Можно и в ЛС.

asmolenskiy

27.04.2017 20:44+3По пунктам

1) Нет. Для поддерживаемой нами памяти DDR4 1600 такой необходимости еще нет.

2) Плата не моделируется целиком. Моделируются отдельные блоки, которые потенциально могут вызвать проблемы. В среднем на один кейс от одного дня до недели.

3) Нет необходимости. Для данных частот еще можно использовать Rules of Thumb. В данном дизайне самая быстрая шина — DMI. 9.6GBps.

4) Нет

5) Не понял вопрос.

К сожалению к нам еще ни разу не приходили топологи, которые бы нас устраивали по своим профессиональным навыкам — поэтому мы бросили оценивать людей по данному параметру. Больше смотрим на то — понимает ли человек суть вещей в общем и целом.

Что такое CID/CID+?

maxbrsw

27.04.2017 21:14+2Благодарю за ответ- прежде чем уточнить пару моментов со свой стороны хотел бы отметить, что вопросы выше скорее для обобщенного случая, нежели только для конкретной платы:

1) В общем случае/в принципе Вы используете tabbed routing? А для DDR4 с указанной скоростью это разумеется излишнее.

2) То что плата не моделируется целиком это понятно, просто хотелось полюбопытствовать насколько большие блоки подвергаются моделированию и сколько времени на это требуется.

3) Понятно, ~10 Gbps это конечно не так много да и по Вашим картинкам не видно нигде больших стабов- ответ понятен.

4) А вообще скрипты используете?

5) Имеются в виду, например, вертикально встроенные терминаторы в хайспидах, но ув. Paging уже опередил с комментарием ниже. Касаемо целесообразности применения ответ понятен, но можно ли узнать подробнее об браке?

Что насчет топологов- т.е. Вы грубо говоря не рассчитываете найти человека который сразу бы отвечал всем требованиям, а постепенно его обучаете чтобы вытянуть на нужный уровень? Если не секрет, в чем как правило человек не соответствует по опыту/знаниям?

CID/CID+ это профессиональная сертификация PCB Designer-ов.

Paging

27.04.2017 22:03Я отвечу на часть вопросов, Антон на остальные.

1. Только собираемся (в другом проекте, где будет DDR4-2400).

5. Любой технологический процесс — это брак. Спроектировали плату с бэкдриллом — увеличили процент брака. Заембеддили пассивку — опять увеличили. И так далее. Другое дело, что какие-то PCB-fab'ы хорошо умеют работать с определенным процессом, какие-то — не очень, это конечно сильно влияет на процент отбраковки. По нашей материнке мы ожидаем порядка 10-15 процентов брака голых PCB из-за большого количества бэкдрилла. Причем при таком проценте нет смысла, к примеру, уходить на фабрику где его умеют делать лучше — как правило там будет дороже само производство, а мы работаем с относительно дешевым производителем. Конечно, у нас бывают гораздо более сложные платы (материнка все-таки достаточно простая технологически, у нас есть намного более плотные платы в других проектах) — и тогда мы размещаем заказ там, где их действительно могут сделать качественно. Просто как пример — одну из наших плат (образцы, не серию) один из китайских производителей смог произвести только с третьего захода (в первый раз были замыкания во внутренних слоях, во второй платы не прошли контроль импеданса).

6. Ребята конечно учатся постоянно (как и любые нормальные профессионалы). Одним из самых основных критериев при наборе команды было понимание физики происходящих на плате процессов. Можно заучить набор правил — но почти на каждой плате есть вещи, которые нельзя красиво сделать тупо следуя шаблонам. Нужно понимать, что лежит под этими правилами, откуда все исходит.

asmolenskiy

27.04.2017 22:20+21) Пока нет. Просто потому что пока мы дизайнили этот борд — Tabbed Routing превратился из экзотики в стандартную технологию. Мы конечно знаем что это такое и как/зачем делается, но применить в реальном продукте еще не довелось.

2) По моей личной профессиональной практике — разные. Причем время не прямо пропорционально размерам. Я могу неделю считать переходное отверстие для каких-нибудь десятков гигагерц, а потом за пару часов отмоделлить полуметровый тракт с коннекторами и виа-переходами.

4) Нет

Не рассчитываем.

И я бы не сказал что как-то особо обучаем.

Касательно того что предпочтительнее. Ну условно если взять два крайних случая:

— человек умеет супер-опыт работы в Cadence, знает где и зачем применяется тот же Tabbed Routing, знает где и какие антипады ставить. В общем — зверь.

— человек вообще не работал в Cadence, в первый раз в жизни видит этот Tabbed Routing и и вообще разводку DDR4, зато сможет понять и объяснить каким образом и почему этот Tabbed Routing снижает XTalk

вот далеко не факт что первый кандидат будет предпочтительнее.

Мы можем потерпеть месяц пока человек найдет все нужные кнопочки и менюшки в Cadence и переучится там… с Альтиума — если он понимает что и зачем он делает.

Хотя конечно если у нас будет официальная вакансия тополога — мы там много чего понапишем в требованиях.

По сертификации.

Вот одна большая и известная компания, не буду ее называть — каждый год возит своих инженеров на обучение к Богатиным, Джонсонам и тому подобным «богам» SI. Идешь у них по офису — а там у каждого висят тучи сертификатов, говорящих что он спец по там… Noise & Grounding или SI или еще что-нибудь. Начинаешь задавать профессиональные вопросы в надежде получить какие-то советы и понимаешь что человек дальше своих корпоративных Design Rules не понимает нифига.

Вот так лично я отношусь к сертификации.

У моих коллег и руководителей конечно может быть совершенно иное мнение.

maxbrsw

27.04.2017 22:59+2Спасибо за подробные пояснения. Правильно ли я понимаю- Вы предпочитаете в первую очередь людей, которые имеют хорошую теоретическую подготовку в означенных областях? По поводу сертификации целиком и полностью разделяю Ваше мнение- от себя могу добавить, что на Западе идеологически сложилась любовь к «бумажкам»(не берусь давать этому оценку в стиле «хорошо/плохо», отнюдь), что в определенных случаях привело к уверенности некоторых групп людей(тех же рекрутеров) в том, что «CID» это тоже самое что и «невероятно крутой PCB Designer». К сожалению или к счастью, неоднократно встречал дизайны уверенно доказывающие обратное. С другой стороны, есть немало людей которые по тем или иным причинам не могут или не хотят осилить даже «начальный этап», т.е. design guides или rules of thumb, не говоря уже о специфике. А как Вы сами пришли к подобным задачам/опыту/уровню, если не секрет?

Позвольте еще пару вопросов по платам:

— какому классу по IPC соответствуют платы на фото выше?

— используете ли сторонние CAM редакторы?

— используете ли стороннее ПО для планирования/составления стеков?

Можете ли Вы или Ваши коллеги что-либо порекомендовать в рамках профессионального роста как PCB Designer-а?

asmolenskiy

27.04.2017 23:20+1Хорошая теоретическая подготовка — это когда человек на вопрос как пойдет обратный ток при трассе в виде тромбона, отвечает что для НЧ — прямо под трассой, а для ВЧ — по прямой. А после того как ты выражаешь недоумение по поводу его ответов — выясняется что НЧ в его понимании это все что до 15GHz. А в таком ключе этот ответ — абсолютно верен. Это кстати случай с реального собеседования.

У нас таких нет =). Наши топологи просто любознательные и сообразительные парни, которые не тупо заучивают правила и размеры антипадов, а пытаются понять физику процесса.

Чтобы человек пришел к какому-то уровню развития — в первую очередь ему нужно поставить соответствующие задачи. Нет задач — нет развития. Мы так и пришли.

Ответы на вопросы:

— не знаю =)

— нет

— тоже нет — я не очень понимаю зачем нужен какой-т спец. софт для стэков. У нас есть параметры всех препрегов и ядер для используемых нами материалов. В смысле не общий даташит — а полные раскладки по стеклам и RC. И мы умеем считать степень сжатия. Что еще нужно?

maxbrsw

27.04.2017 23:39Спасибо, мысль понятна- ну то есть соискателю не предлагается решать на листке уравнения Максвелла на собеседовании?:)

Ответ касаемо рекомендаций вполне ожидаем, но больше имелся в виду этап когда заполняется разрыв между задачами и реальными возможностями человека, того же нового тополога. Наверно маловероятно что новому человеку дают сразу разводить motherboard- здесь и интересно было узнать, как дотягивают человека и за какое время.

По софту вопрос чистого любопытства: мне как PCB Designer-у попросту интересно узнать детали рабочего процесса у людей с подобными задачами и компетенциями, тем более из РФ- что само по себе вызывает приятное удивление.

asmolenskiy

27.04.2017 23:50Спасибо, мысль понятна- ну то есть соискателю не предлагается решать на листке уравнения Максвелла на собеседовании?:)

Конечно нет — мы с головой дружим.

Ответ касаемо рекомендаций вполне ожидаем, но больше имелся в виду этап когда заполняется разрыв между задачами и реальными возможностями человека, того же нового тополога. Наверно маловероятно что новому человеку дают сразу разводить motherboard- здесь и интересно было узнать, как дотягивают человека и за какое время.

Э… никак =). Ну нас был как-то момент когда надо было много простых разных плат и пришел Альтиум-тополог с не очень большим бэкграундом. Мы конечно все это на него и свесили, чтобы он софт освоил и стрессовал поменьше. Но это не закономерность — просто так получилось.

asmolenskiy

28.04.2017 00:01Но вообще я если честно лукавлю.

Наши «молодые и любознательные» топологи на самом деле на момент начала работы у нас — давали фору 90% топологов на рынке. Мы очень тщательно выбираем людей.

Я просто хочу сказать что знание САПР и каких-то правил — для нас не главный критерий.

maxbrsw

28.04.2017 00:40Но вообще я если честно лукавлю.

Я так и подумал- иначе бы наверное слишком многие могли бы делать такие платы, что конечно же неправда.

Наши «молодые и любознательные» топологи на самом деле на момент начала работы у нас — давали фору 90% топологов на рынке. Мы очень тщательно выбираем людей.

Это собственно и было основой моего вопроса про то, «откуда и как берутся такие люди». Что у них за плечами, что делали и пр.- многие люди с трудом могут развести USB 3.0, не говоря о том чтобы качественно положить пару байтлейнов DDR3 на одном слое для несложной FPGA. А тут практически из огня да, в полымя: очень тяжело верится в то что можно вот так просто получить адекватный результат, дав соответствующую задачу человеку без опыта разводки подобных устройств.

Я просто хочу сказать что знание САПР и каких-то правил — для нас не главный критерий.

Это разумеется понятно- просто хотелось знать Ваши требования к «глубине теории»: даже в пределах РФ встречал людей, которые всерьез желали видеть уверенные навыки расчетов по электродинамике аналитическим методом вручную.

lelik363

28.04.2017 23:52Вот одна большая и известная компания, не буду ее называть — каждый год возит своих инженеров на обучение к Богатиным, Джонсонам и тому подобным «богам» SI.

В России есть такая компания?

Paging

27.04.2017 20:48Если встроенные компоненты — это интегрированные в структуру PCB — то нет, не используем. Это дорого, высокий процент брака и в нашем случае не особо нужно.

Vovanys

27.04.2017 20:31А зачем так нужно кривлять, ведь можно пустить напрямую? Наводки? Или нужна определенная длина линии?

Paging

27.04.2017 20:34Для некоторых сериализованных шин требуется жесткое выравнивание всех дифф. пар в группе. Точнее, конечно у всех шин есть требования по выравниванию, просто у некоторых допускается значительный разброс, а у некоторых совсем небольшой. На картинке шина межпроцессорного интерконнекта (A-Bus).

maxbrsw

27.04.2017 21:23+2Разрешите вопрос по памяти- всегда интересовало следующее: почему так мало используется MCP(Multi-Chip-Package) в таких дизайнах? Я достаточно много видел и сам делал платы с x86 и толстыми FPGA(но не серверы конечно) и такая практика достаточно повсеместна в High-End устройствах. Имеются в виду не MCP коммерческого класса(например для смартфонов, т.е BGA шагом 0.5мм и менее, в т.ч. POP), а «обычные» сборки кристаллов DDR3/4 на BGA с шагом 0.8/1мм, как например у Mercury Systems.

Мне всегда виделась причина в том что у MCP есть чисто технические ограничение на итоговый объем памяти, например для целого ранка, т.е. обычными микросхемами проще набрать нужный объем-однако хотелось бы узнать Ваше мнение на этот счет.

Paging

27.04.2017 21:54+1В нашем сегменте рынка MCP как технология может быть интересна только для памяти, и, к слову, она там активно применяется: на один RDIMM высотой 31,5мм невозможно уместить более 36 чипов памяти, поэтому если применять имеющиеся сейчас на рынке single-die чипы емкостью 8Gbit (а сегодня это максимум) то получаем максимальный размер модуля 32GB, в то время как на рынке доступны и 64GB, и 128GB модули — в них применяются dual-die и quad-die чипы, в которых восьмигигабитки сшиты TSV. Но это дорого, особенно по меркам такого конкурентного рынка как рынок памяти. Поэтому как только емкость превышает доступную сегодня к получению 36-ю монолитными чипами — стоимость модуля за GB сразу резко растет.

maxbrsw

27.04.2017 23:01Спасибо за подробный ответ- а Вы всегда используете именно покупные модули памяти, или бывает что делаете свое?

Paging

27.04.2017 23:04Мы ставим чипы DDR4 на платы в некоторых проектах, где стандартные модули не удобны по каким либо причинам (как правило это ограниченность в размере). Но делать самостоятельно стандартные RDIMM конечно было бы довольно странно, поскольку Samsung/Micron/Hynix/etc все равно дешевле будет.

maxbrsw

27.04.2017 23:06Понятно- тут имелся в виду возможный случай «нестандартного» форм-фактора, если такое явление существует конечно.

Scrypto

28.04.2017 07:20Может быть дело в скорости прохождения сигнала по линиям? Возможно при больших частотах, он за такт проходит не так и много, и если не сделать вот такой змейки будут несостыковки? Честно не знаю, но логично предположить, что так

electronus

28.04.2017 05:05Эх. Райзер с таким мощным радиатором придется крепить пожестче, дабы при перевозке он не наворотил.

Видел пропиетарные райзеры в одном месте, так там решили сделать контакты как на pciex плате, только более мелкие со стороны райзера, и соответственный разъем на материнке. Всего 8 райзеров — 2Тб DDR4

SemenovNV

28.04.2017 07:54Для этого у нас в корпусе сервера предусмотрены две рамки, которые жёстко фиксируют райзеры. Одна рамка для передней группы райзеров, и одна для задней. Фотку сделать не могу (отъехал в отпуск), но краешек рамки можно увидеть на иллюстрации к обзорной статье про сервер. Вот эта картинка, на ней в правом нижнем углу часть рамки видна:

.

.

electronus

28.04.2017 08:08Респект! Ещё с интересом рассматривал ваше решение для экспресс-дисков. Последний раз видел решение в виде ретаймеров на базе 4хсетевух с кастомной фирмварью для восьми дисков, у Вас то дисков побольше будет на одно ядро…

agoodmood

28.04.2017 07:20Интересно, каким инструментом пользуетесь для контроля версий трассировки плат?

dzhaputai

28.04.2017 07:20Возможно ли нечто подобное изготовить на отечественных микросхемах?

на отечественном оборудовании?

Paging

28.04.2017 08:08+1В отечестве пока (надеюсь что пока) нет вычислительной платформы, которая могла бы хоть условно составить конкуренцию.

В плане оборудования (если говорить про производство PCB) — да, почти все можно сделать. А если напрячься и напрячь всех — то даже вообще все. Вопрос как обычно сроков, цены и качества (процент брака).

А монтаж плат давно уже не является проблемой, основная проблема тут с закупкой компонентов (когда мы делаем монтаж в Китае и на Тайване значительная часть компонентов по BOM есть у наших партнеров на складах).

murz165

Красота! Некоторые фотки напоминают рендер, но при более детальном просмотре видно, что реальная фотка (хорошо сфоткали)! Так держать, господа! Но PDB-ха лучше всех! )))

SemenovNV

На самом деле с фоток просто убрали выхваченные вспышкой микропылинки, небольшие дефекты пластикового фона и шум.

Остальное натуральное — цветная подсветка, матовый пластиковый фон, хороший фотик и прямые руки.

Вот, например, исходный вариант фотки райзера (только сжатый до 1920 пикселей по широкой стороне по требованиям Хабра):

Как будет перерыв в тестах, сфоткаю с телефона компоненты.

Ну и в шапке поста тоже фотка набивки сервера далека от идеала, увы :)

SemenovNV

Отснял на столе компоненты на мобилку.

Внизу, кстати, виднеется корпус сервера.