Большинство любительских проектов FPGA, опубликованных на Хабре, сделаны на оборудовании фирмы Altera (теперь Intel). Давайте для разнообразия посмотрим, что можно сделать на продукции его основного конкурента – Xilinx. Мы возьмём и сделаем достаточно большой и сложный проект, в процессе реализации которого нам понадобится:

- Выбрать Development board и необходимые PMOD к ней

- Определиться с дизайном проекта, выбрать clock domains и правила перехода между ними

- Освоить основные функции Xilinx Vivado – создание проекта, работу с блочными схемами, компиляцию, симуляцию, отладку

- Сделать несколько IP с интерфейсом AXI4

- Поработать с внешними устройствами

- Сделать с нуля собственный процессор с контроллером шины и обработкой прерываний

- Написать модуль для верификации

- Наконец собрать всё вместе и получить реализацию на FPGA легендарного (как минимум для тех, кто тогда жил) компьютера середины 80-х – БК-0010

Планируется цикл статей, в которых всё это будет подробно описано, сегодня первая из них. Проект написан на System Verilog с небольшими вставками Verilog и VHDL в тех местах, где это необходимо. От читателя требуется понимание базовых принципов языков Verilog/VHDL на уровне книжки Харрис&Харрис.

Пара слов о БК-0010

БК-0010 появился в 1986 году и представлял собой одноплатный компьютер на базе процессора КР1801ВМ1 (система команд DEC PDP-11). По мере повествования нам придётся рассмотреть кое-какие его архитектурные особенности, пока же ограничимся теми характеристиками компьютера, которые нам будут важны для выбора платы и другого оборудования:

| Характеристика | Значение |

|---|---|

| CPU | 3 MHz, количество транзисторов около 18000 (n-МОП) |

| RAM | 32 KB |

| ROM | 8-32 KB |

Устройства вывода

- Бытовой телевизор, 512x256 в черно-белом режиме либо 256x256 в цветном (каждая точка могла иметь 4 цвета независимо от других)

- Звуковая пищалка (вывод 1 бит), совмещенная с выводом на магнитофон

Устройства ввода

- Клавиатура с расположением клавиш ЙЦУКЕН (JCUKEN)

Выбор платы

Какую плату и на каком кристалле взять для проекта? В случае с кристаллом под наши требования можно выбирать из Artix-7 и Zynq-7000, в обоих случаях будет достаточно самого маленького кристалла. Платы для разработки — кое-что делает сама Xilinx, это платы с весьма богатой начинкой, но с четырехзначным ценником. Есть европейская компания Trenz Electronic GmbH, но я бы сказал, что их продукция больше ориентирована на создание готовых устройств. На мой взгляд, наиболее подходящие платы с чипами Xilinx для любительского использования делает компания Digilent. На Artix-7 это Basys-3, Nexus 4 DDR и Nexus Video, на Zynq-7000 это Zybo и ZedBoard.

Для себя я остановился на Zybo. Эта плата одна из самых дешевых ($189, а если вы убедите Digilent, что удовлетворяете требованиям Academic Discount Program, то $125), у неё есть выходы как VGA так и HDMI, много портов PMOD, 512MB RAM. Да, эта плата основана на SoC, а возможности процессорного ядра я в этом проекте использовать не планирую. Но никто не мешает использовать эту плату просто как FPGA. У платы отсутствуют отладочные семисегментные индикаторы и нет возможности подключения PS2 либо USB клавиатуры к FPGA-части (в отличие от более дорогой Nexus 4 DDR), но разница в цене между этими двумя платами существенно больше, чем стоимость модулей PMOD, на которых эту функциональность можно получить.

Итак, в сухом остатке, для проекта нам понадобятся следующее оборудование:

Zybo

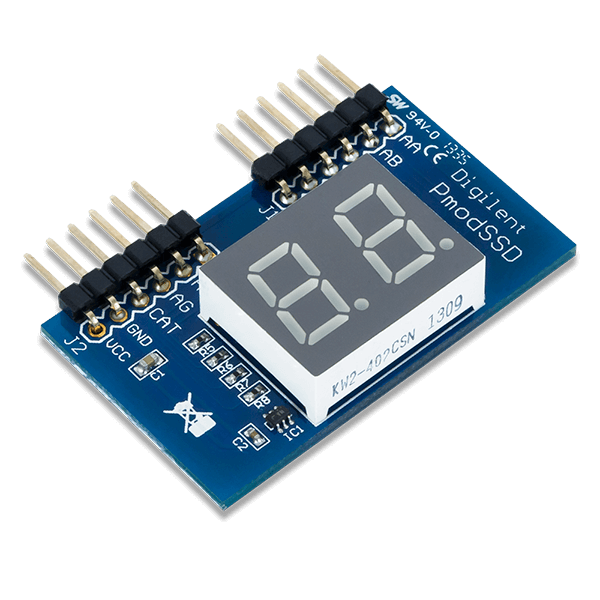

PMOD-SSD – два семисегментных индикатора для отладки

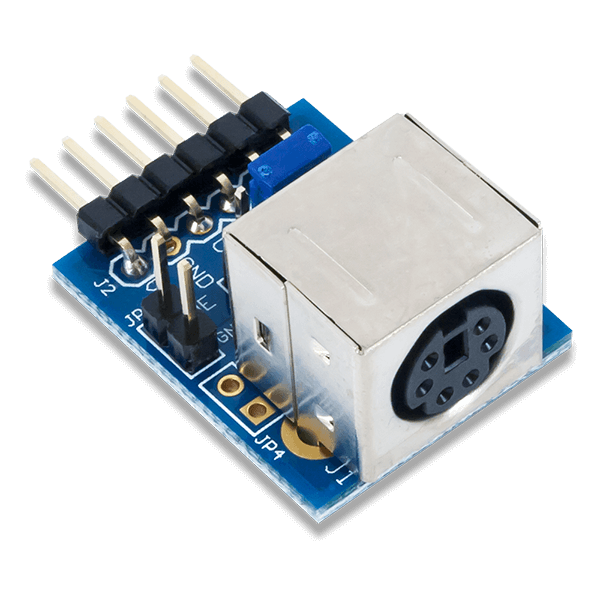

PMOD-PS2 — для подключения PS/2 клавиатуры. Я такой готовый купить забыл, так что пришлось сделать его самому. Заодно поставил туда DC-DC преобразователь 3.3->5В так как имеющаяся у меня клавиатура от 3.3В не заработала.

На Zybo есть USB Host, но он подключен к PS-части. Если планируется PL-проект, то потребуется подключить к плате отдельный USB host.

Полная спецификация протокола USB (с поддержкой HOST и всех типов устройств) очень сложна для реализации на FPGA, к тому же интерфейс USB довольно высокочастотен. Разумным компромиссом является подключение внешнего конвертера физического уровня например по интерфейсу ULPI, для работы с ULPI можно найти готовый IP-модуль на Verilog/VHDL. Можно также подобрать другую плату, на которой уже есть USB host для работы с клавиатурами и мышками (у Digilent это, например, Nexus 4 DDR).

Начало работы с Xilinx Vivado

Проекты для Xilinx (в данном случае речь о 7-й серии чипов) создаются в Xilinx Vivado. Поскольку мы не планируем использовать High-end чипы (UltraSCALE/UltraSCALE+), для наших целей подойдёт бесплатная Xilinx Vivado WebPACK edition. Регистрируемся на xilinx.com, скачиваем её и устанавливаем.

Для работы с Zybo нам потребуется скачать и добавить в Vivado пакет Vivado Board Files, содержащий описание интерфейсов, имеющихся на плате, частотные характеристики чипа и тому подобное. Скачиваем его с сайта Digilent (а точнее с GitHub) и добавляем в Vivado.

Также понадобится файл ресурсов, в котором описано соответствие контактов чипа номерам выводов разъёмов платы. Находим нашу плату, в данном случае Zybo на GitHub/Digilent и скачиваем.

И напоследок сделаем первый проект на Verilog. Этот проект нам в дальнейшем потребуется для создания контроллера клавиатуры БК-0010.

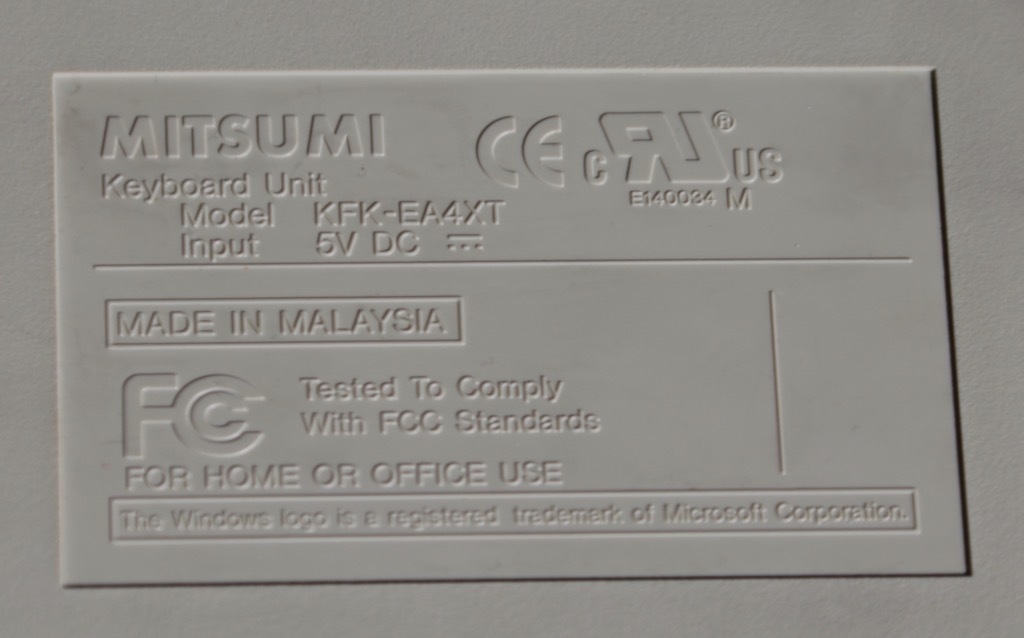

У меня есть вот такая раритетная клавиатура Mitsumi с интерфейсом PS/2:

ishevchuk в своём проекте использовал вот этот контроллер для работы с PS/2 клавиатурой.

Возьмём его и мы и слегка переделаем. Контроллер всем хорош кроме того, что в нём жестко зашита тактовая частота 50 MHz. Такой частоты у нас в проекте БК-0010 не будет, кроме того, хардкодить такие вещи нехорошо. Создаём новый проект в Vivado, скачиваем файлы контроллера и задаём тактовую частоту в виде параметра:

module Altera_UP_PS2_Command_Out #

(

parameter CLOCK = 100,

// Timing info for initiating Host-to-Device communication

// when using a 50MHz system clock

parameter CLOCK_CYCLES_FOR_101US = (CLOCK * 101), // 5050;

parameter NUMBER_OF_BITS_FOR_101US = $clog2(CLOCK_CYCLES_FOR_101US),

parameter COUNTER_INCREMENT_FOR_101US = 1,

// Timing info for start of transmission error

// when using a 50MHz system clock

parameter CLOCK_CYCLES_FOR_15MS = (CLOCK * 15000), // 750000;

parameter NUMBER_OF_BITS_FOR_15MS = $clog2(CLOCK_CYCLES_FOR_15MS),

parameter COUNTER_INCREMENT_FOR_15MS = 1,

// Timing info for sending data error

// when using a 50MHz system clock

parameter CLOCK_CYCLES_FOR_2MS = (CLOCK * 2000), // 100000;

parameter NUMBER_OF_BITS_FOR_2MS = $clog2(CLOCK_CYCLES_FOR_2MS),

parameter COUNTER_INCREMENT_FOR_2MS = 1

)Некоторые модули в составе проекта в своём названии имеют слово Altera. На Xilinx это им работать не мешает, из уважения к разработчику я переименовывать их не стал.

Кроме того, изменим полярность сигнала RESET, у стандартных IP Xilinx сброс происходит при подаче 0 на вход RESET.

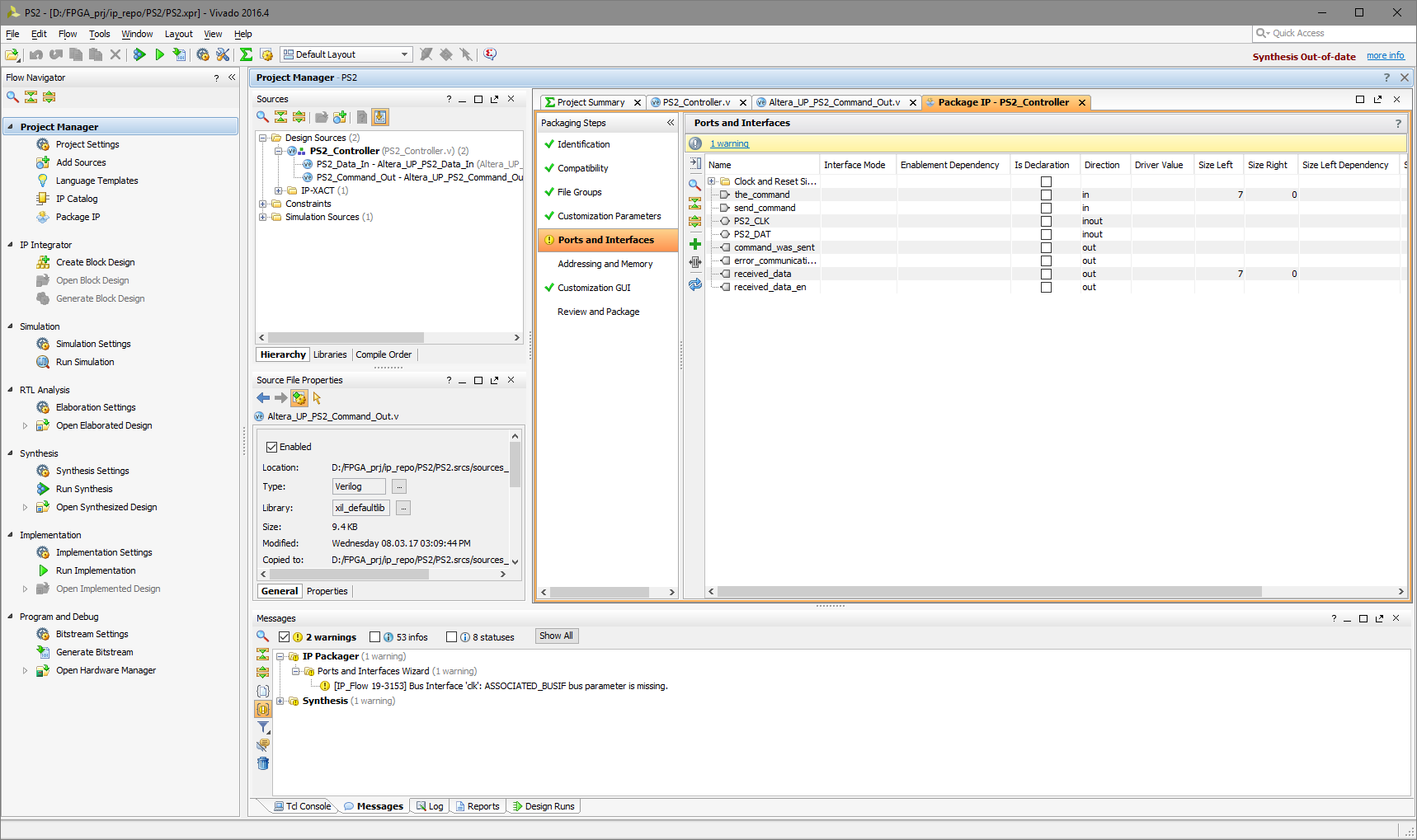

Для удобства работы оформим проект в виде IP. В Vivado есть встроенный инструмент, который это делает, он вызывается через Tools->Create and Package new IP. Входы и выходы головного файла проекта станут входами и выходами нашего нового IP. Vivado пытается сама определить тип портов, анализируя их название. В данном случае нам придётся вмешаться в этот процесс и исключить порт PS2_CLK из числа Clock and Reset Signals, чтобы уменьшить число Warnings при дальнейшей сборке проекта. PS2_CLK нельзя назвать полноценным синхросигналом, поскольку его частота лишь несколько десятков килогерц.

Инструмент весьма гибкий, мы можем не только задавать тип портов, но и управлять различными параметрами, задавать опции условной компиляции, менять внешний вид IP в зависимости от параметров. В данном проекте у нас есть два параметра — Initialize Mouse (выбор устройства — клавиатура или мышь) и Clock (тактовая частота в мегагерцах). Вопросы условной компиляции мы рассмотрим позже, когда будем писать модуль для работы с шиной MPI.

Подключаем Git к Vivado

Напоследок (а вообще это конечно нужно делать сразу после создания нового проекта) прикрутим к Vivado Git. Исходные тексты на Verilog/VHDL, constraints, описания компонент, описания интерфейсов IP-модулей, сам проект и прочее представляют собой текстовые файлы, с ними всё просто. Но есть одна сложность — в файле проекта (он в формате XML) имеются абсолютные пути к исходным текстам, это может вызвать некоторые проблемы при переносе проекта между машинами. Одно из решений — воспользоваться готовым инструментом (написанным инженерами Xilinx), этот инструмент на основе проекта Vivado создаёт переносимый tcl-скрипт, который при запуске на целевой машине создаёт там проект, идентичный оригинальному. К этому инструменту был дописан враппер, автоматизирующий создание tcl-скрипта, заполняющий файл .gitignore, осуществляющий обработку ошибок ввода и тому подобное. После установки этого враппера появляется возможность работать с Git прямо из tcl-консоли Vivado.

Заливаем проект в железо

Проверим теперь, как это всё работает. Закроем проект PS2 контроллера и создадим тестовый проект, принимающий скан-коды с клавиатуры и выдающий их на семисегментный индикатор. В этом проекте мы не напишем ни строчки Verilog-кода, а будем собирать схему из готовых IP-модулей.

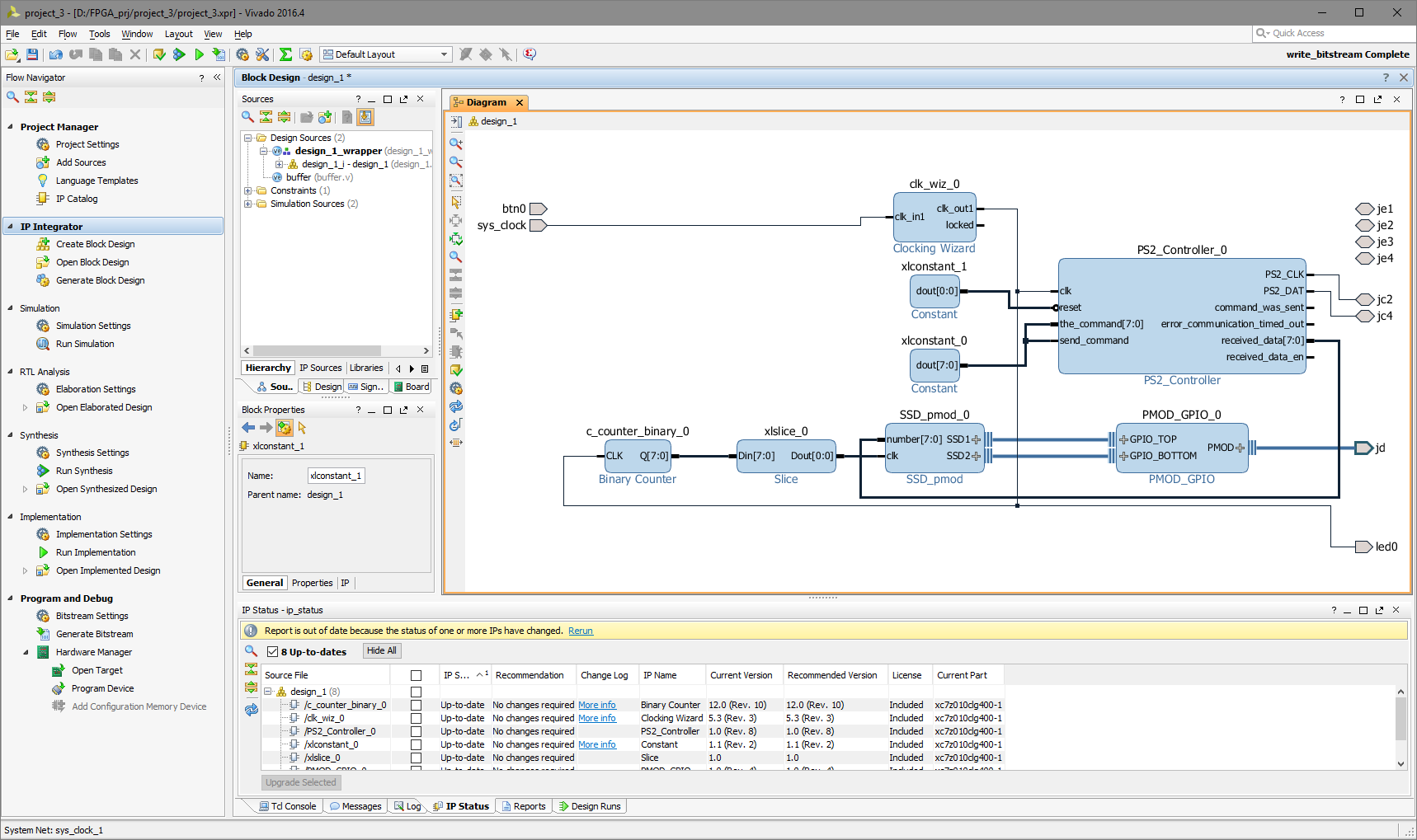

В IP Integrator создаём новый блочный дизайн, добавляем в него IP и соединяем их, пока не получится вот такая схема:

Здесь были использованы следующие IP:

Clocking wizard Модуль создания синхросигналов. Предназначен для создания синхросигналов (до 6 штук) с различной частотой и скважностью (в данном случае одного меандра 100MHz). На вход ему подаётся системный клок (125 MHz). Использует ресурс PLL, выходные синхросигналы распространяются через соответствующие ресурсы кристалла. Стандартный модуль Xilinx.

Binary Counter. Настраиваемый делитель, в данном случае 8-битный. Стандартный модуль Xilinx.

Slice. Делитель шины, в данном случае вытаскивает старший бит из Binary Counter, образуя таким образом делитель на 256. Стандартный модуль Xilinx.

Вообще с синхросигналом такие вещи делать нельзя, нужно брать ещё один выход из Clocking Wizard и корректно настраивать Clock Domain Crossing. Но в данном случае для работы SSD_pmod годится любая частота от сотни герц до сотен килогерц, не синхронизированная вообще ни с чем.

SSD_pmod. Модуль, выводящий байт в шестнадцатеричном виде на двухзначный семисегментный индикатор Digilent PMOD-SSD. Байт поступает на вход модуля. Исходный текст модуль выложен на GitHub.

PMOD_GPIO. Модуль, описывающий работу с сигналами в разъёмах PMOD. В зависимости от типа модуля, подключенного к разъёму, используются различные протоколы — GPIO, SPI, I2C, UART. Я взял за основу модуль написанный Digilent для поддержки своих PMOD, и слегка изменил его. Исходный текст модуль выложен на GitHub.

Модуль Constant. Это просто константа 0 или 1. Мы не используем в данном случае передачу в сторону клавиатуры, так что на входы send_command и the_command подан 0, а на вход reset подана 1 (в окончательном проекте у нас будет полноценная схема сброса).

Наконец PS2_controller, модуль, который мы создали на предыдущем шаге. Не забудьте указать путь к нему в свойствах проекта, чтобы его возможно было добавить.

У нас используются следующие внешние соединения:

sys_clock Синхросигнал 125MHz от внешнего генератора на плате (пин L16). Используется для запуска PLL.

PMOD_C К порту C подключена клавиатура, используются биты JC2 (W15) и JC4 (T10)

PMOD_D К порту D подключен семисегментный индикатор, используются все 8 бит.

Сохраняем блочный дизайн, генерируем враппер на Verilog (Generate HDL Wrapper...), компилируем проект (Generate Bitstream), заливаем его через JTAG в плату (Open Hardware Manager, Open Target, Program Device). Теперь при нажатии кнопок на клавиатуре их скан-коды будут выводиться на семисегментном индикаторе:

8'h4E — это '-'

Ссылки

Для желающих попробовать всё это на железе, все исходники выложены на Github:

> Враппер для работы с Git из Vivado

Кроме этого потребуется установить:

> Описание интерфейсов и плат Digilent, в том числе Zybo

> Раз и два — вспомогательные модули для вывода шестнадцатеричных чисел на семисегментный индикатор

> Контроллер PS2-клавиатуры

> Модуль в котором всё это соединяется вместе

Для установки модуля необходимо скачать его с Github и запустить .tcl файл, лежащий в корне, из под Vivado

Комментарии (44)

erwins22

04.05.2017 17:29А какая эффективная частота работы? (эффективная в данном случае эквивалентна частоты на которой работало бы БК)

Skyroger2

04.05.2017 18:39На процессорный модуль подаётся ровно та же частота, что и в оригинальном БК — 3 MHz. Производительность при этом получается такая же с точностью до погрешности измерений, что говорит о том, что производительность на такт примерно одинакова.

Конечно используя современные технологии можно добиться гораздо лучшей производительности на такт, сделать конвейер и т.п., но мне было интересно вписаться примерно в тот же транзисторный бюджет. По модулю CPU у меня получилось — LUT — 2398, FF — 557. Это на мой взгляд сопоставимо с КР1801ВМ1 — около 18000 транзисторов.

mxms

04.05.2017 22:07Гмм. Там тот же монитор (биос по-современному), EMT, машинные коды PDP-11 и организация памяти с точки зрения программ, что и в оригинальной БК-0010?

Skyroger2

05.05.2017 07:58+1Да, разумеется. Образы оригинальных ПЗУ монитора, блока тестов, языков Фокала и Бейсика доступны в Интернете. Организация памяти, система команд, контроллер клавиатуры, таймер и прочее полностью эмулируется.

Поскольку это не реализация «вентиль в вентиль» (были и такие попытки на FPGA), аппаратные баги 1801ВМ1 я эмулировать не стал.

NumLock

05.05.2017 07:29На всякий случай. Реализация БК-шки на Altera DE1.

https://code.google.com/archive/p/bk0010/

https://github.com/andykarpov/bk0010-wxeda

Skyroger2

05.05.2017 08:02Тот, что на Google code видел, тот, что на GitGub нет, спасибо за ссылку.

Пробежался по коду, во всяком случае видно, что некоторые неудобные особенности системы команд PDP-11 там обрабатываются корректно. Авторы молодцы.

Videoman

05.05.2017 10:51+2Какие такие неудобные особенности системы команд :)? По сравнению с Intel, система команд PDP-11 была изящна как лань. Мне ассемблер БК до сих пор снится. Да мы, вообще, могли писать в машинных кодах, благодаря хорошей систематизации битовых полей в кодах инструкций. Это я вам как заядлый БКашник говорю.

Skyroger2

05.05.2017 11:41О, для программиста система команд просто идеальна, я в своё время довольно много писал на ассемблере для разных архитектур. Но когда начинаешь реализовывать это в железе, натыкаешься на всякие неочевидности.

Например, команда ADD #1, R0 может вызвать переполнение (что отражается в бите C), команда INC R0, которая по сути тоже прибавляет 1 к R0, на содержимое бита C влияния не оказывает. Какова была логика у фирмы DEC сделать своё ALU в 70-х именно так, мне не известно, не исключаю, что у них просто так получилось.

Videoman

05.05.2017 12:07Да, интересно, хотя V (Overflow) ставится. А можно еще вопрос: на сколько подробно вы собираетесь эмулировать все эти особенности архитектуры. Возьмем, для примера, тайминги:

например «очистка» памяти нулями CLR (R0)++, в силу какой-то экономии и реализации адресации в железе, делалась, фактически, в три операции — загрузка из памяти старого значения, обнуления, записи нового значения. Из-за этого быстрее было так: CLR R0, MOV R0,(R1)++. Такие вещи будут учитываться? Я просто, в свое время, написал эмулятор и там такие вещи работали не так как на реальной БК.

Skyroger2

05.05.2017 12:34+1Это действительно очень тонкий момент. Если посмотреть на оригинальные тайминги PDP-11, то там видно, что например команда MOV R0, @#1000 выполняется за меньшее время и требует на одно обращение к памяти меньше, чем ADD R0, @#1000 именно за счёт того, что нам не нужно старое значение по адресу 1000. У меня сделано так же.

CLR в моей текущей реализации старое значение не читает. Тут дело не только в таймингах, а ещё и в том, что на этапе чтения из памяти может случиться ошибка шины.

Так же требуется специальная обработка для команд CLR, TST, CMP, BIT, JMP, JSR — где-то нам не нужно старое значение, где-то новое, где-то косвенность адресации уменьшается на один уровень.

Videoman

05.05.2017 16:18+1Кстати у меня есть версия почему это реализовано именно так. Возможно в те времена экономили везде и на всем и делали только то, что требовалось от команды. У команды ADD была расширенная версия ADC в которой и использовался флаг C (Carry) в случае расширенной беззнаковой арифметики,. т.е. пара команд:

ADD R0, R2

ADC R1, R3

позволяла уже складывать 32-битные числа в регистрах (R0,R1)+(R2,R3). А для INC, DEC такой необходимости уже не было.

mxms

07.05.2017 17:34Где то попадалась в своё время таблица за сколько тактов выполняется на БК та или иная команда в зависимости от метода адресации.

Skyroger2

08.05.2017 07:33Именно за БК не скажу, а по оригинальной PDP-11 эта информация есть в PDP-11 processor handbook, в самом конце.

Videoman

08.05.2017 13:00Именно по БК, тайминги присутствуют в различных журналах в статьях Ю. Зальцмана

GarryC

05.05.2017 17:39+2Нет нет нет, это было сделано специально, «так получилось» было не для DEC!

Простите за эмоцию, я просто очень любил PDP в их реинкарнации ДВК а первая любовь не ржавеет.

DEC специально так сделала для облегчения работы с длинными данными, чтобы команды смещения индексного регистра либо изменения счетчика не трогали бита переполнения для следующих разрядов, и в библиотеках это красиво использовалось.

Videoman

05.05.2017 17:56Кстати, круто!!! Тоже вполне логично. Но это только подтверждает, что все не случайно, что все команды были продуманы, да еще и спроектированы для каскадной работы в связках. Обожаю PDP-11! Не перестаю восхищаться.

mxms

07.05.2017 17:40Инженерная мысль DEC и программная реализация многих модулей RT-11 с кучей гениальных хинтов в реализации на ассемблере, многому меня научившие в своё время, до сих пор впечатляет.

mxms

07.05.2017 17:46Ну тут надо понимать, что уродливость системы команд Intel в сравнении с DEC была обусловлена архитектурой: когда у Intel использовалась раздельные шины данных и адреса, у DEC она была общей. Отсюда и растут эти приятности в виде адресации ячейки памяти как регистра или косвенные адресации.

Skyroger2

08.05.2017 07:28+1Честно говоря, не вижу связи между косвенной адресацией и раздельностью шин адреса и данных. DEC использовал архитектуру с равноправными регистрами общего назначения, Intel со специализированными (аккумулятор, индексные, счётчик и так далее). Вот отсюда и разница.

Videoman

08.05.2017 13:12А вы не могли бы более развернуто объяснить какая связь между шинами и адресацией, тем более, что, насколько мне известно, шина у них стала раздельная начиная с 286-го процессора, а архитектура закладывалась гораздо раньше. А z80, по вашему, по той же причине имеет схожую архитектуру?

Всегда считал, что планировалось, что отдельные команды для доступа к портам, будут экономить адресное пространство, так как имеют, по сути, своё отдельное. Но время все расставило на свои места, и сейчас, масса устройств проецируют себя в адресное пространство ядра напрямую, причем большими диапазонами. Т.е. подход DEC победил.

mxms

08.05.2017 14:14У Intel начиная с 8086 раздельные шины данных и адреса. Другое дело что до, как раз, если я точно помню, 286 использовались общие контакты на корпусе для передачи и данных и адресов.

Я пришёл к этому выводу лет 25 назад когда активно программировал ДВК и БК-0010 на Ассемблере и в машинных кодах. Там неплохо видна эта идея, если машинный код представить в двоичном виде, а затем сэмулировать его обработку на АЛУ и шине. Даже писал что-то вроде реферата для себя на сей счёт. Но вот сходу так тезисно сейчас не изложу.

GarryC

08.05.2017 21:14Не совсем так. У DEC была и шина с раздельными данными и адресом при той же системе команд и даже чуть расширенной.

Дело в другом — ортогональная система команд — то есть все регистры равноправны и к ним применимы все способы адресации, то есть получается полная таблица — отсюда название — требует бОльшего количества железа, нежели специализированные регистры и имеет меньшее быстродействие при прочих равных условиях — вот почему 8080 встала на этот скользкий путь.

«За все в этом мире надо платить».

r44083

05.05.2017 09:46Хочу обратить внимание на спорную политику Xilinx в плане своих продуктов: они выпустили прекрасную IDE Vivado, но эта IDE подходит только для огромных FPGA 7-го поколения (Virtex-7, Kintex-7, Artix-7 и Zynq-7000).

Остальное множество их FPGA ниже 7-го поколения (в том числе Spartan) идут лесом. С ними можно использовать только IDE Xilinx ISE (последний релиз 3 года назад).

ParyginM

05.05.2017 11:31Есть промежуточный продукт между Vivado и ISE: PlanAhead. Поддерживает и старые камни (3, 6) и седьмое поколение (но не самые последние).

Skyroger2

05.05.2017 12:12Меня как любителя это никак не задело, всё же 7-е поколение FPGA появилось аж в 2010 году, Artix-7 в 2011, Zynq-7000 если не ошибаюсь в 2012. Предполагаю, что это важно для тех, кто занимается коммерческой разработкой под FPGA и поддерживает старые проекты на Spartan.

И ещё жаль CPLD. Новых нет, а старые поддерживаются только в ISE.

antonsosnitzkij

05.05.2017 11:32Спасибо за статью!

Сделать с нуля собственный процессор с контроллером шины и обработкой прерываний

К сожалению, этот пункт почти никак не отображен в статье.

Под собственным Вы подразумеваете использовать soft-процессор, реализованный на HDL? Если да, то это и вправду интереснее чем Microblaze, но в этой области есть интересная возможность работать с MIPS'ом на FPGA, что подробно рассказано и в Харрисах и в статьях Юрия Панчула.

Skyroger2

05.05.2017 11:48Да, естественно, для того чтобы сделать БК-0010, нам надо сделать soft-процессор на HDL с системой команд PDP-11. Microblaze нам тут не подойдёт, MIPS тоже, к тому же я не думаю, что про MIPS кто-то расскажет лучше, чем YuriPanchul

За одну статью обо всём проекте БК-0010 рассказать просто невозможно, про процессор будет отдельная статья, я думаю четвёртая по счёту. Постараюсь всё написать быстро!

EndUser

05.05.2017 12:01А нам говорили, что язык БК-0010Ш определяется воткнутой микросхемой. У нас был ФОКАЛ и не было Бейсика. Но в том возрасте я, во-1, не знал какие языки могут быть, во-2, не осознал зачем нужен компьютер вообще. Зачем писать «Привет, человек!», зачем расставлять астериски в виде ёлочки… Я только на первом курсе прозрел, что философское место компьютера быть инфо-хабом для широких масс населения, но это меня зажгло на очень много лет — до сих пор тлеет ;-)

Videoman

05.05.2017 12:19Так и было. Язык был прошит в ПЗУ по адресам — первые 8KБ занимал «монитор», а дальше 24KБ сам язык. Не помню как в БК-0010Ш (вариант для школ), а в БК-0010-01 там лежал обалденный Вильнюс-86 Бейсик (по моему клон GW-Basic). При подключении блока МСТД со своим ПЗУ, оригинальные ПЗУ отключалось, а по этим адресам проецировался Фокал. Но он занимал 8KБ и был намного примитивней по возможностям. Также он был намного медленнее бейсика, т.к. полностью интерпретировался, в отличие от первого, который сначала компилировал программу в промежуточный код (это была интересная смесь машинных команд и данных), а потом уже быстро выполнялся.

Skyroger2

05.05.2017 12:39Да, так и было. В 8 килобайт сумели засунуть полноценный интерпретатор с поддержкой арифметики с плавающей точкой (пусть числа были пятибайтовые, но всё же). Ассемблерный код интерпретатора просто чудовищный — использовались все возможности процессора и самые тяжелые режимы адресации.

nzeemin

05.05.2017 15:26Вильнюс-Бейсик — это не клон, это с нуля написанный язык, сразу для нескольких советских pdp11-like машин: ДВК, БК, УКНЦ. Исходный код можно найти, много где лежит.

Но авторы были под сильным впечатлением от Yamaha MSX, поэтому по ряду вещей этот язык похож на Basic MSX.

https://ru.wikipedia.org/wiki/%D0%91%D0%B5%D0%B9%D1%81%D0%B8%D0%BA_%D0%92%D0%B8%D0%BB%D1%8C%D0%BD%D1%8E%D1%81

Videoman

05.05.2017 16:07Я не точно выразился, и имел ввиду не клон — в плане исходного кода. Это клон — в плане синтаксиса самого Бейсика, так как их было много вариантов на тот момент. А то, что создатели молодцы и проделали огромную работу и все сами написали с нуля — я в курсе.

nzeemin

05.05.2017 15:22Из обсуждений у меня сложилось впечатление что вы реализуете процессор с нуля, используя описание системы команд.

Между тем, уже существует Verilog реализация реального 1801ВМ1 — полученная в результате реинжиниринга реального процессора. Все подробности вот в этой теме:

http://zx-pk.ru/threads/23978-tsifrovaya-arkheologiya-1801-i-vse-vse-vse.html

Skyroger2

05.05.2017 15:56+1У Вас сложилось совершенно верное впечатление.

Проект, на который Вы ссылаетесь очень интересен прежде всего тем, что люди проделали огромную работу и нашли много плохо документированных особенностей 1801ВМ1 в том числе аппаратные баги (действительно баги, например там в каком-то месте просто не хватает транзистора). Целью того проекта было именно сделать аналог 1801ВМ1 на современной элементной базе, то есть сделать некое изделие, которое можно впаять вместо ВМ1 в БК-0010. Этой цели, насколько я понимаю, добились.

Взять тот проект и переделать его в soft core не получится. Во-первых, в 1801ВМ1 использовались двунаправленные и мультиплексированные шины, в качестве внутренних шин в FPGA такие использовать нельзя. Во-вторых, если посмотреть на Verilog-исходники того проекта, то там практически gate-level дизайн. То есть описано, что сигнал на выводе таком-то представляет собой функцию в нормально дизъюнктивной форме от сигналов таких-то. Понятно, что это следствие обратного инжиниринга, но сюда невозможно ни добавить новую команду, ни сделать процессор с таким же набором команд, но с отдельными шинами для адреса и данных.

Наконец основная задача у меня — показать, что можно сделать с помощью Vivado. Проект БК-0010 — лишь средство сделать это интересным.

GarryC

05.05.2017 17:46Кстати, обратите внимание на Электронику 100/25 в которой была совместимая система команд, но чуть расширенная и другая внешняя шина.

Просто в ней процессор был сделан на чистой логике и она была микропрограммная, причем тексты всех микропрограмм были приведены в руководстве и я своими руками чинил процессор при помощи блока микропрограммной отладки.

И схемы всех плат были и даже с таблицами прошивок ПЗУ.

Это я к тому, что можно поискать чистый микрокод, а не реверсить его из описания команд.

Skyroger2

05.05.2017 19:35Спасибо.

Да я собственно процессор и всё остальное уже сделал, у меня есть работающий вариант эмулятора. Мне осталось сделать описание наиболее интересных моментов и выложить здесь (и оставшуюся часть исходников на GitHub).

На БК-0010 (1801ВМ1) были базовые команды PDP-11 плюс некоторые из расширенного набора (XOR, SOB).

Videoman

05.05.2017 20:06+1Вот кстати, если что, эмулятор который вырос из моего: Эмулятор БК-шек с исходниками. Я его года 2 делал, поддержку дисков, ленты, нескольких аппаратных конфигураций. Дальше навалилась работа, семья и я не смог продолжать. Но бросать дело, совсем, было очень жалко, поэтому я выложил исходники в сеть на сайте своего эмулятора. Потом, вот, человек, взял их и за основу и продолжил дело. Он очень сильно развил эмулятор, исправил ошибки, поддержал современное железо. В общем, я очень благодарен ему и слежу за сайтом. Свое имя он почему-то скромно умалчивает на сайте. Я с ним связывался, но дано, и забыл как его зовут. Может быть он и появится тут и присоединится.

Nerten

09.05.2017 14:14Никогда бы не подумал что был БК с механической клавиатурой.

В моём детстве он был таким:

Skyroger2

09.05.2017 14:43Строго говоря, БК-0010 был с плёночной клавиатурой, как на вашем фото. С механической был БК-0010-01. Дребезжала она очень сильно.

В 90-е выпускалась хорошая клавиатура МС-7008.01, совместимая с БК, значительно более качественная.

dtyurev

10.05.2017 09:55Принимайте в клуб написавших эмулятор БК0010-01.) Кстати, тут есть авторы известных игр? Напишите названия своих игр и как подписывали игры.)

Skyroger2

10.05.2017 09:57Под БК-0010 я писал кое-какие системные программы, не игры. А вот под Орион-128 написал немало. Это было позже, в 90-х.

de1m

Может быть немного не в тему вопрос, можно ли всё это (программирование итд.) делать под линуксом, как-то я не всречал точного мнения. И это касается именно Xilinx.

Skyroger2

Да можно, Xilinx Vivado распространяется в виде дистрибутивов под Windows и под Linux.

Некоторые предпочитают часть работы делать на Windows, часть на Linux. Так тоже можно.