Каким образом студент или университетский исследователь может не просто спроектировать микросхему, но и получить ее в свои руки с фабрики? Ведь начальный взнос за фабричное производство микросхем для коммерческих целей как правило превышает миллион долларов? К счастью, такой путь существует за гораздо меньшие деньги — через организацию, которая называется Europractice. Я записал видео интервью с ее директором Carl Das.

Каким образом студент или университетский исследователь может не просто спроектировать микросхему, но и получить ее в свои руки с фабрики? Ведь начальный взнос за фабричное производство микросхем для коммерческих целей как правило превышает миллион долларов? К счастью, такой путь существует за гораздо меньшие деньги — через организацию, которая называется Europractice. Я записал видео интервью с ее директором Carl Das.А если студент вырастет и захочет завалить спроектированными его компанией микросхемами все континенты, но не знает с чего начать? И на это у меня есть ответ — я записал также видео интервью с Mark Scrivener, директором eSilicon’s Semiconductor Manufacturing Services. Мы с Марком вместе рассчитали по пунктам расходы и себестоимость условного российского чипа, который будет производится в больших объемах в 2016-2020 годах.

Эти и другие видео я записал на конференции Design Automation Conference (DAC), которая прошла на прошлой неделе в Сан-Франциско. Конференция DAC фокусируется на индустрии Electronic Design Automation (EDA), которая обслуживает проектировщиков микросхем. Среди людей, которых я проинтервьировал на прошлой неделе — гуру языка описания аппаратуры Verilog Джон Сангвинетти, руководители компаний, которые разрабатывают софтверные инструменты для разработчиков микросхем, разработчики плат с ПЛИС, один из основателей зеленоградской компании по проектированию микросхем ЭЛВИС Александр Галицкий и другие специалисты и бизнесмены.

Итак:

Сначала видео интервью с Carl Das, который является Director ASIC Services at IMEC, который отвечает за Emerging Business Program с TSMC и за Europractice IC Service. Расшифровываю, что это значит:

ASIC — Application-specific integrated circuit, специализированная микросхема, например которая стоит в айфоне.

IMEC — Interuniversity Microelectronics Centre — межуниверситетский центр исследований в области микроэлектроники, в котором работают около 2000 человек. Располагается в Бельгии и Нидерландах, с офисами в других странах.

Emerging Business Program — когда новой компании нужно попробовать выпустить микросхемы малым тиражом.

TSMC — Taiwan Semiconductor Manufacturing Company — крупнейший контрактный производитель микросхем в мире

Europractice IC Service — специальный сервис обслуживания университетов, который за сравнительно небольшие деньги (тысячи евро вместо сотен тысяч) предоставляет доступ к легально лицензированному программному обеспечению для разработки микросхем, а также, снова за сравнительно небольшие деньги (десятки тысяч евро вместо миллионов) к производству микросхем на фабрике.

А теперь видео интервью с Mark Scrivener, Director SMS Sales, eSilicon

SMS — это Semiconductor Manufacturing Services — сервисы по производству полупроводниковых изделий

eSilicon — компания, которая в начале XXI века стала пионером новой модели бизнеса — сервисы по разным физическим аспектам проектирования микросхем, интеграция с блоками от различных проектировщиков и взаимодействие с фабриками. Эта компания стала знаментой после того, как они сделали ASIC для iPad.

Короче, если вы спроектировали на логическом уровне новый микропроцессор или DSP, отверифицировали его функциональность на симуляторе, определили что он вписывается в бюджет тайминга после синтеза, и при этом вы не хотите возиться с физическими аспектами проектирования микросхемы (place & route, parasitics extraction, design rule check), а также если вам хочется минимизировать разбирательство с юристами в других странах, как лицензировать разные IP блоки, и если вы не очень любите общение с фабриками на Тайване или в Дрездене напрямую — то eSilicon для вас.

На видео Марк демонстрирует, как любой российский школьник может зарегистрироваться у них на сайте и ввести параметры чипа, который он собирается произвести ( на сколько нанометров, какого размера, есть ли на нем SRAM и аналоговая часть ), какой тестер на фабрике использовать и время тестирования, а также планы по выпуску в разные годы — 100,000 в первый год, 500,000 во второй и т.д.

После этого вебсайт подумает и сгенерирует PDF файл на много страниц, где подробно расписываются все расходы и себестоимость чипа. В частности вы можете прикинуть себестоимости, с которыми можно произвести некоторые гипотетические будущие российские чипы.

И самое интересное — этот PDF файл является legally binding quote, т.е. если у школьника, играющегося с сайтом, найдется пара миллионов долларов карманных денег на начальный взнос и желание произвести чип, то eSilicon имеет юридическое обязательство предоставить ему такую возможность по опубликованной цене:

www.esilicon.com/asic-design-services/star-online-tools/gdsii-quoting-portal

Аналогом Europractice в США является MOSIS, а конкурентом eSilicon является в частности Open-Silicon.

Пока мы обсудили кульминацию микроэлектронного проекта — изготовление микросхемы на фабрике. Но как такой проект начинается?

В последние 25 лет дизайн микросхемы чаще всего пишется на языке описания аппаратуры Verilog (в Европе и у военных — VHDL), после чего специальная программа (logic synthesis) превращает дизайн в граф из проводов и логических примитивов, другая программа (static timing analysis) сообщает дизайнеру, вписывается ли он в бюджет скорости, а третья программа (place-and-route) раскладывает этот дизайн по площадке микросхемы.

Когда дизайн проходит все этапы: кодирование на верилоге, отладка, верификация, синтез, static timing analysis, floorplanning, place-n-route, parasitics extraction и т.д. — получается файл под названием GDSII, который отправляют на фабрику, и фабрика выпекает микросхемы. Самые известные фабрики этого типа принадлежат компании Taiwan Semiconductor Manufacturing Company или TSMC.

Я проинтервьировал человека, который является для языка Verilog примерно тем же, кем являются для языка Си Керниган и Ричи. Джон Сангвинетти — ранний гуру верилога со времен 1980-х, основатель компании Chronologic Simulation, которая подарила миру быстрый симулятор верилога VCS (Verilog Compiled code Simulator), который сейчас использует большинство разработчиков крупных чипов. Джон поприветствовал российских молодых людей, которые изучают Verilog и высказал пару мыслей о высокоуровневом синтезе и его применимости к разработке out-of-order процессоров:

Применим ли высокоуровневый синтез к разработке out-of-order процессоров?

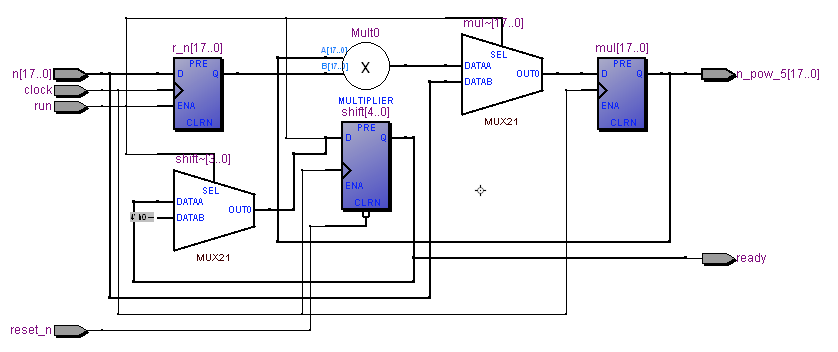

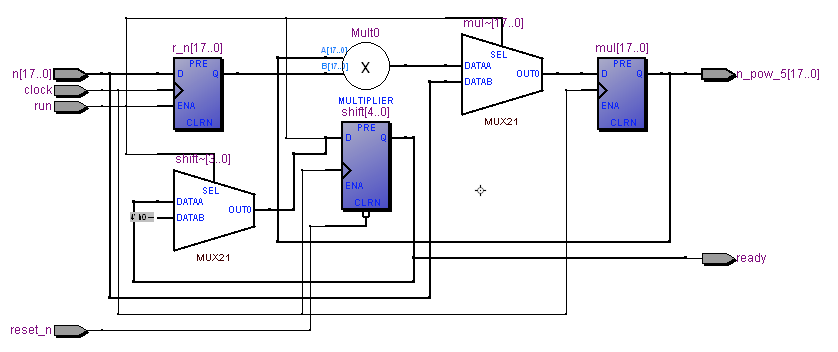

Для тех читателей, кто не в курсе, как выглядит Verilog, привожу один из примерчиков, которые я написал для студентов, вместе со схемой, в которую он транслируется («синтезируется»):

module pow_5_implementation_3

(

input clock,

input reset_n,

input run,

input [17:0] n,

output ready,

output [17:0] n_pow_5

);

reg [4:0] shift;

always @(posedge clock or negedge reset_n)

if (! reset_n)

shift <= 0;

else if (run)

shift <= 5'b10000;

else

shift <= shift >> 1;

assign ready = shift [0];

reg [17:0] r_n, mul;

always @(posedge clock)

if (run)

begin

r_n <= n;

mul <= n;

end

else

begin

mul <= mul * r_n;

end

assign n_pow_5 = mul;

endmodule

На конференции продавали книжки по верилогу:

А вот стенд компании Doulos Training которая за деньги учит инженеров разных компаний языкам Verilog и VHDL, верификации и связанным технологиям. У этой компании есть несколько конкурентов, в частности Willamette HDL и Sutherland HDL:

Также я встретил начальников отделения верификации в Synopsys, эта группа сейчас поддерживает симулятор верилога VCS.

Глава отделения — Manoj Gandhi (слева), Executive Vice President and General Manager, Verification Group, а справа — Jayant Nagda, он был менеджером реализации SystemVerilog в VCS в начале 2000-х:

У Synopsys был большой стенд на выставке, это одна из троицы крупных компаний индустрии программных стредств разработки электроники, два других члена троицы — это Cadence и Mentor Graphics:

Cadence — компания №2 в EDA. В декабре прошлого года они проводили семинары в Москве, точнее в МИФИ:

На стенде Cadence демонстрировали новый тул для синтеза под названием Cadence Genus — по-видимому конкурент Synopsys Design Compiler — основного тула для логического синтеза, используемого разработчиками ASIC-ов:

Mentor Graphics — компания №3 в EDA. Еще в 1996 году я пристроил одну группу в МФТИ делать проекты для Mentor Graphics прямо из Долгопрудного:

Помимо трех крупных компаний в индустрии EDA есть игроки поменьше, которые эксплуатируют свои ниши. Одним из таких игроков является компания SILVACO, которая разрабатывает программы для физической части разработки ASIC — моделирования на физическом уровне, проверки правил дизайна, нахождения всяких паразитных эффектов на наноуровне. (Этот этап наступает после разработки дизайна на логическом уровне). В SILVACO работает несколько русских, в частности Алексей Жариков (на видео внизу слева) и Гаяр Усманов (справа).

Мы побеседовали на следущие темы:

1. Можно ли устроить в России стартапы в области физической части разработки микросхем?

2. Что происходит в Беларусии (завод Интеграл как поставщик кадров для EDA индустрии).

3. Способствует ли наличие локального фаба возникновению EDA компаний?

После чего я поговорил с начальником компании (председатель совета директоров) Iliya Pesic, SILVACO Chairman of the Board, он сказал мне, что они расширяются в Восточную Европу и плотно работают с фабриками, от которых получают PDK (Process Design Kit — информация, необходимая программным средствам разработки для поддержки производства на данной фабрике):

Я участвую в конференциях DAC c 1996 года и замечаю, когда те или иные темы становятся модными. Текущая мода — повышенный интерес к тематике ПЛИС / FPGA. Причем эта тематика популярна в этом году не только на DAC, но и среди нетехнических СМИ — в связи с покупкой Интелом компании по разработке FPGA под названием Altera. За $16.7 миллиардов долларов!

Когда в марте по интернету пошли слухи о сделке Intel-Altera, многие журналисты просто не поняли, чем занимается компания, за которую Интел решил уплатить такие бешенные деньги. Один домыслил, что Альтера якобы «главный конкурент интела по процессорам» (при том, что альтеровские FPGA — это вообще не процессоры, хотя процессор может стоять рядом с reconfigurable gates), другой — что Альтера якобы «производитель телекоммуникационного оборудования» (никакого телекоммуникационного оборудования Альтера не производит), третий — что Альтера якобы «контрактный производитель микросхем» аки TSMC (при том, что у Альтеры вообще нет своих фабрик).

Что такое ПЛИС / FPGA я на пальцах объяснил в другом посте на Хабре — Как начать разрабатывать железо, используя ПЛИС — пошаговая инструкция. Но повторим эту информацию снова:

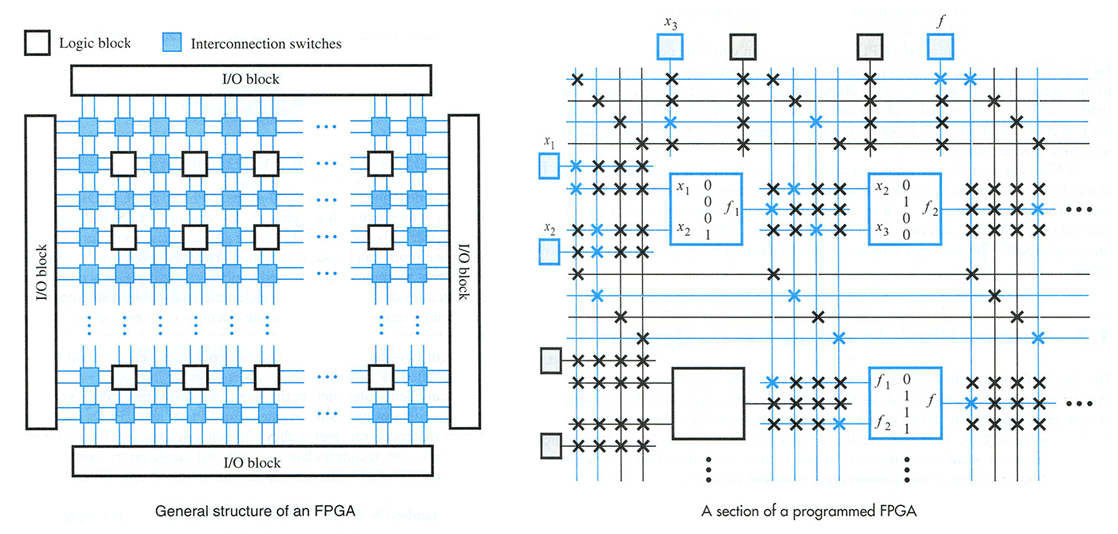

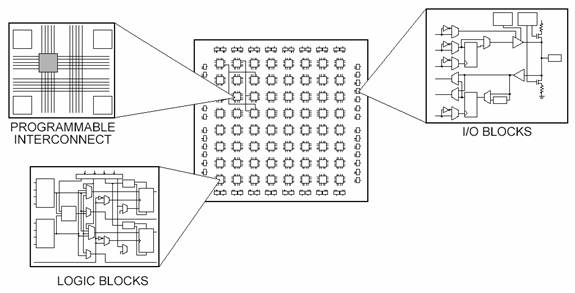

В самом простом варианте FPGA состоит из матрицы однородных ячеек, в функцию каждой из которых можно поменять с помощью мультиплексоров, подсоединенных к битам конфигурационной памяти. Одна ячейка может стать гейтом AND с четырьмя вводами и одним выводом, другая — однобитным регистром и т.д. Загружаем в конфигурационную память последовательность битов из памяти — и в FPGA образуется заданная электронная схема, которая может быть процессором, контроллером дисплея и т.д.

ПЛИС-ы / FPGA — не процессоры, «программируя» ПЛИС (заполняя конфигурационную память ПЛИС-а) вы создаете электронную схему (хардвер), в то время как при программировании процессора (фиксированного хардвера) вы подсовываете ему цепочку написанных в память последовательных инструкций программы (софтвер).

Внизу — схема простейшего блока FPGA, в который входит look-up table (LUT) и flip-flop. Правда в этой схеме не показаны мультиплексоры, которые меняют функцию ячейки, и соединения с конфигурационной памятью.

Диаграммы, иллюстрирующие структуру FPGA:

И еще одна:

В своих предыдущих постах про ПЛИС-ы (1, 2) я писал о студенческих FPGA платах за $80-$150-$300, а теперь посмотрим на производителей «взрослых» плат стоимостью от $5,000 до $50,000 и выше, с быстрыми и большими Xilinx Virtex-7 FPGA. Эти платы используются разработчиками ASIC-ов для прототипирования:

Компания из Германии proFPGA:

Компания из южной Калифорнии Dini Group:

Компания из северной Калифорнии S2C:

Но большие FPGA платы для меня не в новинку — еще в XX веке я участвовал в конференции FCCM (IEEE Symposium on Field-Programmable Custom Computing Machines) в Винной Стране (Wine Country), на которой треть народу были университетские исследователи, треть — проиводители больших FPGA плат и треть — товарищи из армии и ЦРУ, которые использовали эти платы для своих секретных нужд (расшифровывание, обработка сигналов и т.д. — см. ieeexplore.ieee.org/xpl/mostRecentIssue.jsp?punumber=5734&filter%3DAND%28p_IS_Number%3A15334%29&pageNumber=3 )

А вот что было для меня в новинку в этом году — это большое количество новых компаний, которые продают в виде интеллектуальной собственности (semiconductor IP), дизайн блоков из ячеек FPGA, которые можно поместить на ASIC. Вот одна такая компания из Франции, Menta:

Вот еще одна, flexlogix из Silicon Valley:

И еще одна — французская ADICSYS, у основателя которой, Peer Schmitt, я взял видео-интервью, зачем все это нужно. Оказывается, одна из причин использования FPGA на ASIC-е — это чтобы (!) разработчик микросхемы мог утаить самую секретную часть схемы от фабрики (!) Типа 95% микросхемы несекретно, а засекреченная state machine прошивается уже после производства, когда тепленькая микросхема возвращается с Тайваня в Зеленоград:

Потом я встретил группу дефилирующих русских, в том числе Влада и Елену Потаниных, основателей компании Viveng, которая занимается сервисами до аналоговому и mixed-signal (цифровому и аналоговому) дизайну. Компания находится в Silicon Valley, до нее Потанины работали в Texas Instruments, National Semiconductor, Zilog, на Ангстреме, учились в МИФИ и МИЭТ-е.

К Потаниным примкнул специалист про флэш-памяти Александр Котов из компании Silicon Storage Technologies, которую несколько лет назад купил производитель микроконтроллеров Microchip Technology. «О, еще один русский микрочиповец!» — воскликнул я, ибо микрочиповцы мне хорошо знакомы, я даже делал доклад на их конференции в Санкт-Петербурге.

Поговорили про перевод учебника Харрис & Харрис на русский, который распостраняется бесплатно и про судьбы России.

И немного про актуальность аналогового дизайна — как вообще, так и для России в частности:

А вот еще один российский проект на DAC-е — спроектированная в России плата Black Swift на стенде Imagination Technologies. Сама плата маленькая черная, она стоит на большой демонстрационной:

Еще я встретил Фумико Сузуки, консультантку по японскому электронному рынку, которой опять же поделился про перевод учебника Харрис & Харрис на русский, который распостраняется бесплатно. Также я рассказал, что Х&Х был переведен и на японский и упомянул про критиков, которые уверяют, что россияне должны якобы читать такие учебники только на английском.

Реакция Фумико на вопрос, правильно ли переводить Харрис & Харрис: «Конечно, конечно. Когда вы читаете на своем языке, вы выучиваете больше. Когда вы привыкнете, вы можете читать и на английском, но в любом случае — отличная книга.»

Китаянка Манни Райт, инженерный менеджер приложений, тоже считает что тексты на сложные темы молодым студентам может быть лучше читать по китайски (Харрис & Харрис также переведен на китайский):

А вот мнение Линка Джепсона, рожденного в США американца, который из спортивного интереса выучил русский язык и прожил года полтора в Зеленограде жизнью российского инженера. Линк — инженер по верификации (SystemVerilog, UVM) чипа, который делает ray-tracing для генерации реалистичных трехмерных изображений:

По русски: «главное — делайте крутые чипы, что-то полезное [а язык — вторичен]»:

По английски про Harris & Harris:

Но Линка я, в отличие от всех перечисленных товарищей, встретил не на DAC-е, а на конференции под названием SVOD (Silicon Valley Open Doors), которая проходила одновременно с конференцией DAC, но не в Сан-Франциско, а в 60 километрах южнее, в Музее Истории Компьютеров в Маунтин-Вью. Как можно догадаться из названия («Свод»), это конференция, которая сводит русских стартапщиков и американских инвесторов.

Я зашел на SVOD, чтобы наугад отловить кого-нибудь, кто имеет отношение к российской электронике, и заодно поглазеть на деловых русских девушек, которые как правило тусуются на таких конференциях. Девушки отыскались сразу в лице Анны Дегтеревой, одной из организаторов UTGEM'14, украинской конференции хайтека, которую я описал в panchul.livejournal.com/390486.html.

Анна подтвердила мое наблюдение, что в этом году народу на Свод приехало гораздо больше, чем в прошлом году:

Довольно быстро нашлись и люди из российской электроники, в лице Александра Галицкого, человека со следующей биографией: МИЭТ, МФТИ, Зеленоград, ЭЛАС, бортовой компьютер космической станции «Салют», соглашение с Sun Microsystems, участие в основании НПО ЭЛВИС и компании ЭЛВИС-ПЛЮС, венчурный фонд Almaz Capital.

Я спросил мнение Александра Галицкого по следующим вопросам:

1. Почему кооперация между Imagination Technologies и группой компаний ЭЛВИС является значимой? Imagination Technologies больше всего известна как разработчик графического процессора PowerVR внутри Apple iPhone, а также лицензиат процессорных ядер архитектуры MIPS. Группа компаний ЭЛВИС известна как разработчик космической микроэлектроники и «умных камер», которые используются в частности для обеспечения безопасности аэропорта Шереметьево.

2. Как улучшить образование молодых российских инженеров в области микроэлектроники?

3. Как можно использовать российские фабрики Микрон и Ангстрем в Зеленограде?

4. Как вывести микросхемы, спроектированные в России, на мировой рынок?

Потом Александр Галицкий пошел на сцену выступать, а я выпил кофе и пошел домой писать этот пост:

Только зарегистрированные пользователи могут участвовать в опросе. Войдите, пожалуйста.

Комментарии (12)

andy_p

16.06.2015 18:45Мы разрабатывали библиотеку цифровых элементов для компьютера, которй делался в ЭЛАС. Кстати, система команд этого компьютера была подмножеством команд ЕС ЭВМ.

YuriPanchul Автор

16.06.2015 19:51Интересно. А вы с Ярославом Петричковичем (президентом ЭЛВИСа) знакомы?

zvic

17.06.2015 18:38В SILVACO работает несколько русских

Русских там довольно мало, а вот белорусов — достаточно.

nerudo

Всегда хотел задать вопрос создателям языка Verilog: почему после module() ставится ";", а после endmodule — нет?

Хотя с точки зрения здравого смысла module начинает конструкцию описания модуля, далее следует внутренняя часть и потом по завершении словом endmodule ее было бы поставить наиболее уместно.

DarkByte

Не зная синтаксиса verilog могу предложить, что если после ";" не обязательно ставить перенос строки, то символ служит разделителем, а если endmodule это последняя строка в файле, то после неё ничего уже не может быть и нет смысла в использовании разделителя. Например в pascal после end ставится ";", а после последнего end в файле ставится просто точка.

nerudo

После endmodule может идти новый module или еще какая хрень. Там везде так:

UA3MQJ

А в Veriog после end не ставится точка с запятой никогда. Видимо, эти слова сами по себе являются закрывающими.

AlexanderS

Предположу. В VHDL код можно поделить на три части: карта портов (port map(), после которого ставится ";"), объявление сигналов и компонентов (между «architecture Behavioral of ХХХ is» и «begin»), описание логики схемы (между «begin» и "«begin»"). В верилоге «module();» будет соответствовать карте портов в VHDL. Т.е. ";" в данном случае является концептуальным разделителем между картой портов и описанием схемы (сигналы же объявлять в verilog не обязательно все заранее — можно перед каждым процессом отдельно).

nerudo

Если module() считать отдельной законченной конструкцией, то все прочие части (описывающие логическую схему) остаются как бы висящими в воздухе, в то время как они обязательно должны следовать между module и endmodule.

Понятно, что можно притянуть разные доводы, но мне было бы интересно услышать именно оригинальную трактовку… Может Юрий, как наиболее близко сидящий от создателей верилога, сможет пролить свет…

AlexanderS

Ну да, это гадание)

YuriPanchul Автор

Я спрошу при случае — мне это тоже казалось странным в свое время.