Недавно мы занимались восстановлением бортового управляющего компьютера «Аполлона» – компьютера, занимавшегося управлением, навигацией и контролем на борту миссий «Аполлон», летавших к Луне. Этот исторический компьютер одним из первых начал использовать интегральные схемы (ИС), а его процессор был полностью построен на вентилях NOR (в памяти компьютера использовался второй тип ИС, усилитель считывания). В данной статье я опишу архитектуру и схему CPU.

Разделённые лотки управляющего компьютера «Аполлона». В левом лотке содержится логика на основе NOR-вентилей. В правом – память и вспомогательные компоненты.

Управляющий компьютер «Аполлона» (Apollo Guidance Computer, AGC) разработали в 1960-х для обеспечения полёта миссий «Аполлон» на Луну. В то время, когда большая часть компьютеров занимала объём от полноразмерного холодильника до целой комнаты, AGC был чем-то уникальным – он был достаточно маленьким, чтобы уместиться на борту космического корабля «Аполлон», весил 32 кг и занимал не более 0,03 м3 (30 литров).

Компьютер AGC – 15-битный. Странно встречать размер слова, не являющийся степенью двойки, но в 1960-х, ещё до того, как байты стали популярными, в компьютерах использовали разнообразные размеры слов. 15 бит обеспечивали достаточную точность для посадки на луну (и использовали данные с удвоенной и утроенной точностью при необходимости), поэтому 16 бит просто увеличили бы размер и вес компьютера без необходимости.

Инструкция AGC вмещалась в 15-битное слово, и состояла из 3 бит, обозначавших код операции, и 12 бит, обозначавших адрес в памяти. К сожалению, этих объёмов всё равно не хватало, поэтому в компьютере использовались многочисленные хитрости и обходные пути, и архитектура получилась довольно неуклюжей. 12-битный адрес памяти мог обращаться только к 4 К слов. При этом у AGC было 2К слов в основной RAM и 36К слов в памяти на сердечниках. Чтобы обращаться ко всей памяти, AGC использовал сложную систему переключения банков памяти и множество регистров. Иначе говоря, к памяти можно было обращаться только по кускам в 256 слов, а к ROM – по кускам несколько большего размера.

3 бит для кода операции не хватало, чтобы напрямую обозначить 34 возможные инструкции, поэтому AGC использовал трюки с расширением значения инструкций и с тем, что некоторые инструкции имело смысл исполнять только с определёнными ячейками памяти. Кроме того, использовались такие трюки, как «волшебные» адреса в памяти – к примеру, запись в ячейку «регистра сдвига вправо» осуществляла побитовый сдвиг, исключая таким образом необходимость в отдельной инструкции «сдвиг вправо». Были также инструкции, сочетающие несколько действий сразу.

Архитектура AGC была довольно простой, даже по стандартам 1960-х. Хотя его создавали в эпоху сложных и мощных мейнфреймов, возможности AGC были весьма ограничены; по мощности и архитектуре он сравним с ранними микропроцессорами. Его сильными сторонами были компактный размер и большие возможности по обеспечению ввода и вывода данных в реальном времени.

На архитектурной диаграмме ниже показаны основные компоненты AGC. Я выделил цветом те части, на которых остановлюсь подробнее. У AGC был небольшой набор регистров, и простой арифметический модуль, занимавшийся только сложением. У него была ROM всего на 36К слов и RAM на 2К слов. «Шина записи» была основным путём передачи данных между компонентами. Декодирование инструкций и генератор последовательностей выдавали управляющие импульсы для AGC.

Блок-схема AGC

Примерно половину диаграммы занимает память, что отражает тот факт, что во многих аспектах архитектуру AGC разрабатывали вокруг его памяти. Как большая часть компьютеров в 1960-х, AGC использовал память на сердечниках, храня каждый бит в крохотном ферритовом кольце (сердечнике), нанизанном на сетку проводов. Поскольку для каждого бита требовался отдельный физический сердечник, объём такой памяти был кардинально меньше, чем у современной полупроводниковой. Отличительным свойством памяти на сердечниках было то, что прочтение слова из памяти удаляло его, поэтому после каждого доступа это значение приходилось записывать заново. Также у AGC была фиксированная память ROM, знаменитые прошитые сердечники – они использовались для хранения программ, и были физически прошиты проводами (см. ниже).

Память на прошитых сердечниках крупным планом

AGC был одним из первых компьютеров, использовавших ИС. Возможности этих первых ИС были весьма ограниченными; на чипах AGC (ниже) находилось всего по шесть транзисторов и восемь резисторов, и вместе они реализовывали NOR-вентиль с тремя входами.

Двойной NOR-вентиль с тремя входами из AGC. Десять проводов снаружи кристалла соединены с внешними контактами ИС.

Ниже показано схематическое обозначение NOR-вентиля. Это простейший логический вентиль: если все входы равны нулю, то выход равен единице. Вас может удивить, но одних NOR-вентилей достаточно для создания компьютера. NOR – вентиль универсальный: на его основе можно сделать любой другой логический вентиль. К примеру, при объединении всех входов NOR мы получаем инвертер. Расположив на выходе NOR инвертер, мы получим OR-вентиль. Расположив инвертеры на входах NOR-вентиля, мы получим AND-вентиль. А из этих вентилей можно строить более сложную логику: триггеры, сумматоры и счётчики.

NAND-вентиль обладает той же универсальностью. В современных схемах по техническим причинам NAND используются чаще, чем NOR. В популярном курсе "От NAND до Тетриса" описано, как создать вычислительную машину из NAND-вентилей, вплоть до реализации игры «Тетрис». Сначала из NAND строится набор логических вентилей (NOT, AND, OR, XOR, мультиплексор, демультиплексор). Затем из них создаются более крупные строительные блоки (триггер, сумматор, счётчик, ALU, регистр), а уже из них – компьютер.

NOR-вентиль выдаёт 1, если на всех входах у него 0. Если хотя бы на одном из входов 1, то NOR выдаёт 0.

Очень часто в AGC попадается такой компонент, как RS-триггер (set-reset, установить/сбросить). Эта схема делается из двух NOR-вентилей и хранит один бит данных. На входе set хранится бит 1, а на входе reset – бит 0. То есть, импульс 1, поданный на вход set, выключает верхний вентиль и включает нижний, поэтому на выходе получается 1. Импульс 1, поданный на вход reset, делает всё наоборот. Если на оба входа подать 0, триггер запоминает своё предыдущее состояние, играя роль накопителя. В следующем разделе мы покажем, как из триггера делаются регистры.

RS-триггер из двух NOR-вентилей. Один вентиль при включении выключает другой. Черта над одним из выходов обозначает, что он дополняет другой.

У AGC есть небольшой набор регистров для временного хранения значений вне основной памяти. Основной регистр – накопитель (A), используемый во многих арифметических операциях. Также у него есть регистр счётчика Z, регистры арифметического блока X и Y, буфер B, адрес возврата Q и некоторые другие (в современных компьютерах для вызова подпрограмм и возврата из них используется стек, но в ту эпоху программистам для рекурсии необходимо было писать стек самим). Для доступа к памяти есть регистр адреса памяти S, а для данных — регистр буфера памяти G. Также у AGC есть регистры в основной памяти – к примеру, счётчики ввода/вывода.

На диаграмме ниже приведена схема регистров AGC, упрощённая для случая с одним битом и двумя регистрами. У каждого бита регистра есть триггер, использующий описанную ранее схему (синий и фиолетовый). Данные передаются в регистры и из них по шине записи (красный). Для записи в регистр триггер сбрасывается сигналом очистки (CQG или CZG, зелёный). Затем сигнал «запись» (WQG или WZG, оранжевый) позволяет данным, идущим по шине записи, установить соответствующий триггер регистра. Для чтения регистра сигнал «чтение» (RQG или RZG, голубой) проходит выход триггера через усилитель записи на шину записи, и используется в других частях AGC. Полная схема регистров более сложная, в ней есть несколько 16-битных регистров, но базовая схема такая.

Упрощённая схема работы регистров AGC

Диаграмма регистров иллюстрирует три ключевых момента. Во-первых, схема регистров строится из NOR-вентилей. Во-вторых, движение данных построено вокруг шины записи. Наконец, действия регистров зависят от определённых управляющих сигналов, приходящих в нужное время.

У большинства компьютеров есть арифметико-логическое устройство, выполняющее арифметические и булевские операции. По сравнению с современными компьютерами, арифметический модуль у AGC весьма ограничен: он выполняет только сложение 16-битных величин, поэтому называется арифметическим модулем, а не арифметико-логическим (остальные операции выполняются через различные трюки; к примеру, вычитание выполняется через сложение, перед которым у одного из аргументов биты обращаются на противоположные, и т.п.).

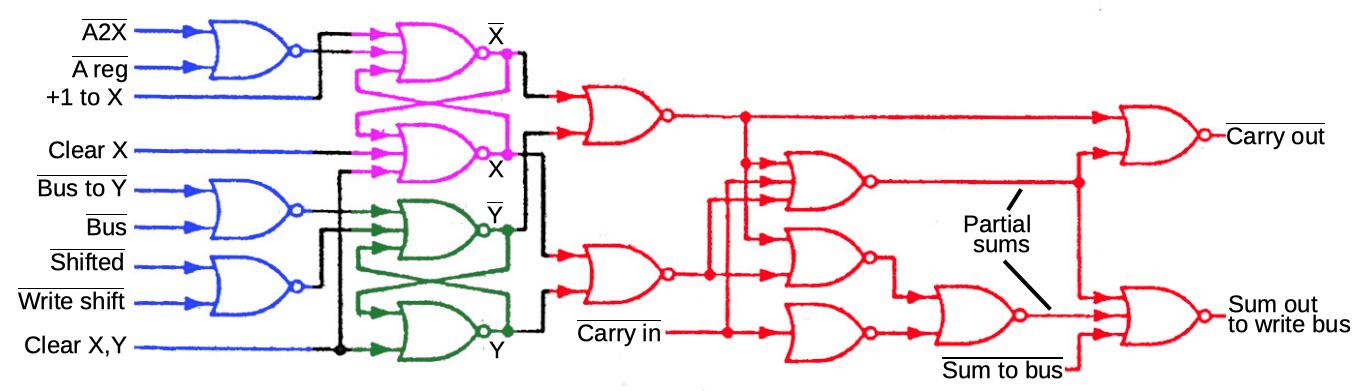

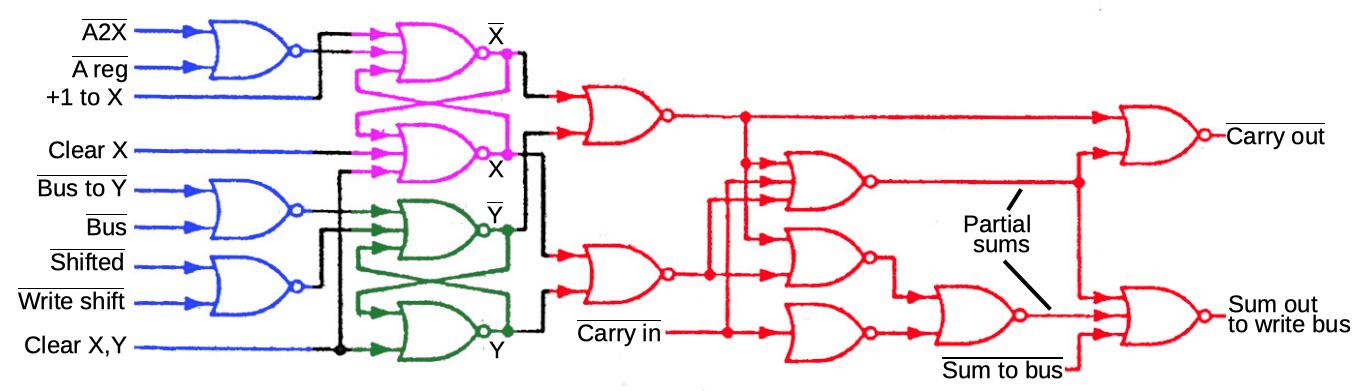

На схеме ниже показан один бит арифметического модуля AGC. Полный сумматор (красный) вычисляет сумму двух битов и перенос. Перенос передаётся в следующий сумматор – таким образом их можно комбинировать для сложения более длинных слов (чтобы ускорить передачу переноса в случаях типа 111111111111111 + 1, AGC использует сумматор с пропуском переноса).

Регистры X и Y (фиолетовый и зелёный) обеспечивают два входящих бита в сумматор. Они реализованы при помощи уже описанных триггеров на NOR-вентилях. Синий контур записывает значения в регистры X и Y в соответствии с управляющими сигналами. Схема довольно сложна, ведь она позволяет хранить в регистрах константы и значения со сдвигом, но я не буду углубляться в эту тему. Обратите внимание на управляющий сигнал A2X, передающий значение регистра A в регистр X; мы вернёмся к нему позже.

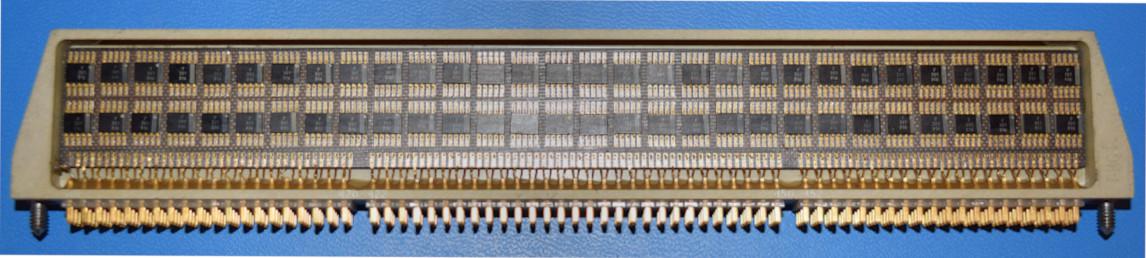

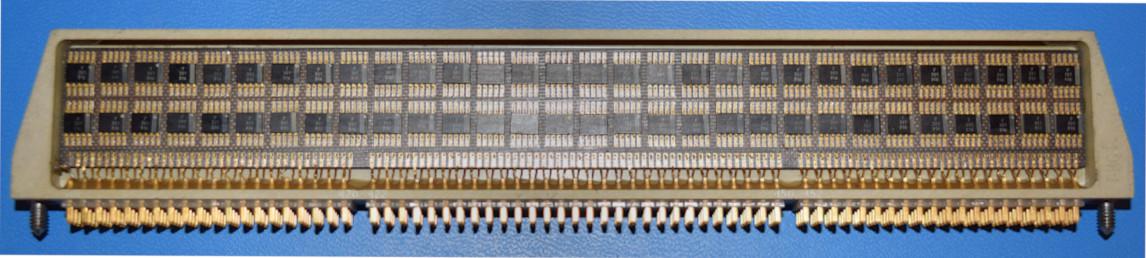

На фото ниже показана физическая реализация схемы AGC. Этот модуль реализует четыре бита для регистров и арифметический модуль. Чёрные прямоугольники – это плоские ИС; в каждом модуле есть две платы по 60 чипов, и всего получается 240 NOR-вентилей. Арифметический модуль и регистры собраны из четырёх идентичных модулей, каждый из которых обрабатывает по четыре бита; это похоже на работу микропроцессорной секции.

Арифметический модуль и регистры собраны из четырёх идентичных модулей. Модули установлены в слоты от A8 до A11.

В данном разделе описывается последовательность операций, которые проделывает AGC для выполнения инструкции. В частности, я покажу, как работает инструкция сложения ADS (add to storage). Эта инструкция читает значение из памяти, прибавляет его к накопителю (регистр А), и сохраняет сумму как в сумматоре, так и в памяти. Это единичная инструкция, но для её выполнения AGC проделывает несколько шагов и много значений перемещаются туда и сюда.

Таймер инструкций реализуется за счёт подсистемы памяти на магнитных сердечниках. В частности, чтение значения из памяти стирает хранимое значение, поэтому после каждого чтения значение необходимо записать обратно. Также при доступе к памяти существует задержка между обозначением адреса и поступлением данных. В итоге каждый такт памяти тратит по 12 шагов на чтение и на последующую запись. Каждый интервал времени (от T1 до T12) длится чуть менее микросекунды, а весь такт длится 11,7 мкс, и называется временем такта памяти (MCT).

Модуль стираемой памяти на магнитных сердечниках от AGC. Хранит 2 килослова, каждый бит хранится при помощи отдельного крохотного ферритового колечка.

MCT является базовой единицей памяти для исполнения инструкций. Типичной инструкции требуется два такта памяти: один для извлечения инструкции из памяти, второй для выполнения операции. Поэтому на типичную инструкцию уходит два MCT (23,4 мкс), что даёт нам 43 000 инструкции в секунду (по сравнению с современными процессорами и их миллиардами инструкций в секунду это чрезвычайно медленно).

AGC обрабатывает инструкции, разбивая их на подкоманды, каждая из которых отнимает один такт памяти. К примеру, инструкция ADS состоит из двух подкоманд: ADS0 (сложение) и STD2 (вызов следующей инструкции). На диаграмме ниже показано движение данных внутри AGC для выполнения инструкции ADS0. 12 тактов идут слева направо.

Важнейшие шаги следующие:

T1: адрес операнда копируется из регистра инструкции B в регистр адреса памяти S, чтобы начать чтение из памяти.

T4: Операнд читается из памяти в регистр данных памяти G.

T5: Операнд копируется из G в сумматор Y. Значение накопителя A копируется в сумматор X.

T6: Сумматор вычисляет сумму U, и копирует её в регистр данных памяти G.

T8: Счётчик программы Z копируется в регистр адреса памяти S для подготовки к получению следующей инструкции из памяти.

T10: Сумма из регистра данных памяти G записывается обратно в память.

T11: Сумма U копируется в накопитель А.

Хотя это простая инструкция суммирования, в течение 12 временных интервалов туда и сюда передаётся множество данных. И с каждым из этих действий связан определённый управляющий сигнал; к примеру, сигнал A2X на интервале T5 копирует значение из накопителя А в регистр Х. Для копирования регистра G в регистр Y требуется два управляющих импульса: RG (прочесть G) и WY (записать Y). В следующем разделе я объясню, как управляющий модуль AGC генерирует нужные управляющие сигналы для каждой инструкции.

Как у большинства компьютеров, управляющий модуль AGC декодирует каждую инструкцию и генерирует управляющие сигналы, сообщающие остальной части процессора, что ему нужно делать. Для генерации сигналов AGC использует заранее запрограммированный управляющий модуль, состоящий из NOR-вентилей. AGC не использует микрокод; у него нет микроинструкций и управляющей памяти, поскольку это заняло бы слишком много физического места.

Сердце управляющего модуля AGC называется генератором пересечений [crosspoint generator]. Он берёт подкоманду и один из временных отрезков и генерирует управляющие сигналы для этой комбинации. Его можно представить себе в виде решётки, на которой в одном направлении идут подкоманды, а в другом – временные отрезки, и каждой из точек пересечения назначен свой управляющий сигнал.

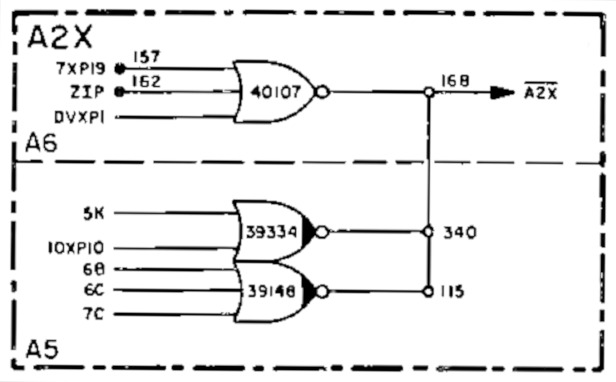

Генератор пересечений требует множества компонентов и разделён на три модуля; это модуль А6. Обратите внимание на добавленные провода, изменяющие схему. Это ранняя версия модуля для тестирования на земле; у полётных модулей уже никаких проводов не было.

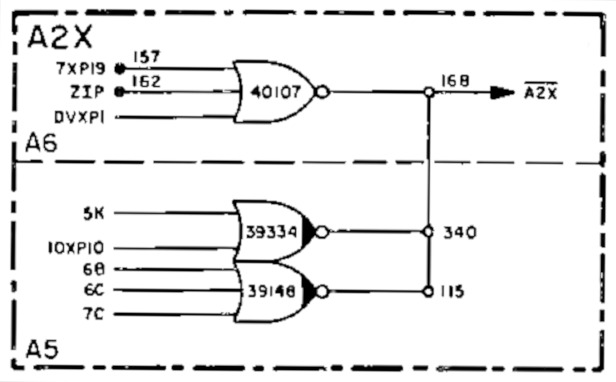

Для эффективности итоговый управляющий модуль крайне оптимизирован. Инструкции со схожим поведением скомбинированы и обрабатываются генератором пересечений совместно, что уменьшает размер необходимой схемы. К примеру, у AGC есть инструкция «добавление к накопителю с двойной точностью» (DAS). Поскольку она примерно эквивалентна двум сложениям одинарных слов, у подкоманд DAS1 и ADS0 в генераторе пересечений общая логика. На схеме ниже показана схема генератора пересечений для временного отрезка Т5, и выделена логика подкоманды ADS0 (использующая сигнал DAS1). К примеру, сигнал 5К генерируется из комбинации DAS1 и Т5.

Но что собой представляют сигналы 5К и 5L? Это ещё одна оптимизация. Многие управляющие импульсы часто подаются вместе, поэтому вместо того, чтобы генерировать их напрямую, генератор пересечений генерирует промежуточные сигналы для пересечений. К примеру, 5K генерирует управляющие импульсы A2X и RG, а 5L генерирует управляющий импульс WY. На диаграмме ниже показано, как генерируется сигнал A2X: любой из 8 различных сигналов (включая 5K) генерирует A2X. Похожие схемы генерируют другие управляющие сигналы. Эти оптимизации позволили уменьшить размер генератора пересечений, но он всё равно остался крупным, и разросся на целых три модуля.

Подытоживая, можно сказать, что управляющий модуль отвечает за то, что сообщает CPU, что ему делать для выполнения инструкции. Сначала инструкции разбиваются на подкоманды. Генератор пересечений создаёт нужные управляющие импульсы для каждого временного интервала и подкоманды, сообщая регистрам, арифметическому модулю и памяти, что им нужно делать.

Обычно инструкции состояли из двух подкоманд, но были и исключения. Некоторые из инструкций, например, умножение или деление, требовали использования множества подкоманд, поскольку состояли из многих шагов. И наоборот, инструкция перехода по адресу TC использовала одну подкоманду, поскольку ей нужно было только вызвать следующую инструкцию.

Другие процессоры использовали другие подходы к генерации управляющих сигналов. 6502 и многие другие ранние микропроцессоры декодировали инструкции при помощи программируемой логической матрицы (PLA), реализующей логику AND/OR через память только для чтения.

Микропроцессор 6502.

Это была захватывающая экскурсия по бортовому управляющему компьютеру «Аполлона». Чтобы сильно не растягивать её, я сконцентрировался на инструкции сложения ADS и некоторых управляющих импульсах (A2X, RG и WY). Надеюсь, вы получили представление о том, как можно собрать компьютер из таких примитивных элементов, как NOR-вентили.

Самая наглядная часть архитектуры – тракт данных: арифметический модуль, регистры и шина данных. Регистры AGC созданы на основе простых триггеров из NOR-вентилей. И хотя арифметический модуль AGC умеет делать только сложение, компьютер всё равно справляется со всем набором операций, включая умножение, деление и булевские операции.

Однако тракт данных – это лишь часть компьютера. Среди других критически важных компонентов есть управляющий модуль, сообщающий компонентам, что им нужно делать. Подход, используемый в AGC, основан на генераторе пересечений, использующем сильно оптимизированную и жёстко прописанную логику для генерации правильных управляющих импульсов для определённых подкоманд и временных интервалов.

Используя эти возможности, AGC обеспечивал руководство, навигацию и управление на борту миссий «Аполло», и сделал возможным посадки на Луну. Также он подстегнул раннюю индустрию интегральных схем, использовав 60% выпускавшихся в США ИС в 1963. Поэтому современные компьютеры многим обязаны AGC и его простым NOR-компонентам.

AGC работает в лаборатории, подключённый к винтажному осциллографу Tektronix

Архитектура управляющего компьютера «Аполлона»

Разделённые лотки управляющего компьютера «Аполлона». В левом лотке содержится логика на основе NOR-вентилей. В правом – память и вспомогательные компоненты.

Управляющий компьютер «Аполлона» (Apollo Guidance Computer, AGC) разработали в 1960-х для обеспечения полёта миссий «Аполлон» на Луну. В то время, когда большая часть компьютеров занимала объём от полноразмерного холодильника до целой комнаты, AGC был чем-то уникальным – он был достаточно маленьким, чтобы уместиться на борту космического корабля «Аполлон», весил 32 кг и занимал не более 0,03 м3 (30 литров).

Компьютер AGC – 15-битный. Странно встречать размер слова, не являющийся степенью двойки, но в 1960-х, ещё до того, как байты стали популярными, в компьютерах использовали разнообразные размеры слов. 15 бит обеспечивали достаточную точность для посадки на луну (и использовали данные с удвоенной и утроенной точностью при необходимости), поэтому 16 бит просто увеличили бы размер и вес компьютера без необходимости.

Инструкция AGC вмещалась в 15-битное слово, и состояла из 3 бит, обозначавших код операции, и 12 бит, обозначавших адрес в памяти. К сожалению, этих объёмов всё равно не хватало, поэтому в компьютере использовались многочисленные хитрости и обходные пути, и архитектура получилась довольно неуклюжей. 12-битный адрес памяти мог обращаться только к 4 К слов. При этом у AGC было 2К слов в основной RAM и 36К слов в памяти на сердечниках. Чтобы обращаться ко всей памяти, AGC использовал сложную систему переключения банков памяти и множество регистров. Иначе говоря, к памяти можно было обращаться только по кускам в 256 слов, а к ROM – по кускам несколько большего размера.

3 бит для кода операции не хватало, чтобы напрямую обозначить 34 возможные инструкции, поэтому AGC использовал трюки с расширением значения инструкций и с тем, что некоторые инструкции имело смысл исполнять только с определёнными ячейками памяти. Кроме того, использовались такие трюки, как «волшебные» адреса в памяти – к примеру, запись в ячейку «регистра сдвига вправо» осуществляла побитовый сдвиг, исключая таким образом необходимость в отдельной инструкции «сдвиг вправо». Были также инструкции, сочетающие несколько действий сразу.

Архитектура AGC была довольно простой, даже по стандартам 1960-х. Хотя его создавали в эпоху сложных и мощных мейнфреймов, возможности AGC были весьма ограничены; по мощности и архитектуре он сравним с ранними микропроцессорами. Его сильными сторонами были компактный размер и большие возможности по обеспечению ввода и вывода данных в реальном времени.

На архитектурной диаграмме ниже показаны основные компоненты AGC. Я выделил цветом те части, на которых остановлюсь подробнее. У AGC был небольшой набор регистров, и простой арифметический модуль, занимавшийся только сложением. У него была ROM всего на 36К слов и RAM на 2К слов. «Шина записи» была основным путём передачи данных между компонентами. Декодирование инструкций и генератор последовательностей выдавали управляющие импульсы для AGC.

Блок-схема AGC

Примерно половину диаграммы занимает память, что отражает тот факт, что во многих аспектах архитектуру AGC разрабатывали вокруг его памяти. Как большая часть компьютеров в 1960-х, AGC использовал память на сердечниках, храня каждый бит в крохотном ферритовом кольце (сердечнике), нанизанном на сетку проводов. Поскольку для каждого бита требовался отдельный физический сердечник, объём такой памяти был кардинально меньше, чем у современной полупроводниковой. Отличительным свойством памяти на сердечниках было то, что прочтение слова из памяти удаляло его, поэтому после каждого доступа это значение приходилось записывать заново. Также у AGC была фиксированная память ROM, знаменитые прошитые сердечники – они использовались для хранения программ, и были физически прошиты проводами (см. ниже).

Память на прошитых сердечниках крупным планом

NOR-вентили

AGC был одним из первых компьютеров, использовавших ИС. Возможности этих первых ИС были весьма ограниченными; на чипах AGC (ниже) находилось всего по шесть транзисторов и восемь резисторов, и вместе они реализовывали NOR-вентиль с тремя входами.

Двойной NOR-вентиль с тремя входами из AGC. Десять проводов снаружи кристалла соединены с внешними контактами ИС.

Ниже показано схематическое обозначение NOR-вентиля. Это простейший логический вентиль: если все входы равны нулю, то выход равен единице. Вас может удивить, но одних NOR-вентилей достаточно для создания компьютера. NOR – вентиль универсальный: на его основе можно сделать любой другой логический вентиль. К примеру, при объединении всех входов NOR мы получаем инвертер. Расположив на выходе NOR инвертер, мы получим OR-вентиль. Расположив инвертеры на входах NOR-вентиля, мы получим AND-вентиль. А из этих вентилей можно строить более сложную логику: триггеры, сумматоры и счётчики.

NAND-вентиль обладает той же универсальностью. В современных схемах по техническим причинам NAND используются чаще, чем NOR. В популярном курсе "От NAND до Тетриса" описано, как создать вычислительную машину из NAND-вентилей, вплоть до реализации игры «Тетрис». Сначала из NAND строится набор логических вентилей (NOT, AND, OR, XOR, мультиплексор, демультиплексор). Затем из них создаются более крупные строительные блоки (триггер, сумматор, счётчик, ALU, регистр), а уже из них – компьютер.

NOR-вентиль выдаёт 1, если на всех входах у него 0. Если хотя бы на одном из входов 1, то NOR выдаёт 0.

Очень часто в AGC попадается такой компонент, как RS-триггер (set-reset, установить/сбросить). Эта схема делается из двух NOR-вентилей и хранит один бит данных. На входе set хранится бит 1, а на входе reset – бит 0. То есть, импульс 1, поданный на вход set, выключает верхний вентиль и включает нижний, поэтому на выходе получается 1. Импульс 1, поданный на вход reset, делает всё наоборот. Если на оба входа подать 0, триггер запоминает своё предыдущее состояние, играя роль накопителя. В следующем разделе мы покажем, как из триггера делаются регистры.

RS-триггер из двух NOR-вентилей. Один вентиль при включении выключает другой. Черта над одним из выходов обозначает, что он дополняет другой.

Регистры

У AGC есть небольшой набор регистров для временного хранения значений вне основной памяти. Основной регистр – накопитель (A), используемый во многих арифметических операциях. Также у него есть регистр счётчика Z, регистры арифметического блока X и Y, буфер B, адрес возврата Q и некоторые другие (в современных компьютерах для вызова подпрограмм и возврата из них используется стек, но в ту эпоху программистам для рекурсии необходимо было писать стек самим). Для доступа к памяти есть регистр адреса памяти S, а для данных — регистр буфера памяти G. Также у AGC есть регистры в основной памяти – к примеру, счётчики ввода/вывода.

На диаграмме ниже приведена схема регистров AGC, упрощённая для случая с одним битом и двумя регистрами. У каждого бита регистра есть триггер, использующий описанную ранее схему (синий и фиолетовый). Данные передаются в регистры и из них по шине записи (красный). Для записи в регистр триггер сбрасывается сигналом очистки (CQG или CZG, зелёный). Затем сигнал «запись» (WQG или WZG, оранжевый) позволяет данным, идущим по шине записи, установить соответствующий триггер регистра. Для чтения регистра сигнал «чтение» (RQG или RZG, голубой) проходит выход триггера через усилитель записи на шину записи, и используется в других частях AGC. Полная схема регистров более сложная, в ней есть несколько 16-битных регистров, но базовая схема такая.

Упрощённая схема работы регистров AGC

Диаграмма регистров иллюстрирует три ключевых момента. Во-первых, схема регистров строится из NOR-вентилей. Во-вторых, движение данных построено вокруг шины записи. Наконец, действия регистров зависят от определённых управляющих сигналов, приходящих в нужное время.

Арифметический модуль

У большинства компьютеров есть арифметико-логическое устройство, выполняющее арифметические и булевские операции. По сравнению с современными компьютерами, арифметический модуль у AGC весьма ограничен: он выполняет только сложение 16-битных величин, поэтому называется арифметическим модулем, а не арифметико-логическим (остальные операции выполняются через различные трюки; к примеру, вычитание выполняется через сложение, перед которым у одного из аргументов биты обращаются на противоположные, и т.п.).

На схеме ниже показан один бит арифметического модуля AGC. Полный сумматор (красный) вычисляет сумму двух битов и перенос. Перенос передаётся в следующий сумматор – таким образом их можно комбинировать для сложения более длинных слов (чтобы ускорить передачу переноса в случаях типа 111111111111111 + 1, AGC использует сумматор с пропуском переноса).

Регистры X и Y (фиолетовый и зелёный) обеспечивают два входящих бита в сумматор. Они реализованы при помощи уже описанных триггеров на NOR-вентилях. Синий контур записывает значения в регистры X и Y в соответствии с управляющими сигналами. Схема довольно сложна, ведь она позволяет хранить в регистрах константы и значения со сдвигом, но я не буду углубляться в эту тему. Обратите внимание на управляющий сигнал A2X, передающий значение регистра A в регистр X; мы вернёмся к нему позже.

На фото ниже показана физическая реализация схемы AGC. Этот модуль реализует четыре бита для регистров и арифметический модуль. Чёрные прямоугольники – это плоские ИС; в каждом модуле есть две платы по 60 чипов, и всего получается 240 NOR-вентилей. Арифметический модуль и регистры собраны из четырёх идентичных модулей, каждый из которых обрабатывает по четыре бита; это похоже на работу микропроцессорной секции.

Арифметический модуль и регистры собраны из четырёх идентичных модулей. Модули установлены в слоты от A8 до A11.

Выполнение инструкции

В данном разделе описывается последовательность операций, которые проделывает AGC для выполнения инструкции. В частности, я покажу, как работает инструкция сложения ADS (add to storage). Эта инструкция читает значение из памяти, прибавляет его к накопителю (регистр А), и сохраняет сумму как в сумматоре, так и в памяти. Это единичная инструкция, но для её выполнения AGC проделывает несколько шагов и много значений перемещаются туда и сюда.

Таймер инструкций реализуется за счёт подсистемы памяти на магнитных сердечниках. В частности, чтение значения из памяти стирает хранимое значение, поэтому после каждого чтения значение необходимо записать обратно. Также при доступе к памяти существует задержка между обозначением адреса и поступлением данных. В итоге каждый такт памяти тратит по 12 шагов на чтение и на последующую запись. Каждый интервал времени (от T1 до T12) длится чуть менее микросекунды, а весь такт длится 11,7 мкс, и называется временем такта памяти (MCT).

Модуль стираемой памяти на магнитных сердечниках от AGC. Хранит 2 килослова, каждый бит хранится при помощи отдельного крохотного ферритового колечка.

MCT является базовой единицей памяти для исполнения инструкций. Типичной инструкции требуется два такта памяти: один для извлечения инструкции из памяти, второй для выполнения операции. Поэтому на типичную инструкцию уходит два MCT (23,4 мкс), что даёт нам 43 000 инструкции в секунду (по сравнению с современными процессорами и их миллиардами инструкций в секунду это чрезвычайно медленно).

AGC обрабатывает инструкции, разбивая их на подкоманды, каждая из которых отнимает один такт памяти. К примеру, инструкция ADS состоит из двух подкоманд: ADS0 (сложение) и STD2 (вызов следующей инструкции). На диаграмме ниже показано движение данных внутри AGC для выполнения инструкции ADS0. 12 тактов идут слева направо.

Важнейшие шаги следующие:

T1: адрес операнда копируется из регистра инструкции B в регистр адреса памяти S, чтобы начать чтение из памяти.

T4: Операнд читается из памяти в регистр данных памяти G.

T5: Операнд копируется из G в сумматор Y. Значение накопителя A копируется в сумматор X.

T6: Сумматор вычисляет сумму U, и копирует её в регистр данных памяти G.

T8: Счётчик программы Z копируется в регистр адреса памяти S для подготовки к получению следующей инструкции из памяти.

T10: Сумма из регистра данных памяти G записывается обратно в память.

T11: Сумма U копируется в накопитель А.

Хотя это простая инструкция суммирования, в течение 12 временных интервалов туда и сюда передаётся множество данных. И с каждым из этих действий связан определённый управляющий сигнал; к примеру, сигнал A2X на интервале T5 копирует значение из накопителя А в регистр Х. Для копирования регистра G в регистр Y требуется два управляющих импульса: RG (прочесть G) и WY (записать Y). В следующем разделе я объясню, как управляющий модуль AGC генерирует нужные управляющие сигналы для каждой инструкции.

Управляющий модуль

Как у большинства компьютеров, управляющий модуль AGC декодирует каждую инструкцию и генерирует управляющие сигналы, сообщающие остальной части процессора, что ему нужно делать. Для генерации сигналов AGC использует заранее запрограммированный управляющий модуль, состоящий из NOR-вентилей. AGC не использует микрокод; у него нет микроинструкций и управляющей памяти, поскольку это заняло бы слишком много физического места.

Сердце управляющего модуля AGC называется генератором пересечений [crosspoint generator]. Он берёт подкоманду и один из временных отрезков и генерирует управляющие сигналы для этой комбинации. Его можно представить себе в виде решётки, на которой в одном направлении идут подкоманды, а в другом – временные отрезки, и каждой из точек пересечения назначен свой управляющий сигнал.

Генератор пересечений требует множества компонентов и разделён на три модуля; это модуль А6. Обратите внимание на добавленные провода, изменяющие схему. Это ранняя версия модуля для тестирования на земле; у полётных модулей уже никаких проводов не было.

Для эффективности итоговый управляющий модуль крайне оптимизирован. Инструкции со схожим поведением скомбинированы и обрабатываются генератором пересечений совместно, что уменьшает размер необходимой схемы. К примеру, у AGC есть инструкция «добавление к накопителю с двойной точностью» (DAS). Поскольку она примерно эквивалентна двум сложениям одинарных слов, у подкоманд DAS1 и ADS0 в генераторе пересечений общая логика. На схеме ниже показана схема генератора пересечений для временного отрезка Т5, и выделена логика подкоманды ADS0 (использующая сигнал DAS1). К примеру, сигнал 5К генерируется из комбинации DAS1 и Т5.

Но что собой представляют сигналы 5К и 5L? Это ещё одна оптимизация. Многие управляющие импульсы часто подаются вместе, поэтому вместо того, чтобы генерировать их напрямую, генератор пересечений генерирует промежуточные сигналы для пересечений. К примеру, 5K генерирует управляющие импульсы A2X и RG, а 5L генерирует управляющий импульс WY. На диаграмме ниже показано, как генерируется сигнал A2X: любой из 8 различных сигналов (включая 5K) генерирует A2X. Похожие схемы генерируют другие управляющие сигналы. Эти оптимизации позволили уменьшить размер генератора пересечений, но он всё равно остался крупным, и разросся на целых три модуля.

Подытоживая, можно сказать, что управляющий модуль отвечает за то, что сообщает CPU, что ему делать для выполнения инструкции. Сначала инструкции разбиваются на подкоманды. Генератор пересечений создаёт нужные управляющие импульсы для каждого временного интервала и подкоманды, сообщая регистрам, арифметическому модулю и памяти, что им нужно делать.

Обычно инструкции состояли из двух подкоманд, но были и исключения. Некоторые из инструкций, например, умножение или деление, требовали использования множества подкоманд, поскольку состояли из многих шагов. И наоборот, инструкция перехода по адресу TC использовала одну подкоманду, поскольку ей нужно было только вызвать следующую инструкцию.

Другие процессоры использовали другие подходы к генерации управляющих сигналов. 6502 и многие другие ранние микропроцессоры декодировали инструкции при помощи программируемой логической матрицы (PLA), реализующей логику AND/OR через память только для чтения.

Микропроцессор 6502.

Заключение

Это была захватывающая экскурсия по бортовому управляющему компьютеру «Аполлона». Чтобы сильно не растягивать её, я сконцентрировался на инструкции сложения ADS и некоторых управляющих импульсах (A2X, RG и WY). Надеюсь, вы получили представление о том, как можно собрать компьютер из таких примитивных элементов, как NOR-вентили.

Самая наглядная часть архитектуры – тракт данных: арифметический модуль, регистры и шина данных. Регистры AGC созданы на основе простых триггеров из NOR-вентилей. И хотя арифметический модуль AGC умеет делать только сложение, компьютер всё равно справляется со всем набором операций, включая умножение, деление и булевские операции.

Однако тракт данных – это лишь часть компьютера. Среди других критически важных компонентов есть управляющий модуль, сообщающий компонентам, что им нужно делать. Подход, используемый в AGC, основан на генераторе пересечений, использующем сильно оптимизированную и жёстко прописанную логику для генерации правильных управляющих импульсов для определённых подкоманд и временных интервалов.

Используя эти возможности, AGC обеспечивал руководство, навигацию и управление на борту миссий «Аполло», и сделал возможным посадки на Луну. Также он подстегнул раннюю индустрию интегральных схем, использовав 60% выпускавшихся в США ИС в 1963. Поэтому современные компьютеры многим обязаны AGC и его простым NOR-компонентам.

AGC работает в лаборатории, подключённый к винтажному осциллографу Tektronix

Lazytech

Оригинал:

www.multitran.com/m.exe?s=nor+gate&l1=2&l2=1

Пример употребления:

Цифровая электроника для начинающих — Кириченко П. — Google Books

www.multitran.com/m.exe?s=cpu&l1=1&l2=2

amartology

«вентиль NOR» — вполне понятный и общепринятый жаргонизм, «логический элемент ИЛИ-НЕ» ничем не лучше, зато намного длиннее. Что такое «NOR», вполне понятно любому человеку, который хотя бы немного в теме.

Lazytech

P.S. Справедливости ради привожу найденный пример использования жаргонизма «NOR-вентиль», который почему-то неважно гуглится:

Minecraft. Полное и исчерпывающее руководство — Стивен О'Брайен — Google Books

Но сам я впервые встретил этот английский термин в обсуждаемой статье, тогда как русский эквивалент знаю достаточно давно.

P.P.S. Забавно, что переводчик книги (см. ссылку выше) оставил как есть термины AND, OR, NOR и иже с ними, но при этом в переводе есть слово «ИСТИНА» (вместо более короткого и понятного любому программисту слова TRUE).

amartology

Или вот русский перевод учебника Харриса и Харрис: в нем в тексте везде использованы ИЛИ-НЕ, но в самом начале в определениях есть NOR gate. И в оригинале учебника употребляется, разумеется, тоже NOR gate.

Что касается того, что жаргонизм плохо гуглится в книгах, то на то он и жаргонизм, разве нет? )

Lazytech

Будем считать, что статья предназначена для специалистов по микроэлектронике и прочей-разной схемотехнике. Я, к сожалению, таковым не являюсь.

amartology

Мне казалось, что программистам должны давать в университете базовые основы дискретной математики. Но я могу быть неправ.

Lazytech

amartology

Lazytech

Ваше мнение мне понятно. Предлагаю на этом завязать со спором.

Перевод:

firegurafiku

К слову, конкретно этот перевод — всё же любительский и не совсем официальный, я бы не стал ссылаться на него в вопросах правильности употребления терминологии.

amartology

Конкретно этот перевод сделан людьми, работающими в индустрии, так что как раз с точки зрения употребления терминологии к нему гораздо больше доверия, чем в трудам профессиональных переводчиков, не имеющих отношения к тематике книги.

lingvo

У меня вот есть общий вопрос к таким статьям:

Я, конечно, понимаю, что "Аполлоны" и все, что с ними связано, это супер-интересно и важно для истории. Но зачем уделять столько времени составлению и переписыванию статей, которые нужны только для восхищения умом и сообразительностью? Расписанная архитектура была крутой для своего времени, но сегодня уже никому не нужна даже для общего развития.

То есть в принципе это то же самое, что продолжать выпускать статьи об устройстве автомобиля ВАЗ 2101, а также об особенностях его карбюратора и системы зажигания. И то, для этих ВАЗ 2101 это еще имеет смысл, так как существуют ездящие экземпляры и данная информация может быть кому-то полезна. Но Аполлоны-то не летают.

Может я не прав — ну напишите в ответ коммент, что полезного вы выносите из изучения архитектур старых компьютеров.

VMichael

Т.е. по вашему все должны как биороботы руководствоваться не «нравится», «не нравится», а исключительно некоей «пользой», причем исключительно в вашем понимании?

Какую пользу получают люди, когда коллекционируют марки? Или когда смотрят сериалы?

Или когда посещают музеи старой техники? Любуются закатом?

И, кстати, когда изучаешь прошлые технические решения, может посетить мысль, как можно решить текущую задачу или просто потренируется мышление. Что в целом полезно.

P/S: У меня вот вопрос к таким комментариям: Зачем вообще их писать и тратить на это время? Есть варианты: — поставить минус статье; — проигнорировать статью. Но нет, нужно выплеснуть негодование о том, что не укладывается в ваше видение «пользы». Хотя наверное, это потому, что сложно заминусить до полного молчания автора с высоким рейтингом.

lingvo

Наверное, именно поэтому. Будь бы кто другой, я бы прошел мимо, поставил минусик статье да и все. Но тут нагорело. Я ведь сам фанат техники — "Буран" и "Шаттл" все обглядел в музеях. Да, круто, да, интересно. ПЗУ на проводах — шикарно!

Но зачем об этом писать по десять статей в год? Красивость, любование — они как раз, как в музее — прочитал один раз, удивился, восхитился и пошел дальше. Как и в музеи мы ходим не каждый день. Но когда тебя начинают водить на экскурсии к одному и тому же экспонату и рассказывать — смотри, как это устроено — тут уж невольно задумаешься о "пользе" такого времяпровождения.

old_gamer

Некоторым людям это интересно, они читают. В принципе, тут наглядна оценка статьи: много плюсов = много пользователей хотели бы видеть такие статьи впредь.

А так, статья — развлекательного характера. В целом, статьи в хабе «Старое железо» довольно много плюсов набирают, то есть тематика аудитории нравится.

Nalivai

Не нравится — не пишите, мы-то тут причем?

Oxyd

Не нравится — не читайте.

Nalivai

И я о том

AndyKorg

Большинству населения не по карману ехать в Москву (а тем более в США) и посетить музей старой техники, а так хоть что-то более подробно чем «уникальные технические решения». И да: «Повторение — мать учения»

drWhy

Ну и Винтаж, да: В части второй — как раз подходит. Представьте, сколько человеко-лет труда вложено в создание и тестирование описанного компьютера. Одна прошитая память чего стоит.

Goyza

Вы вообще в музеи ходите?

… в данном случае персонально для меня интересна реализация известных структур в рамках ограниченной технологической базы. Специально этим вопросом заниматься желания нет, а вот в формате такой статьи — самое то…

amartology

Как решать задачи в условиях серьезных ограничений в ресурсах. Это довольно часто бывает очень полезно и освежающе.

lingvo

Вспомнился анекдот на эту тему:

Это с точки зрения того, что необходимо сначала себе создать такие ограничения в ресурсах, чтобы появилась потребность изобретения собственной архитектуры, как это было в Аполлонах

old_gamer

В хобби-проектах такое сплошь и рядом

amartology

И это все вполне себе нормальные профессиональные задачи, а не хоббийные. Так что вы очень зря недооцениваете понимание того, как работают низкоуровневые вещи и возможность переиспользовать опыт давно минувших дней.

atomlib

А зачем мне оправдываться? Я редко объясняю собственные предпочтения.

Вы намеренно пришли в статью, в которой смакуют потроха проекта пятидесятилетней давности. Насильно никто никого не заставляет читать.

Вообще-то в комплекте с каждым «ВАЗ-2101» шёл прекрасный цветной альбом с внутренним устройством автомобиля, рассказывающий про все основные узлы и детали.

Если кому-то захочется документировать эту тему ради собственного удовольствия, лично я ему слова не скажу. Пускай занимается в свободное время подобным.

Brak0del

Мне в своё время интересно было почитать про устройство всяких Alpha, Power и Pentium-ов, про причины тех или иных проектных решений. А многие идеи потом пригодились при разработке под ПЛИС.

neonkainside

Изучение таких девайсов, созданных на самом острие тогдашнего прогресса, позволяет понять, как думают люди, решающие такие задачи. Технологии ушли вперед, а задачи не поменялись, нужно из имеющихся блоков собрать нечто с предельными характеристиками. Зачем учить историю древнего мира? Давайте читать только текущие новости!

claymen

Мне такое очень нравится, это не тупой фреймворк где фиг его знает как что происходит. Интересно и с точки зрения развлечения и очень много умных мыслей. Например какая красота волшебные ячейки. Эти приемы актуальны всегда, мы как то раз Повысили быстродействие системы заменив расчетную функцию на табличное значение, а это я вычитал у разработчиков демок. Они синус не вычисляли, а брали таблично и далее формулами приведения.

vp1000

С удовольствием прочитал статью. Как и предыдущую, про память на прошитых сердечниках. Для своего времени шедевры инженерной мысли. Вместить в то время компьютер в такой ограниченный вес и объем сложнейшая задача. Интересно читать, как разработчики выкручивались в таких стесненных условиях.

Компьютеры размером с огромный зал видеть в работе приходилось, хотя сам участвовал только в процессе разборки такого монстра на слом. Хорошо помню блоки памяти на ферритовых сердечниках, шкафы магнитофонов с огромными бабинами, шкафы с платами на дискретных транзисторах, целые платы с диодами и пр. Это колоссальная техника вызывает восхищение.

lingvo

А мне вот больше интересно, как и с помощью чего собирались решать аналогичные задачи в советской лунной программе. Был ли там примерно такой-же компьютер в разработке? Кто для него писал листинг и на каком языке? Что с микросхемами, если даже в США 60% всех выпускавшихся ИС шли в NASA?

Или вдруг может наши решили, что можно обойтись без компьютера вообще?

vp1000

Да, очень интересно. Только боюсь что не узнаем, в отличие от американской программы. Сначала все было засекречено, а потом было уничтожено, так и оставаясь засекреченным.

drWhy

Году в 1993 на лабах демонстрировали авиационный бортовой компьютер, состоящий из собранных в пакет плат (керамических?), на которых были смонтированы бескорпусные микросхемы, штук по 30 на плате, плат около 10.

Ещё рассказывали о вакуумных интегральных схемах.

Peacemaker

На аппаратах серии Зонд (некоторых, на шестом точно) устанавливалась ЭВМ Аргон-11С. Раньше можно было почитать об этом, например, здесь, правда, сейчас сайт недоступен.

VT100

Вот тут пристально интересуются БЦВМ Аргон: https://1500py470.livejournal.com/455372.html

А про 60% — думаю, это процент использованной номенклатуры, а не общего числа. У них тоже много на Минитмены уходило.

AndyKorg

Возможно вам будет интересна серия книг Чертока

Cirno_9

Кое-какие военные БЦВМ с похожей архитектурой, конструктивом и элементной базой до сих пор несут службу или только недавно списаны. С такими проектными нормами, а также благодаря специальным конструкторским ухищрениями (типа аппаратной побитной сверки каждой операции и умения «засыпать» по сигналу «вспышка», чтобы потом продолжить как ни в чем не бывало) они были вполне устойчивы к самым жестким боевым факторам.

А еще интересная параллель — популярный чип AVR Amtega328p, на котором построены наборы Arduino, имеет схожие с этим компьютером параметры: ОЗУ 2к, ПЗУ 1к, память программ 32к, при несравненно большем быстродействии. Современный чип едва закрывает ноготь мизинца. Интересно, что бы на его базе сотворили инженеры программы Аполлон, попади он им в руки в те времена! А современные разработчики? Справились бы? Смог бы заменить этот МК бортовой комп Аполлона?

TOPGAMERU

Аполон так-же как и Джемени, так-же как и Скайлеб.

Полностью мифическая программа с 20% от силы долей правды.

Обсуждать эту программу на полном серьезе не имеет смысла.

С таким же успехом мы можем обсуждать Звездные войны и компьютеры из них, лазерные мечи и джедаев.

ramzes2

В любой лунной статье самое интересное начинается с подобного комментария.

lingvo

Че, даже в существование этого компьютера не верите? А на него хорошая доля расходов на Аполлон легла.

TOPGAMERU

У Илона Маска в кармане электроники больше чем на всех Аполлонах вместе взятых.

А он даже не на пол пути к Луне.

И это господа показывает что такое прогресс и что такое регресс.

Со времен Аполлонов мощность лично моего компьютера выросла в 100500 раз.

На Лунную программу тратиться от 20 до 50 млрд ежегодно.

А воз и ныне там.

Более того в 2019 это даже смешно все читать, когда давным давно доказано что эта программа существовала только на бумаге.

Да были прототипы как у автора в статье, ракеты были, живые космонавты и все что хочешь, только к самой Луне это не имело ровным счетом ни какого отношения.

Это бутафория. Которая реально не является рабочим аналогом именно для настоящей Лунной программы.

Нет смысла изобретать велосипед заново спустя 50 лет его изобретения.

Однако США вливают в НАСА по 20 млрд в год и даже колеса от этого "велосипеда из прошлого" не имеют. Пусть возвращаются НАЗАД в БУДУЩЕЕ. Так будет честнее.

neonkainside

Так полностью или на 80%? А в чем измеряется мифичность? А Меркурий был? А Зонд? И даже в вашей системе коммент нерелевантен, здесь обсуждается БЦВМ, которая вот прямо на фото есть.

TOPGAMERU

Мифичность измеряется в недостижении основной цели. А именно в полете на Луну человеком. А то какие они понаделали красивые макеты на Земле и для Земли, это ни кого не интересует. Некоторые считают что летали они реально в космос уже при Шатлах.Я конечно думаю что это произошло гораздо раньше. Но опять же отними например от Джемени 80% вранья и что останется в итоге? Здесь обсуждается компьютер созданный на Земле, для Земли, в чем собственно нет ни чего "сверх выдающегося" для того времени. А то что это железяка не летала ни на какую Луну это даже не обсуждается. Это доказанный научный факт.

neonkainside

Если цель не достигнута, то откуда 20%? И что там с Меркурием? С Зондом?

Научные факты — это результаты научного эксперимента, наблюдения. Причем желательно предсказанные теорией. У вас таких фактов очевидно нет, а у этой БЦВМ есть в виде уголковых отражателей, слетавших кораблей, следов на фотках LRO, мешков грунта с Луны и много еще чего. Чтобы заявить, что американцы не летали на Луну, вам придётся придумать альтернативное объяснение всех имеющихся фактов, да еще и предсказать появление новых. Вы очевидно сделать этого не сможете. Посему научным фактом утверждение, что AGC не летал на Луну, не является.

PS: И "сверх выдающееся" в этой железяке очень даже есть кстати, о чем и серия статей.

TOPGAMERU

Как от куда. Полет в космос был? Был. Грунт привезли? Привезли. А то что главную цель не выполнили и ни каких людей на Луне не было это другой вопрос.

Часть от программы достигнута. Это 20%. У меня конечно есть факты. Добро пожаловать в Московский планетарий. В музей космонавтики и покажите мне там серую Луну, на которую высаживались доблестные Американцы.

Я больше скажу уже в 1974 году было известно, что Луна не серая.

Однако вы до сих пор рассказываете сказки, как США 6 раз из 6 возможных высадились на исключительно Серую Луну.

Про мешки грунта тоже не надо.

Это смешно даже звучит. Изучите для начала вопрос, прежде чем заявлять такое.

Вот я например про Меркурий и Зонд ни чего не скажу, требует отдельного изучения, но мне эта тема не интересна, ибо роботы меня на Луне не интересуют, это не ново. Тот же самый Китай это сделал в этом же году ( 2019 ) и в прошлом, что в этом сложного? А первые сделали мы!

neonkainside

Я думал вы что-нибудь интересное принесете. Какого же цвета Луна?

Алгоритм прост. Не знаете что-то > спрашиваете у Гугла > GOTO 1

TOPGAMERU

Да действительно гугл выдаст, что Луна это светло серый цвет. Однако при этом покажет первую же картинку это опровергающую. Где-то гугл врет. Я лично больше доверяю своим глазам, чем тому что пишут. Ибо лучше 1 раз увидеть, чем 100 раз услышать. А вы верите всему что именно ПОНАПИСАЛИ США. Именно этим и отличаются теоретики, от практиков. И как это не прискорбно, вы теоретики.

А для тех кто совершенно не в курсе ( однако рассуждает тут об электронике на полном серьезе ) так вот аппаратура позволяющая рассмотреть Луну в 500 кратном зуме есть в любом магазине той самой электроники.

Сейчас это даже телефоны современные позволяют сделать.

И цветность Луны там ой как хорошо видно и вот тут у меня печальные для Вас новости.

TOPGAMERU

Да посмотрел. Меркурий 20% правды. Зонд программа СССР и от сюда 100% правды. Все просто.

Проблема США в том, что надо было врать мелкими дозами.

Например: Не соревноваться с СССР что сразу после Юры полетели 2 Американца. Не запускать на Луну 6 раз 130 тонники. А врать по чуть чуть! Подождали бы пол годика. Запустили бы 1 раз муляж и сейчас бы никто не догадался. Тоже самое со скайлебом. Надо было не пытаться обогнать СССР как минимум в 2 раза! Что даже современные технологии не позволяют сделать.

В общем чем больше вранья, тем более вероятность быть пойманным за руку.

Что собственно и произошло.

Даже сами Американцы периодически ржут с сайта НАСА, ибо вранья там ОМГ сколько. Проще Звездные Войны смотреть и искать там правду, чем искать ее в НАСА.

elmm

Какое классическое хабро-самоубийство.

TOPGAMERU

Я просто указал по факту, что подобную статью мог написать только теоретик, который очень далек от космоса и космической тематики. Так же как я далек от балета например.

Он даже не понимает что баги ( о которых он говорит в своей статье и которые они быстро исправили попивая джус на диване ) На Луне исправить просто нереально. Что это может привести к фатальным ошибкам и не корректной работе системы. После чего безопасное возращение назад может быть под вопросом. Я уж не говорю про мелочи, что люди как всегда забили на степень радиационной защиты, температурной защиты, взрыво-защиты, применения адекватного охлаждения при повышенных температурах и прочего. Иными словами железяка для съемок в павильоне, ни в коем случае не для настоящей Луны.

Чисто пример: есть такой космо костюм "Орлан", этот скафандр во много раз превосходит те тряпки, в которых якобы США летали на Луну по степени защищенности.

Однако он не годится для Луны в нынешнем виде!

Иными словами есть 3 варианта одежды полицейского. 1) Парадный смокинг 2) бронежилет 1 класса защиты 3) костюм тяжелый "ратник" со степенью защиты 6а.

Так вот Американцы сейчас рассказывают и втирают всем сказки что они в парадном смокинге летали на Луну и выдержали очередь с АК-47!

Как-то так.

А минусят меня необразованные ребята верующие в этот кромешный бред.

lingvo

Можете конкретно рассказать неучам, почему «Орлан» не годится для Луны?