Интереса ради сделал несколько простеньких модулей (аля платки для встраиваемых систем), про которые и хочу рассказать и поделиться исходниками, вдруг кому пригодится. Да, эта статья не про ПЛИСовую тематику, а что бы её немного разбавить, хотя кого я обманываю, модули же с ПЛИСами.

Про каждый модуль писать отдельно не вижу смысла, поэтому будет статья - сборник, а чтобы добавить наукообразия в текст, буду комментировать особенности разводки, если таковые будут. И предлагаю начать от сложного к простому.

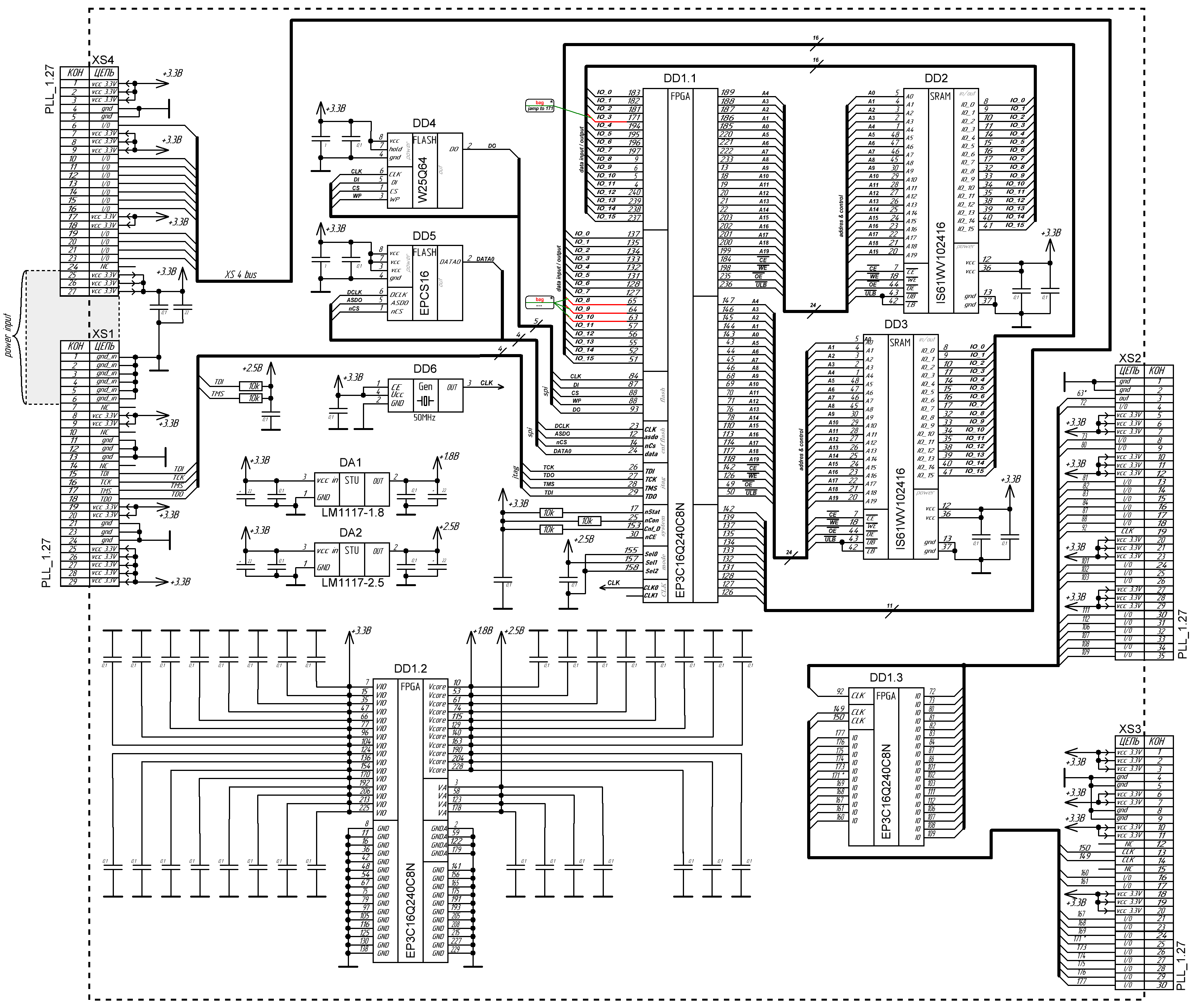

Встраиваемый модуль (CORE V8)

Сталкивался с проблемой, что нужен модуль с относительно жирной ПЛИСой и абсолютно минимальной обвязкой, но на али существует такая тенденция, что чем более мощная ПЛИС распаяна на отладочной плате, тем больше вокруг нее всего, что иногда может быть лишним в конкретной ситуации. Например, SDRAM которую везде ставят рядом с BGA ПЛИСами, в большинстве случаев действительно нужна, но бывают редкие случаи, когда она лишняя, а нужно, например, как можно больше свободных ног. И даже если есть возможность не использовать лишний функционал без ущерба в количестве свободных выводов, то в любом случае происходит существенные потери в компактности модуля.

Другая ситуация, когда может понадобится модуль с большой ПЛИС и минимальной обвязкой - когда строится 3D система, в формате стека из модулей, например со сквозным соединением краевых разъемов. Такая концепция может применяться для адаптивности функционала 3D сборки – путем комбинации модулей: на одном ПЛИС с минимальной обвязкой, на другом банк SDRAM/SRAM, на следующем NAND накопитель, далее модуль питания со стабилизаторами, модуль интерфейсов и т.д. и т.п.

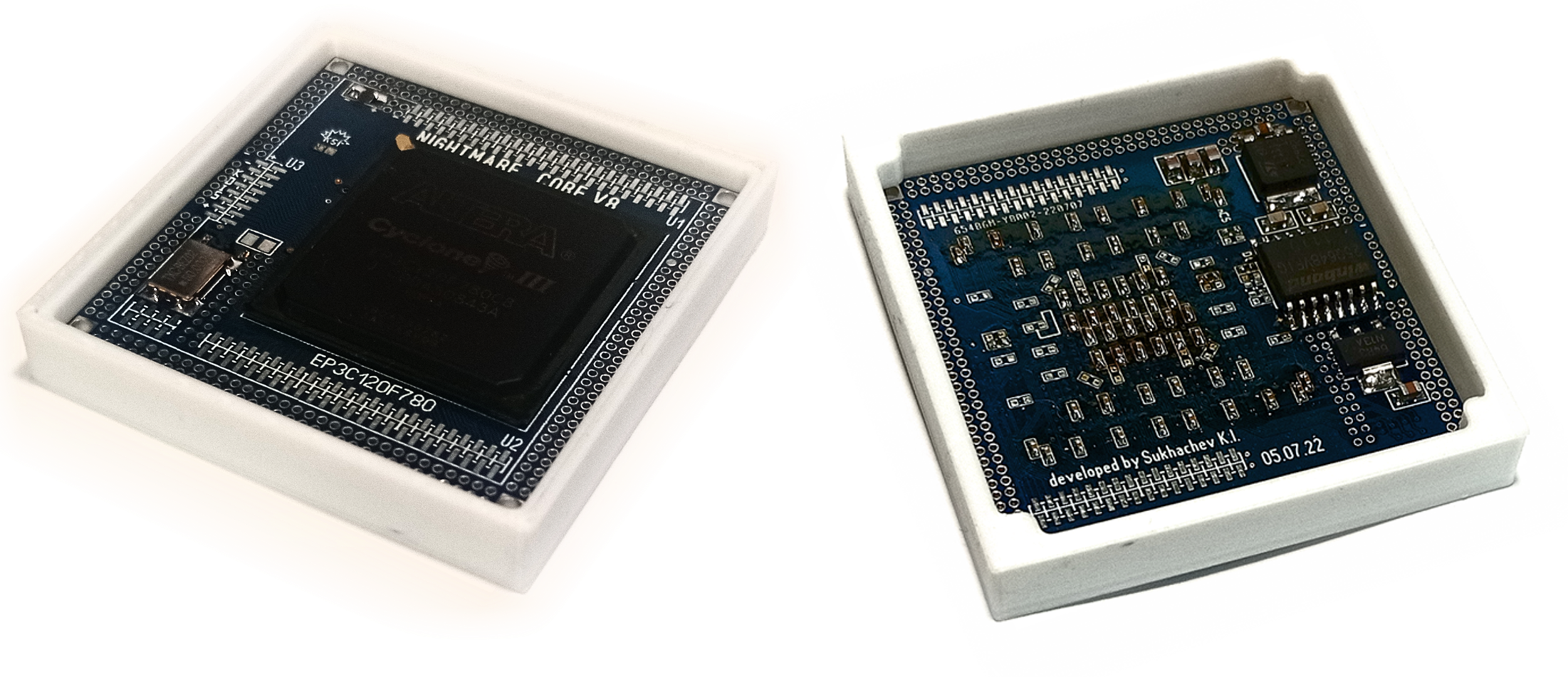

В общем в рамках озвученной концепции, как всегда в ночное время, родилась топология данного модуля под ПЛИС EP3C120F780, внешний вид модуля показан на рисунке 1.

Гербер файлы платы, а также исходники представлены в архиве по ссылке в конце статьи *.

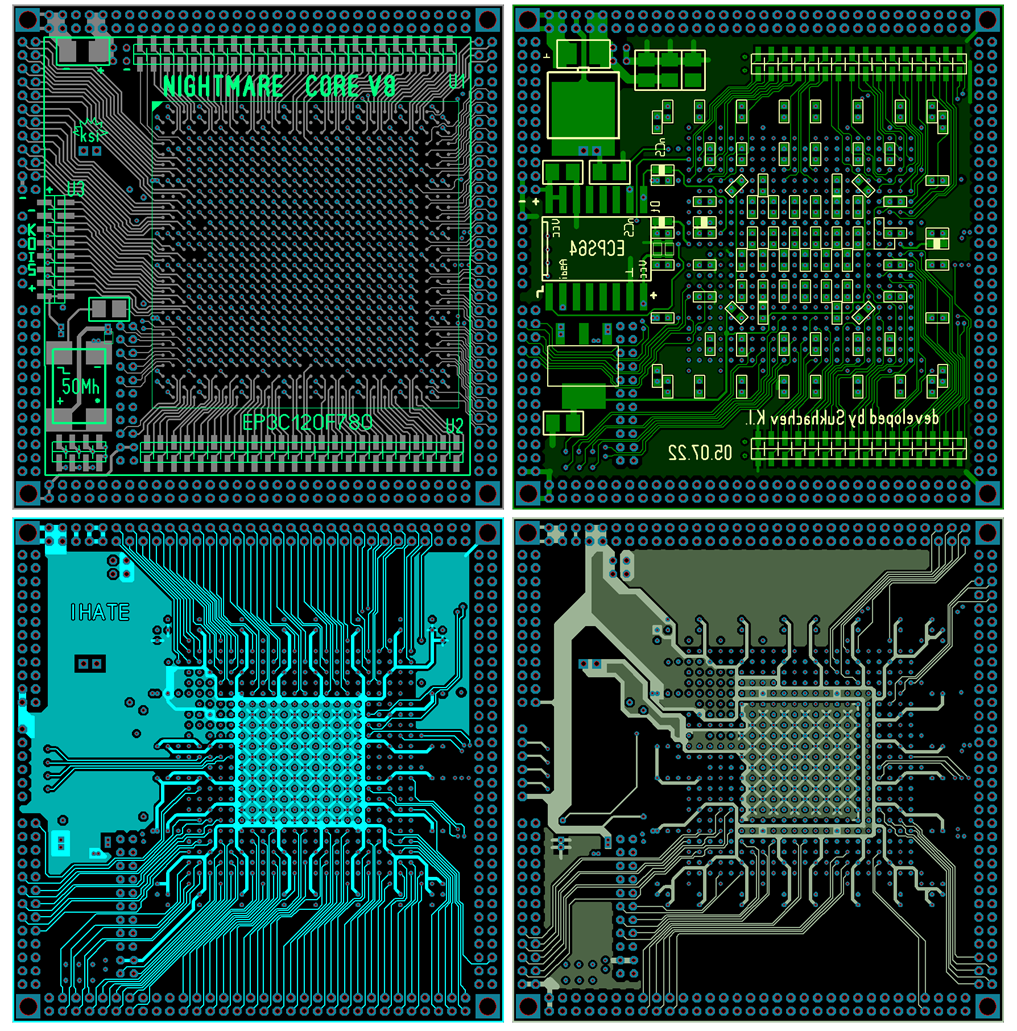

Модуль выполнен в 4 слоях, меньше для такого количества выводов просто не реально. Целевая технология печатной платы (ПП) – МПП со сквозной металлизацией переходных отверстий (ПО). Слои платы смешанные, так верхний слой отведен под трансляцию BGA выводов FPGA на остальные слои, а выводы первой очереди сразу на SMD площадки модуля. Внутренние слои МПП отведены под топологию цепей питания и земли, а также трассировку 2ой и 3ей очереди BGA выводов ИМС к разъемам модуля. Нижний слой отведен под посадку ИМС линейных стабилизаторов 1,2В и 2,5В, ИМС конфигурационной FLASH EPCS64, а также для посадки блокировочных конденсаторов формата 0402 (да мелко, но размещены так, что можно спаять и вручную). В нижнем слое так же разведены линии от выводов ИМС к разъемам модуля, что не уместились в остальных слоях. Полигоны земли, по возможности, залиты во всех свободных участках слоев для создания распределенной емкости сигнальных линий и линий питания. Иллюстрация топологии слоев показана на рисунке 2.

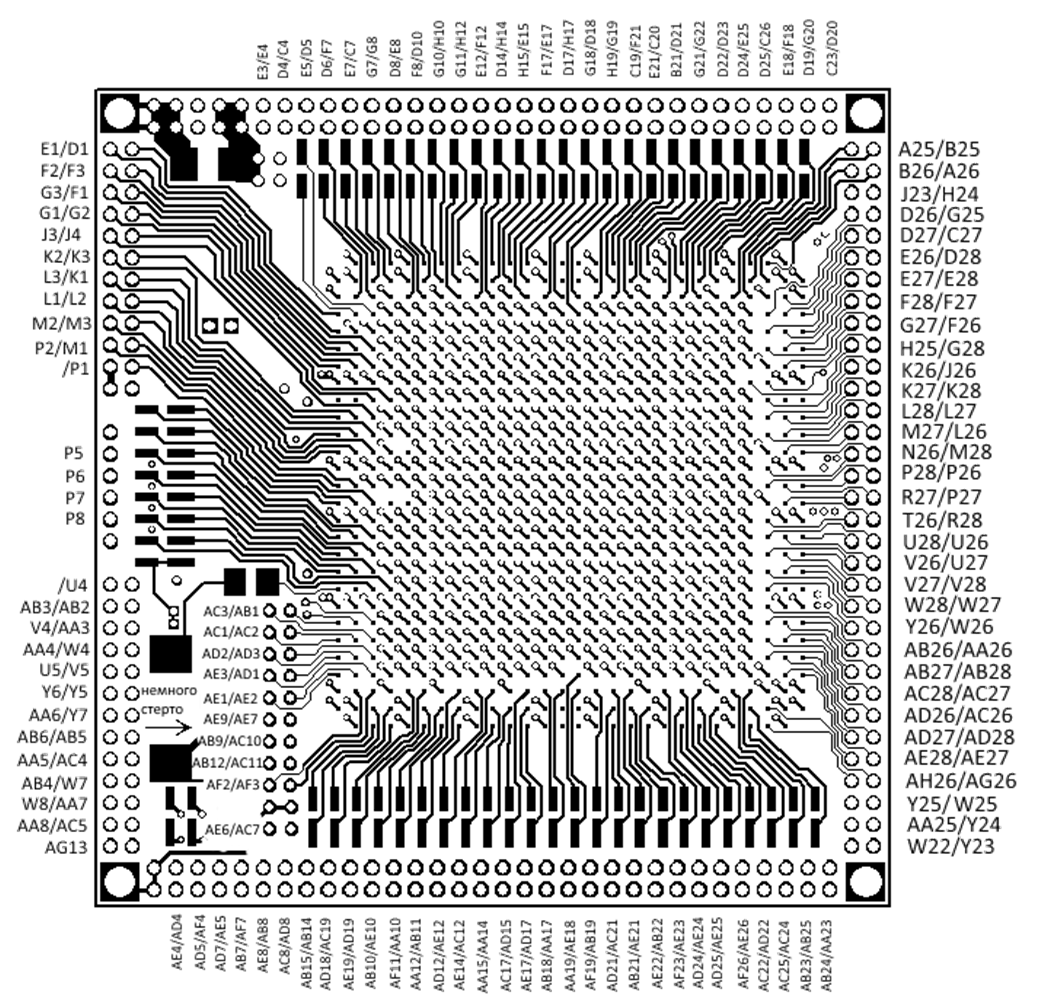

Карта периферийных выводов CORE V8 показана на рисунке 3.

Модуль (встраиваемая система FMU)

Встраиваемый модуль, адаптированный для синтезируемого CPU ядра NMR, описанного в статье.

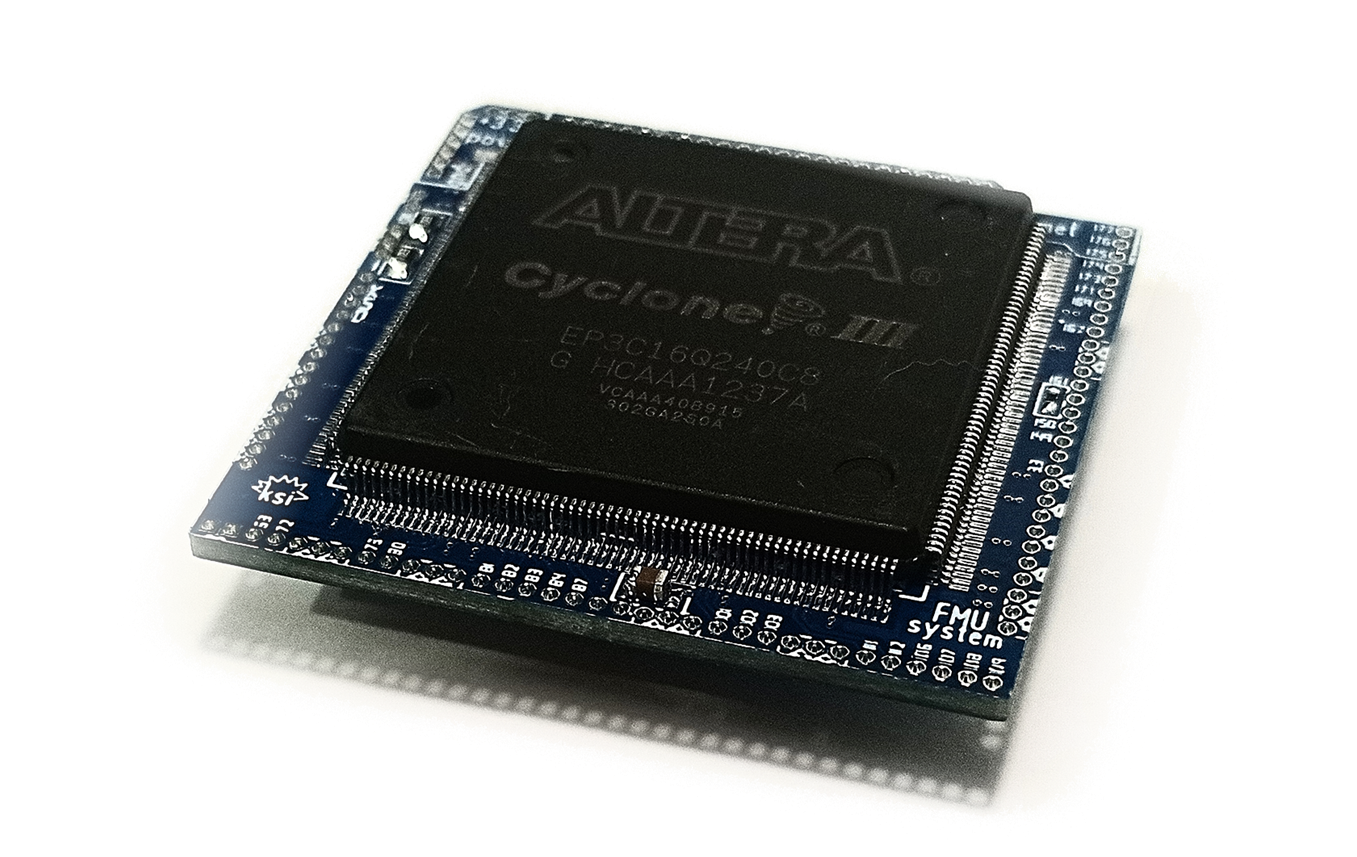

Модуль также построен на базе 4х-слойной ПП со сквозной металлизацией ПО. Старался сделать его максимально компактным и простым в самостоятельной пайке. Внешний вид модуля показан на рисунке 4, а его исходники и герберы по ссылке*.

Все элементы модуля паяются максимально просто, в том числе вручную, ИМС ПЛИС - EP3C16Q240C8 (с осторожностью EP3C25Q240C8) имеет выводной TQFP корпус с 240 ножками. Две ИМС SRAM IS61WV1024 также выводные, блокировочные конденсаторы и резисторы подтяжки в удобных для ручной пайки корпусах 0805.

Кроме перечисленных элементов модуль содержит: конфигурационную FLASH EPCS16, загрузочную FLASH W25Q64, цепи питания и защиты со стабилизаторами на 1,2В и на 2,5В и набором фильтрующих конденсаторов по входу питания.

Послойная топология модуля показана на рисунке 5.

В плане топологии можно отметить сдвоенные ПО, для снижения их паразитных параметров, а также для повышения надежности соединения. Внутренние слои отведены в основном для линий питания и целостного земляного полигона. Принципиальная схема модуля показана на рисунке 6.

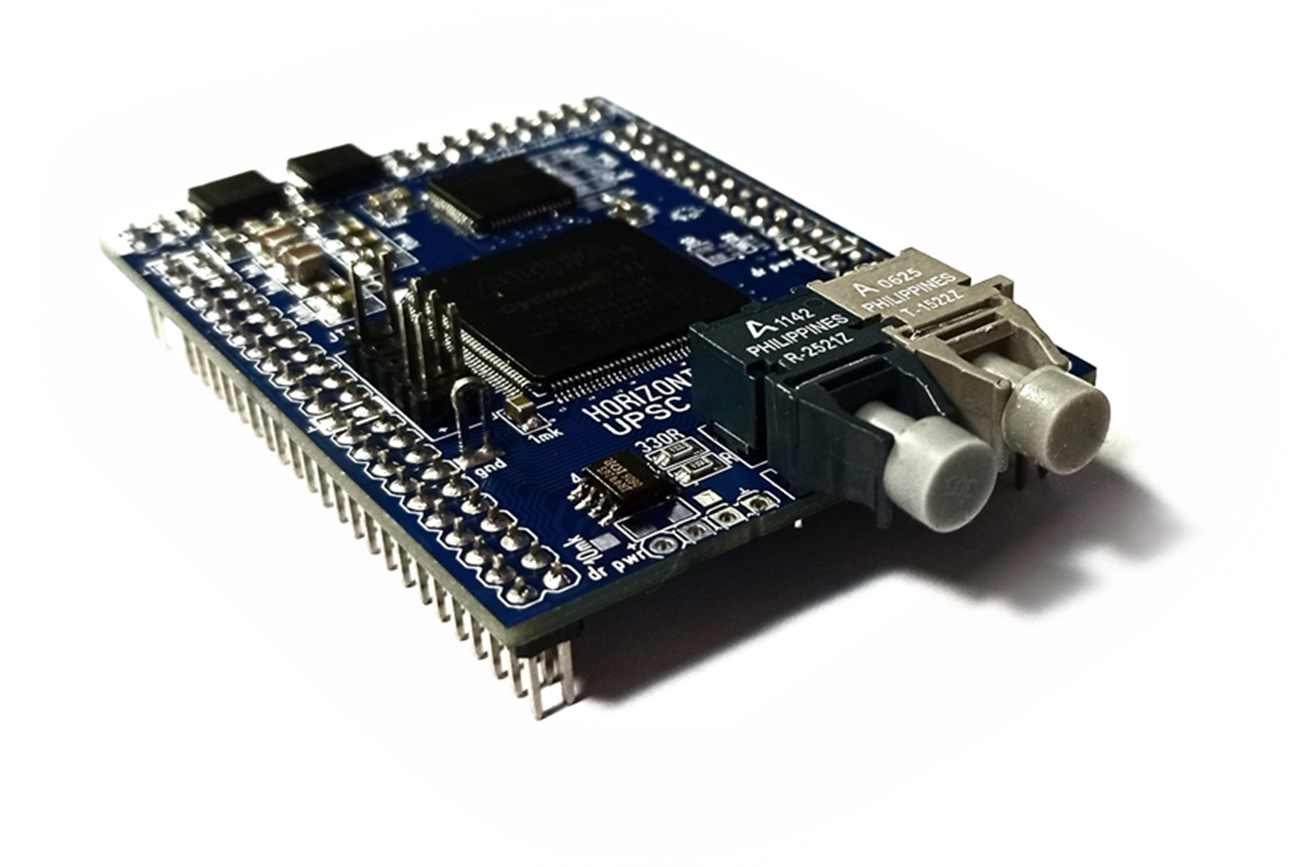

Модуль (система управления оборудованием Horizont V)

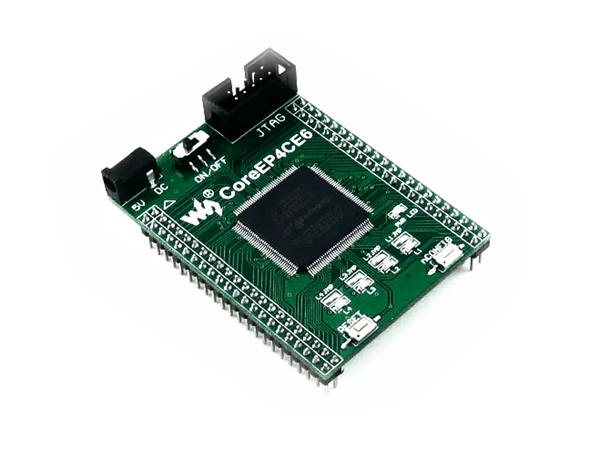

Модуль разрабатывался как некий автономный, исполнительный блок, оптимизированный под управление преобразователями (инверторами различной топологии). По посадочному месту модуль прямо совместим с популярным ранее (пока цены на него не стали кусаться) модулем с али, показанным на рисунке 7, но с существенно расширенным функционалом.

Внешний вид модуля Horizont V показан на рисунке 8. Модуль отличается по посадке тем, что существуют дополнительные разъемы и убраны разъемы питания. Т.е. модуль стал более оптимален в формат встраиваемой концепции.

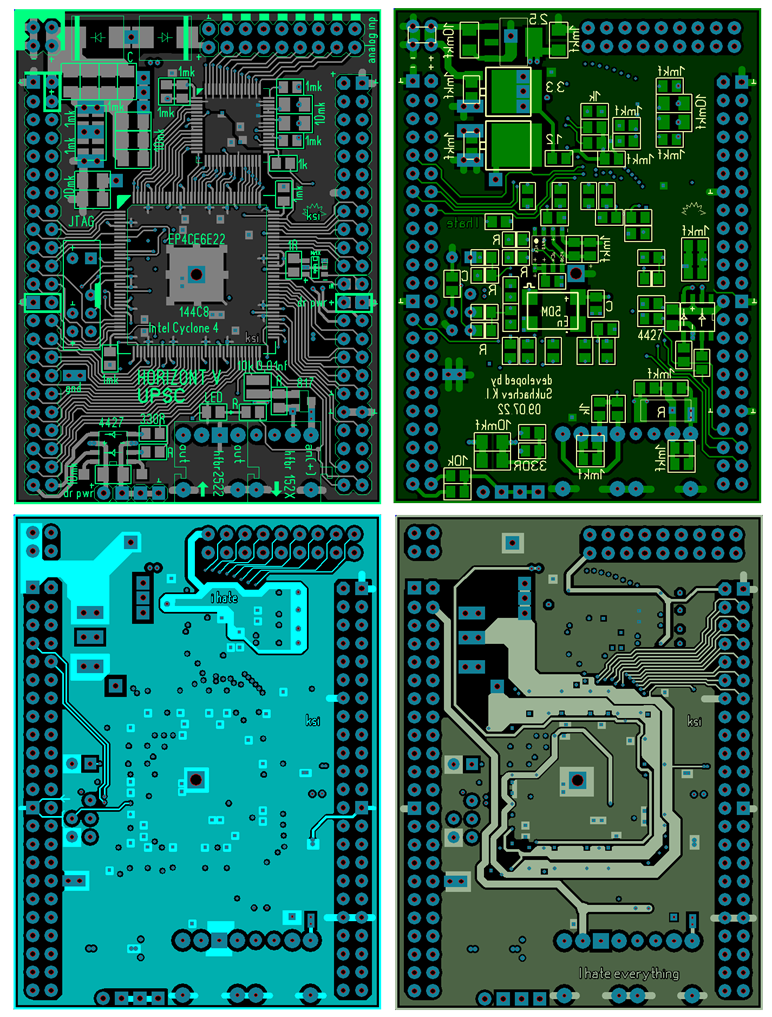

В основе модуля лежит FPGA Cyclone IV EP4CE6E22 – минимальная ИМС данного семейства в корпусе TQFP144, что позволяет легко её напаивать вручную. Кроме FPGA на борту модуля есть интересная 8-канальная 16-битная АЦП с одновременной выборкой по всем каналам, со встроенной фильтрацией и частотой дискретизации 200КГц. На модуле есть 2 двухканальных драйвера мосфет формата IR4427, или аналоги по посадке в корпусе SO8, есть быстрый компаратор MAX999 с внешними цепями задания уровней. Естественно, присутствует система питания всех ИМС, размещенных на модуле: стабилизаторы, блокировка, фильтрующие конденсаторы, защита. Для ПЛИС есть загрузочная FLASH EPCS16, кварцевый генератор, выделенный разъем JTAG. Особенностью модуля так же является наличие посадочных мест под оптические приемник и передатчик HFBR-2521 и HFBR-1522 или аналогичных. Что позволяет использовать модуль в аппаратуре требующей серьезной помехоустойчивости и изоляции (Оптический канал также позволяет реализовать интерфейс SINT, описанный ранее https://habr.com/ru/articles/769986/ , в варианте без дифференциального вывода.)

Послойная топология модуля, показана на рисунке 9. Модуль выполнен на 4-слойной МПП со сквозной металлизацией ПО.

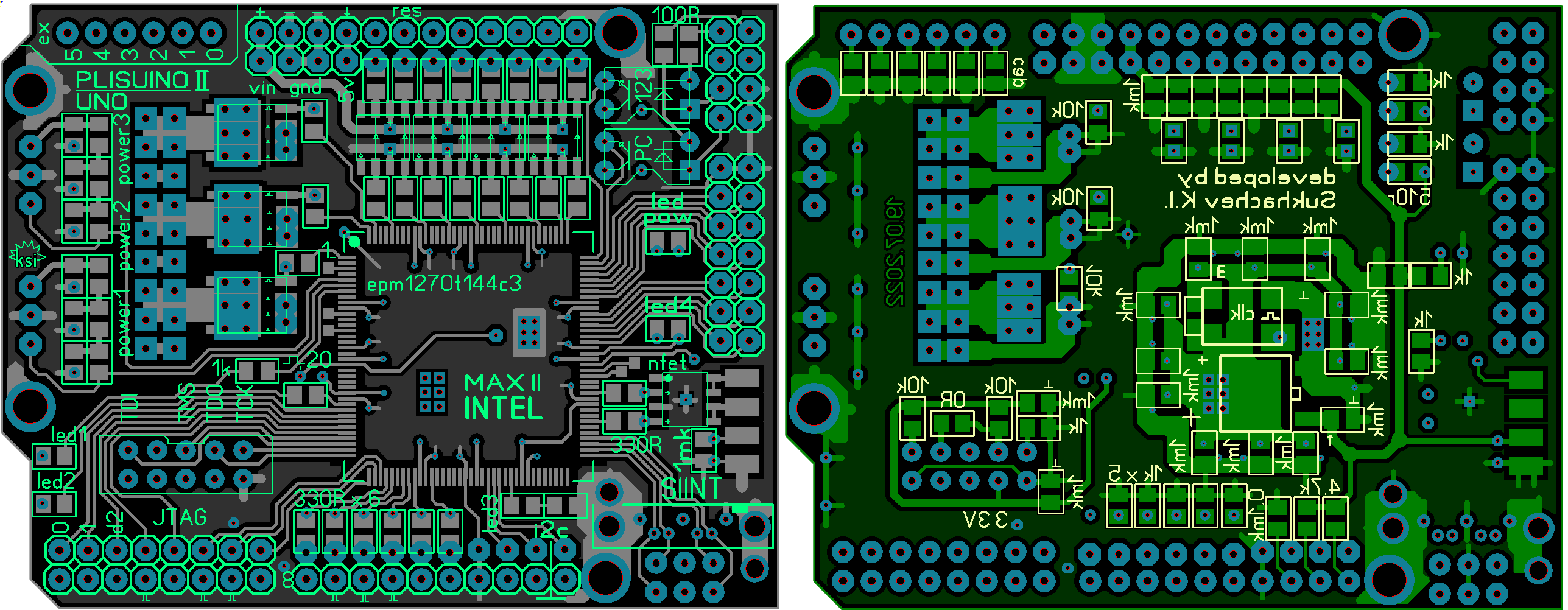

Модуль (PLISUINO) шилд к Arduino UNO

Просто модуль, содержащий неплохую CPLD MAXII EPM1270T144, на которой уже вполне можно сделать что-то интересное (1270 логических элемента, неплохая скорость и немного UFM). Кроме ПЛИС и всей необходимой для нее обвязки (генератор, питание), на модуле есть 3 мощных мосфета H8321, два мосфета послабее в SO8, 4 сдвоенных драйвера типа IR4427, 2 оптрона по входу PC123, пару светодиодов, RC фильтры для реализации ШИМ ЦАПов и заготовки под интерфейсы. Модуль почти без проблем стыкуется с платой Arduino UNO (нужны удлиненные PLS, а «аналоговую» колодку задействовать не нужно, по топологии если кто будет повторять все в принципе видно). Внешний вид модуля со всеми особенностями показан на рисунке 10.

Соединения ATmega и модуля предполагается осуществлять по SPI. Послойная топология показана на рисунке 11. Модуль на основе двухсторонней ПП, пайка не сложная все пассивные элементы SMD 0805.

Функционал, заложенный в модуль, может сделать его удобным для управления преобразователями (инверторами различной топологии), шаговыми моторами, сервоприводами, исполнительными блоками на реле или своими силами коммутировать мощную нагрузку. Возможности ПЛИС позволяют взять часть функций на себя разгрузим МК, и оставим ему функцию контроля основного алгоритма.

Заключение

По разводке ПП, могу отметить несколько практических подходов которые использовались при разработке представленных модулей, а также общих рекомендаций:

Не нужно мельчить, если речь не идет о очень тонких аналоговых цепях или СВЧ, нужно делать дорожки максимально широкими, что позволяет топология ПП, поэтому почти во всех модулях, представленных в статье довольно «жирные» сигнальные дорожки;

Цепи питания лучше делать в формате полигонов, перекрывающих полигоны земли;

ПО лучше делать по минимуму, чем их меньше, тем лучше, но если речь идет о надежности и минимальных паразитных параметрах, лучше их дублировать в непосредственной близости друг от друга;

Для отведения тепловой мощности лучше использовать ПО совмещенный с SMD контактной площадкой (Это справедливо только для ручной пайки, для автоматической такое недопустимо, т.к. дозированный припой затянется В ПО);

Удлиненные PLS позволяют очень дешево и просто делать многослойный бутерброд из плат;

Есть большая разница в подходах разведения ПП между серийным производством и штучным, в статье все модули для единичного – ручного или DIY производства. Отказавшись от некоторых ограничений серийных плат, если делаете опытное оборудование или для себя, можно добиться намного лучших показателей надежности, компактности и прочих ТТХ, взамен технологичности;

Не жадничать в слоях если нет особых требований к приемке ПП, слоев нужно столько – сколько нужно, получится надежнее и лучше. Цены на МПП сейчас адекватные…

Итого в статье я представил некоторые модули, для свободного использования тем, кому они могут пригодиться. Если будут запросы на такой формат статей (открытых и свободных для использования модулей) данный цикл статей можно продолжить.

П.С.: Кто будет использовать исходники – просьба не удалять лого ёжика!!

Комментарии (22)

forthuse

29.10.2023 13:38Модуль (PLISUINO) шилд к Arduino UNO

Лет 10-ть назад был сделан авторский модуль на FPGA (Xilinx) - Gameduino-1

а, потом автор уже сделал Gameduino-2 и 3 (Dazzler), но уже в более сложном варианте.P.S. Ниша таких модулей в концепции Gameduino, предположу, востребована и сейчас,

но в России таких упоминаний-разработок почти не слышно.

ShadF0x

29.10.2023 13:38Ниша таких модулей в концепции Gameduino, предположу, востребована и сейчас

Есть Arduino MKR 4000, не особо-то она популярна.

checkpoint

29.10.2023 13:38+1Может быть кому-то будет интересно, вот мой вариант платы на ПЛИС Lattice ECP5 (редкий зверь в наших краях) в форм-факторе RPi3, под названием Karnix ASB-254, заточенной под синтез RISC-V ядер. Проект полностью open source, выполнен в KiCAD 7. Помимо самих файлов проекта в репозитории присутствуют Gerber файлы, BoM и схема в PDF.

RV3EFE

29.10.2023 13:38Спасибо! Интересно. Сейчас будет ещё более редким в россии

checkpoint

29.10.2023 13:38+1Микросхему ПЛИС Lattice ECP5 в малых дозах (как водку) приобрести проблем нет - она есть на известной китайской барахолке за вполне вменяемые 850 руб. Но у бывших "официальных" поставщиков уже приобрести нельзя.

Сама ПЛИС Lattice серии ECP5 интересна тем, что она полностью задокументирована (читай - зареверсена) и отлично поддерживается Yosys-ом. Именно с целью проведения экспериментов по изучения синтезируемых ядер с помощью open source тулчейна и была спроектирована эта платка.

Megobari

29.10.2023 13:38Так для большинства то случаев и важно иметь возможность официально покупать партиями. Штучно - это уже для радиолюбителей, получается, для собственных нужд и отладок.

Поэтому сейчас многие фирмы в россии метаются между выбором панго и говин

checkpoint

29.10.2023 13:38ПЛИСы Gowin тоже поддерживаются в Yosys, но не полностью. Мне пока не удается синтезировать VexRiscV на GW1NR из-за проблем с размещением оперативной памяти. На говинах Yosys использует LUT вместо специальной памяти, и их разумеется не хватает.

nkie

29.10.2023 13:38+2Не нужно мельчить, если речь не идет о очень тонких аналоговых цепях или СВЧ, нужно делать дорожки максимально широкими, что позволяет топология ПП

Вот с этим в корне не согласен. Все сигнальные линии необходимо делать согласованного импеданса. Чаще всего 50 Ом. Тут конечно можно порассуждать в сторону "да что тут будет на таких коротких линиях", "да что тут будет на таких частотах". Но я говорю о принципиальных соображениях. Нет никакого смысла делать одну линию толще другой, если это позволяет топология, тк при таком раскладе есть нехилый шанс, что у вас развалются тайминги из-за несогласованных импедансов, если пользователь захочет на этом модуле какой-то высокоскоростной интерфейс поднять. Тому же DDR-у может сильно поплохеть.

VT100

29.10.2023 13:38Для сведения, EPCS64SI16N сняты с производства. Замена - EPCQ64ASI16N с 4-х битным интерефейсом.

mpa4b

29.10.2023 13:38Помнится, что EPCS64 были перемаркированными флешками от ST что ли (точно не помню), и те подходили в качестве замены. Аналогичные флешки от других производителей не подходили, т.к. копирасты и вендорлочеры из тогда ещё альтеры сверяли ID, получая его из флешки до собственно начала загрузки. Какая ситуация с EPCQ64 не в курсе, но можно предположить, что аналогичная.

В этом смысле идеальный вариант для загрузки -- это например примитивный контроллер (даже АВР, лишь бы фатфс влезла) и microSD. Дёшево, доступно, легко поменять или выбрать прошивку. Но да, не очень быстро (в смысле времени загрузки конфы в FPGA).

VT100

29.10.2023 13:38Да, на оригинальных EPSC даже шрифт маркировки - Томсоновский.

ЕМНИМС, сейчас официально одобрены помимо EPCx - Micron и Macronix. По крайней мере - есть app. note про их использование.

Также подозреваю, что если абстрагироваться от "прошивки" конфигуратора, то ПЛИС Intel должны бы грузиться с любой SPI-Flash 25-й серии.

kimstik0

29.10.2023 13:38"ПО совмещенный с SMD контактной площадкой"

Можно использовать переходные заполненные эпоксидкой или медью.

Как вариант можно переходное затянуть снизу маской, пузырек воздуха внутри не позволит втянуть припой.

RV3EFE

Модули понравились. Схемотехника олдскульно сделана, с шинами. Платы аккуратные.

Я только вместо LDO и линейных стабилизаторов заложил бы dc/dc. По цене есть просто за копейки, ядро и периферия будут так же отлично работать, а КПД будет на порядок лучше.

Yuri0128

Ну не факт, что заместо LDO у DC-DC будет лучший КПД.

RV3EFE

Ну вообще-то факт.

Напряжения даны, указаны в статье.

Можно взять разные входные и увидим что КПД будет лучше, особенно для стабилизатора напряжения ядра.

sim2q

а что там с токами?

может смысла нет усложнять т.к. это всё равно в стационарное

Nick_Shl

Я когда-то давно делал модуль на STM32. Тоже такой "Нафиг эти линейные стабилизаторы! Даёшь DC-DC!". Поставил LM3671MF-3.3, маленький такой, в корпусе SOT23-5, все круто, все работает... а потом как-то вместо подачи 5 вольт на соответствующий вход модуля, подал напряжение 3.3 вольта на выход модуля и этот DC-DC взял и сдох! Оказалось микросхема преобразователя совсем не переносит напряжения поданного на её выход. Пришлось заменить на линейный стабилизатор(ap2112-3.3 вроде, благо назначения ножек совпали), который такой болезнью не страдал.

Можно, конечно, начать аргументировать "А зачем ты подавал на выход?", но это же модули. Кто-то хочет питать модуль от внешнего источника питания 5 вольт, а кто-то хочет питать модуль от внешнего источника питания 3.3 вольт. И если ножки обозначены как +5V и +3.3V - кто-нибудь обязательно подаст туда 3.3 вольта.

rus-spb

Некоторые, например, TPS563207, LT8612, + полагаю, многие ещё, вполне нормально переносят подачу напряжения на свой выход. Уточню, штатного выходного (для данного блочка) напряжения, на его входе при этом ноль.

mpa4b

Просто комментарий насчёт источников питания для FPGA: полезно проводить для них "smoke test": в FPGA зашивается специальная прошивка, которая задействует (почти) всю логику на высоких частотах. Если мощности источников не хватает, то наблюдается перезагрузка по встроенным мониторам питания ПЛИС с последующим "исчезновением" залитой прошивки.

RV3EFE

Ещё ведь можно многое подключить на пины в плане нагрузки. У некоторых по 20-30 мА пин тянет, вроде бывают и больше. Ну а вообще верно сказали, смотря какое потребление. Но так как это модули, то наверное стоит закладываться на максимально возможное потребление.