Как‑то так cлучилось, что я вышел сначала на одну статью, а потом и на другие [1, 2, 3], в которых активно рекламировалась книга (ссылка на ее скачивание можно найти в [1]), посвященная проектированию цифровых схем [4]. Редкий по нынешним временам случай, когда реклама уделяет внимание совсем другим вещам. Так что со всех точек зрения все это, можно сказать, было делом случая. Ну, и конечно то, что в силу определенных обстоятельств мне эта тема интересна и, если как‑то себя обозначает, то меня это «цепляет» автоматически. Ну а дальше... как зайдет. Зашло.

Однако, ближе к теме... Со временем технологии проектирования цифровых схем и архитектур процессоров изменяются, совершенствуются, но базовая «арифметика» всех этих дел остается фактически неизменной. А это главное, т.к. всегда интересно — что же там новенького?

И вот, скачав бесплатную версию книги, я в который раз убедился, что как оно было этак 40–50 лет тому назад, так оно фактически и осталось. Но больше убило другое. В научном плане стало даже хуже. Теорию, судя по содержанию книги, нынче пролетают «по диагонали», что влечет за собой элементарные ошибки, характерные больше для студентов техникума, чем «вышки», на которых, судя по рекламе, эта книга рассчитана.

Нижеследующий разбор примеров из книги, надеюсь, это подтвердит. Но, если в чем‑то я не прав, то, как говаривали когда‑то, старшие товарищи меня поправят.

Итак, начнем...

1. Поведение автоматной программы в пределах переднего фронта тактового импульса

Авторы книги (далее — H&H) об этом рассуждают в подразделе 3.5 главы 3. Здесь вводится понятие апертурного времени (aperture) — времени, в течении которого входной сигнал должен быть неизменным. Речь идет о поведении схемы до и после переднего фронта тактового сигнала в пределах так называемого времени предустановки (setup time), т. е. времени до переднего фронта, и времени удержания (hold time) — времени после фронта. Сумма этих времен как раз и составляет апертурное время.

Для программных автоматов эти понятия приобретают несколько иное содержание. Но дискретное время и моменты его фиксации актуальны и здесь. При этом на моменты изменения входных сигналов, если не определить протокол взаимодействия с ними, повлиять сложно. Та же «обезьяна» (см. п.3.5.4 H&H), оперируя ими, готова сделать любую пакость в любой момент времени. И договориться с ней достаточно сложно: она должна быть послушной хотя бы в пределах апертурного времени, но такое вряд ли возможно — на то она и обезьяна.

Но адаптироваться к ее поведению при программной реализации автоматов не так уж сложно. Во‑первых, нужно считывать входной сигнал только один раз и строго после переднего фронта тактового сигнала, а, во‑вторых, выходной сигнал, как реакция на входной, устанавливать также один раз и до наступления очередного фронта тактового сигнала. Так мы исключим весьма вероятную метастабильность поведения автомата в пределах одного такта.

А если все будет так, как это представлено выше, то при частоте тактового сигнала более чем в два раза превышающей максимальную частоту входного сигнала (формально дискретный такт может иметь любое не равное нулю значение, т. е. по частоте увеличиваться до бесконечности) мы сможем распознать любой входной сигнал (принцип Котельникова). И пусть обезьяна жмет на входную кнопку, как ей заблагорассудится, основное в этом процессе, чтобы частота «давления» была минимум в два раза меньше тактовой частоты синхросигнала. Тогда такой автомат сможет повторить на выходе любой входной сигнал со сдвигом по времени на величину, равную времени между соседними передними фронтами тактового сигнала, т. е. aperture (см. рис. 3.50 в [4]). Или, если уж совсем по‑простому, то на величину присущей объекту задержки.

2. Импульсные помехи

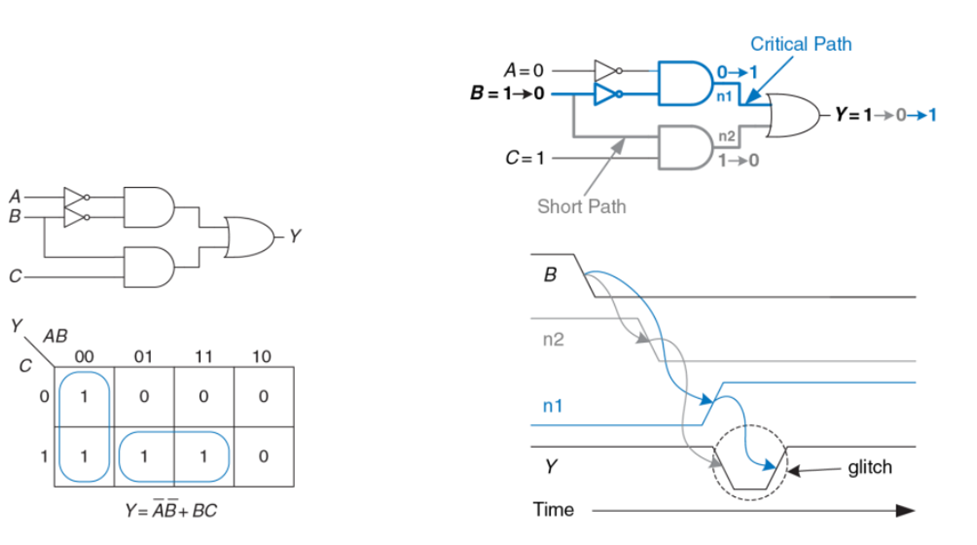

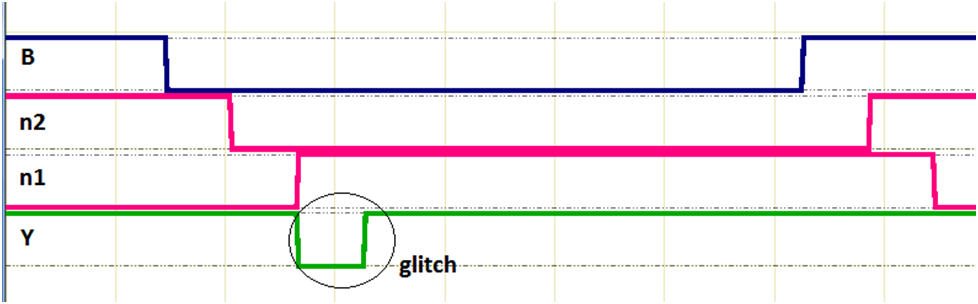

Сначала несколько слов про диаграммы сигналов, отображающих поведение сигналов логических схем. Поскольку мы договорились, что оперируем идеальными сигналами в двоичной форме, то наклонный вид их фронтов вызывает, прошу прощения, неуклонное возражение. То, как это хотелось бы видеть, мы покажем на примере из H&H, демонстрирующем импульсные помехи. В книге он представлен схемой на рис. 2.75, а временная диаграмма его работы на рис. 2.76. Ниже пример с диаграммой сигналов повторен на рис. 1, а на рис. 2 приведена диаграмма его работы в желаемой форме, полученной при моделировании схемы в ВКПа[5].

3. Метастабильность

Поговорим о метастабильности. В рамках данного ей определения в [4] — это некое промежуточное/неопределенное значение выходного сигнала. Довольно расплывчато, т.к. не ясно, каким видится H&H «неопределенное значение» в двоичной кодировки. Кроме того, нужно отличать метастабильность в пределах одного дискретного такта от метастабильности в течение нескольких. Первая ситуация устраняется описанным выше путем (см. поведение программы в пределах переднего фронта тактового импульса). Вторая предполагает фактически генерацию выходного двоичного сигнала, принимающего периодически значение 0 или 1. И именно подобное поведение логично было бы назвать метастабильным, хотя для этого есть и другое определение — генерация.

В подобное метастабильное поведение/состояние, например, способен входить RS‑триггер (модель триггера и доказательство его свойств см. в [5]). В такое же метастабильное состояние входят или могут войти и примеры схем, о которых далее пойдет речь. В H&H, если о таком поведении и говорится, то диаграммы сигналов, которые могли бы прояснить определение метастабильности, почему‑то не приводятся.

3.1. Бистабильная ячейка

Формальное доказательство бистабильного поведения RS‑триггера приведено в [5]. Аналогично можно доказать поведение бистабильной ячейки на инверторах. Схема бистабильной ячейки приведена на рис. 3 (см. также рис. 3.1. в [4]).

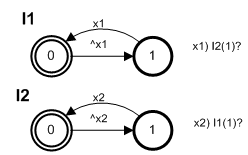

Модель бистабильной ячейки в форме автоматной сети приведена на рис. 4, а результирующий автомат для данной сети показан на рис. 5. Даже не зная про операцию умножения автоматов (см. [5]), получить его можно совсем просто — буквально «на пальцах». Для этого необходимо фиксировать, хоть теми же пальцами, различные комбинации состояний сетевой модели и определить возможные переходы из этих состояний, исходя из переходов компонентных автоматов сети.

Полученный результирующий автомат показывает наличие у бистабильной ячейки двух изолированных состояний и наличие метастабильного поведения. Попав в любое из изолированных состояний, бистабильная ячейка уже не способна будет его покинуть. Это и есть ее устойчивые состояния. Но нас больше привлекает метастабильное поведение ячейки, которое заключается в циклических переходами между состояниями 00 и 11.

Поведение бистабильной ячейки, смоделированное в ВКПа, показано на рис. 6. Действительно, — генерит. При запуске модель попадает сразу в одно из устойчивых состояний, а затем путем сброса ее можно ввести в метастабильный режим (режим генерации). Сбрасывая отдельные элементы схемы (в ВКПа это тоже можно делать) мы также можем перевести модель в режим генерации. Перевести модель в одно из устойчивых состояний можно, например, меняя свойства элементов ячейки. В нашем случае, изменяя тип задержек у элементов с транспортного типа на инерционный и обратно (о типах задержек см. также в [5]).

4. Неустойчивые схемы

Рассмотрим более сложные схемы — последовательностные, которые отличаются достаточно неожиданным поведением. Собственно это будут отражать примеры из [4], демонстрирующие метастабильное или неустойчивое поведение.

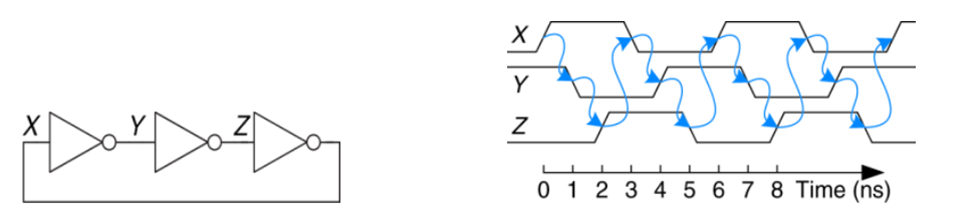

4.1. Кольцевой генератор на инверторах

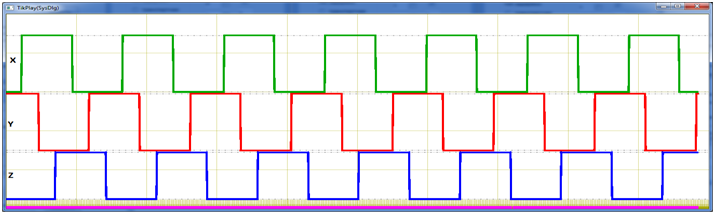

Сначала — кольцо из трех инверторов. Схема и временная диаграмма подобной схемы приведены на рис. 7. В [4] это, соответственно, рис. 3.16 и рис. 3.17. Кстати, в классической теории такое соединение инверторов будет считаться противоречивым, но практика, как ни странно, такое допускает (об этом см. [5])

Если собрать схему, состоящую из трех инверторов, в ВКПа, то получим такую же диаграмму, но имеющую иной вид сигналов (см. рис.8). Можно также заметить, что любая схема из нечетного числа инверторов представляет собой генератор прямоугольных импульсов. В том числе состоящая из одного инвертора.

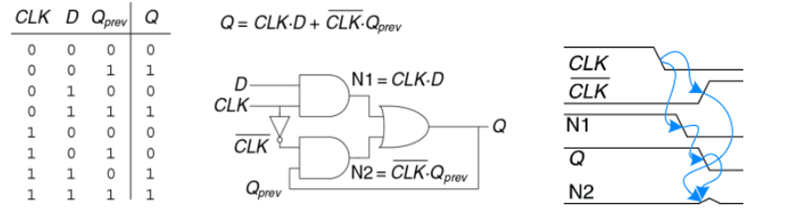

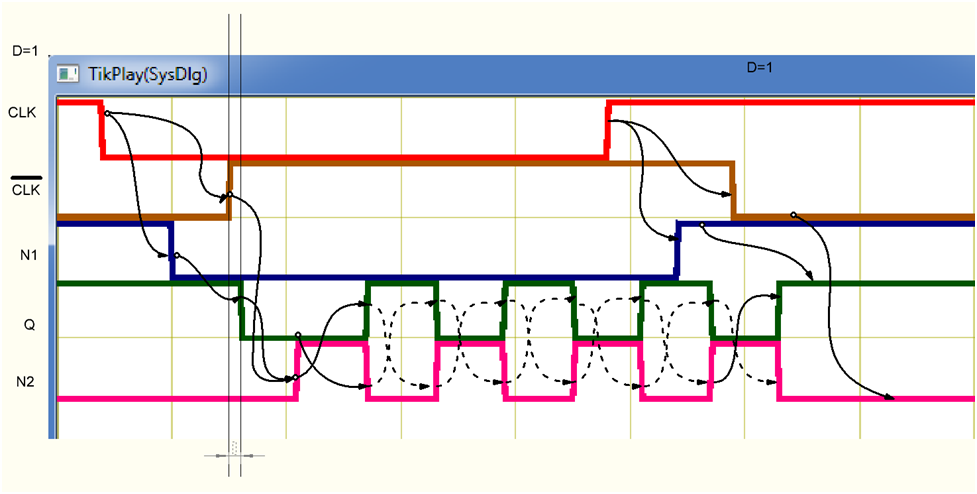

5. Гонки сигналов

Гонки сигналов в цифровых схемах могут привести к достаточно неожиданным эффектам. Рассмотрим это на примере D‑защелки, представленной на рис. 9. В [4] она приведена, соответственно, на рис. 3.18 (подробнее см. пример 3.4 в [4]), а диаграмма ее сигналов на рис. 3.19.

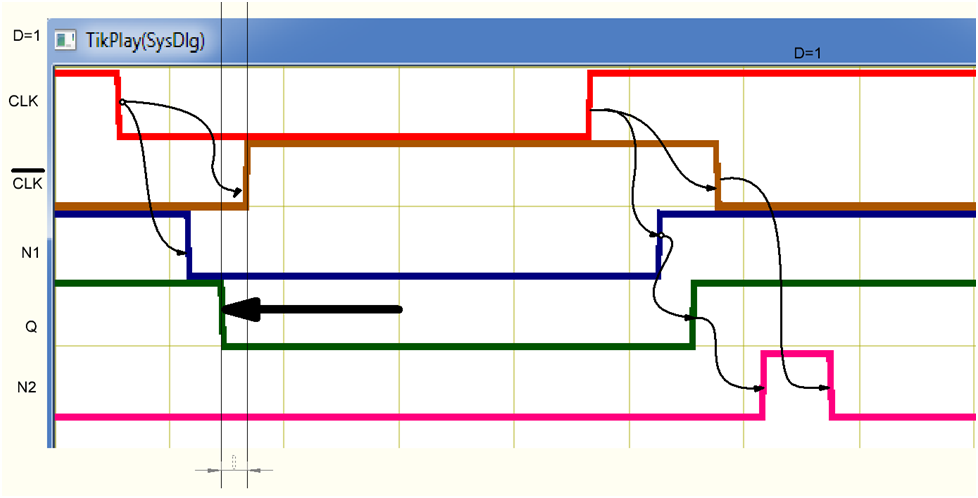

На рис. 10 приведены результаты моделирования схемы в ВКПа, когда задержка инвертора ровно в два раза больше задержки остальных элементов схемы. При этом задержки всех элементов имеют транспортный тип. Заметим, что в [4], в отличие, например, от [6], типы задержек почему‑то не рассматриваются вовсе (подробное описание типов задержек см. в разделе «Временное моделирование» в [6]).

По сравнению с результатами моделирования аналогичной схемы в H&H имеем явно другое поведение: среда ВКПа выявляет метастабильное поведение сигнала Q. В первоисточнике это лишь небольшой «пупырышек» сигнала N2 (см. рис. 9), которому почему‑то не хватило сил проскользнуть на выход схемы.

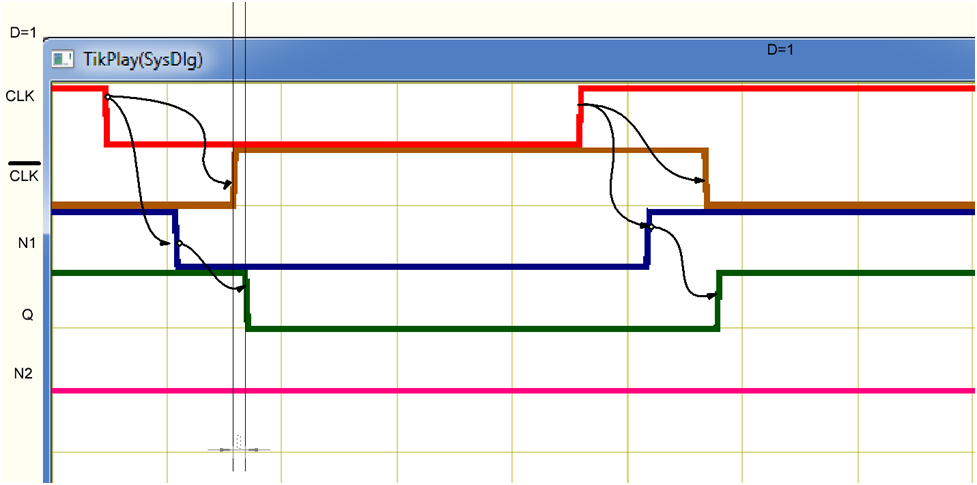

Совсем другое поведение будет у схемы, элементы которой имеют инерционный тип задержек (рис. 11). Здесь инерционный элемент, на выходе у которого должен появиться сигнал N2, не пропустит кратковременное единичное значение сигналов ^CLK и Q на его входах (видимо, он и представлен упомянутым выше «пупырышком»). В то же время для элемента с транспортным типом задержки этого времени оказалось вполне достаточно, чтобы на выходе появился импульс, который и спровоцировал последующее метастабильное поведение схемы.

Однако, если сдвинуть фронт спада сигнала Q по отношению к единичному фронту сигнала ^CLK влево, то это исключит установку сигнала N2, что в свою очередь сорвет процесс генерации. Это можно сделать, уменьшив задержку выходного элемента ИЛИ. Диаграмма сигналов подобного эксперимента приведена на рис. 12. Но при этом, уже при установке сигнала CLK, появится кратковременный импульс. Но его легко подавить. Для это достаточно, чтобы элемент И (см. сигнал N2), порождающий данный импульс, имел инерционный тип задержек.

Таким образом, устойчивость рассматриваемой D‑защелки определяется соотношением задержек инвертора и выходного элемента ИЛИ. Если оно будет подобно представленному на рис.10, то существует реальная опасность возникновения метастабильного состояния или, попросту, генерации. Правда, она, скорее всего, будет подавлена инерционным характером нижнего элемента И (см. рис. 11), т.к. реальные элементы по своей сути инерционны. Но, чтобы генерацию исключить совсем, нужно гарантированно увеличить задержку инвертора. Правда, как схема при этом будет воспринимать информационный сигнал D (тут могут быть проблемы) пусть все же лучше объяснит Бен Бидтидл — автор данной схемы (см. [4]).

6. Заключение

Выше мы рассмотрели некоторые проблемы поведения цифровых схем. В случае комбинационных схем это могут быть импульсные помехи, которые с течением времени, т. е. при переходе их в установившийся режим, исчезают. Для схем последовательностного типа гонки сигналов могут привести к метастабильному поведению схемы (самовозбуждению схемы). И действительно «подобные ошибки весьма сложно выявлять» (см. стр. 298–299 в [4]). И здесь нам в помощь будут конечные автоматы и приемы их аппаратной реализации. Хотя это уже тема для отдельного разговора. Опять же это можно сделать на основе анализа примера из [4] — модели светофора. А там, к счастью, а для кого‑то, думаю, и к сожалению, тоже есть о чем поговорить.

Однако, интерес продолжить такой разговор для автора выражается, как минимум, количеством «плюсов» за данную статью. Из чего я исхожу. Например, что там скрывать, количество «минусов» за мою предыдущую статью [7], которая выявила явные проблемы с анализом работы даже элементарных параллельных процессов, слабо мотивирует на работу. Пусть, например, такой границей будет 40+. Ведь, нашлось же 38 человек, поставивших «плюсы» статье [8], содержащей так и не разрешенную проблему использования общего ресурса в форме переменной‑счетчика? И, что примечательно, ее автор так и не соизволил подключиться к обсуждению проблемы. А кому, как не ему, озвучить, что он ожидал, и согласен ли он с результатами обсуждения данной проблемы.

Описанная ситуация, как мне представляется, довольно странная: мы с большим желанием хотим видеть только лишь то, что мы хотим видеть, и с усердием, достойным лучшего применения, минусуем тех, кто пытается разрушить подобные иллюзии.

Думаю, что и этот мой критический взгляд на столь разрекламированную книгу, которую, если опять же верить рекламе, собираются срочно внедрить в учебный процесс чуть ли не все ведущие высшие учебные заведения США и России (а за ними, видимо, подтянутся и другие) вызовет оценку, выраженную соответствующим числом «минусов». Но я тут бессилен что‑то сделать и хоть как‑то изменить свое мнение, т.к. передо мной лежит книга для техникумов железнодорожного транспорта 70-х годов времен СССР [9], которая в научном плане гораздо полнее раскрывает темы, затронутые в рамках обсуждаемой книги.

Конечно, в 70-х годах в CCCP не подозревали, что скоро появится VHDL и новые технологии проектирования цифровых схем, а потому не включили в упомянутый выше учебник соответствующие главы. Тем не менее, базовые — научные основы остались теми же. А потому скатываться на уровень ниже, чем уровень техникумов в CCCP, представляется не очень правильным, если не сказать — опасным. Пусть об этом не подозревают американцы, но россияне могут купить за совсем символическую цену вторую версию упомянутого учебника на том же WILDBERRIES, как это сделал автор, приобретя его более расширенный вариант [10], и оценить куда же мы катимся в научном плане. Да и ценность книги и понимание затронутых в ней тем студентами определяется совсем не ее объемом, а содержанием.

А то, что я в своих статьях часто ссылаюсь на труды наших ученых — В.М. Глушкова, С.И. Баранова, А.Н. Мелихова, Д.А. Поспелова и, касаясь текущей темы, С.А. Майорова и Г.И. Новикова и прочая и прочая... не счесть просто, не похоже, чтобы кого‑то убеждало. При этом не столь часто, как они того заслуживают, упоминаю А. Тьюринга, Дж. фон Неймана, М. Минского и многих других «заморских» ученых и исследователей, из которых, кстати, в H&H удостоились чести быть упомянутыми лишь Ч. Беббидж, да Дж. Буль. Может здесь «собака порылась»?

Но неужели сонм помощников и рецензентов, упомянутых в разделе «Признательность за поддержку» или ведущих специалистов, участвовавших в переводе данной книги, не заметили очевидных недостатков книги H&H? Это, безусловно, не перечеркивает тех положительных качеств, которые, несмотря ни на что, имеет данная книга. А это тоже есть, т.к. иначе она была бы мне просто неинтересной. Но все же студенты высших учебных заведений должны глубже вникать в тему, чем учащиеся техникумов времен СССР. Ну, или хотя быть на их уровне... Иначе совсем беда — будем говорить на разных языках.

Литература

Как я убеждал блондинку Машу перейти с программирования RTOS в проектирование железа (а также Coq, Lisp и Haskell). [Электронный ресурс], Режим доступа: https://habr.com/ru/articles/732700/ свободный. Яз. рус. (дата обращения 21.11.2023).

Избранные места из популярного учебника микроэлектроники на русском, который наконец-то выходит на бумаге.. [Электронный ресурс], Режим доступа: https://habr.com/ru/articles/317558/ свободный. Яз. рус. (дата обращения 21.11.2023).

Самый по-человечески написанный учебник компьютерной архитектуры наконец-то выходит на русском языке и для RISC-V. [Электронный ресурс], Режим доступа: https://habr.com/ru/articles/597603/ свободный. Яз. рус. (дата обращения 21.11.2023).

Хэррис Д.М., Хэррис С.М. Цифровая схемотехника и архитектура компьютера. - 2-е изд.

Автоматное программирование: определение, модель, реализация. [Электронный ресурс], Режим доступа: https://habr.com/ru/articles/682422/ свободный. Яз. рус. (дата обращения 21.11.2023).

Армстронг Дж.Р. Моделирование цифровых систем на языке VHDL: Пер с англ./М.: Мир, 1992. – 175 с.

Параллелизм без потоков: очевидно и вероятно. [Электронный ресурс], Режим доступа: https://habr.com/ru/articles/765676/ свободный. Яз. рус. (дата обращения 21.11.2023).

Многопоточность в Python: очевидное и невероятное. [Электронный ресурс], Режим доступа: https://habr.com/ru/articles/764420/ свободный. Яз. рус. (дата обращения 21.11.2023).

Грицевский П.М., Мамченко А.Е. Основы импульсной и вычислительной техники. Учебник для техникумов. – М.: "Сов радио". 1974. – 296 с.

Грицевский П.М., Мамченко А.Е., Степенский Б.М. Основы импульсной и вычислительной техники. Учебник для техникумов. – М.: "Сов радио". 1979. – 392.

Комментарии (85)

Yak52

22.11.2023 16:09+2Если собрать схему, состоящую из трех инверторов, в ВКПа, то получим такую же диаграмму, но имеющую иной вид сигналов (см. рис.8).

В чем иной вид сигналов? В том, что в книге фронты сигналов показаны как имеющие время нарастания?

lws0954 Автор

22.11.2023 16:09-1При двоичной кодировке сигнала времени нарастания нет. Или есть? Может, я что-то не догоняю? :)

TaGUNil

22.11.2023 16:09+8Но в реальной-то схеме есть. И разработчик реальной схемы не может его не учитывать, от него максимально допустимая тактовая частота зависит.

lws0954 Автор

22.11.2023 16:09В реальной, да, есть. Но пока речь не идет о максимальной частоте, а лишь о логических схемах, оперирующих двоичной логикой, то этих фронтов нет. Ими пренебрегают. И правильно делают. На этом уровне есть только 0 и 1 и ни каких (!) промежуточных значений - тех же фронтов.

Но если необходимо учитывать фронты, то это уже должна быть другая книжка и кодирование сигналов будет уже не двоичным. В упомянутом учебнике для техникумов этому как раз посвящена почти его половина, т.е. импульсной технике.

TaGUNil

22.11.2023 16:09+4В учебнике по схемотехнике фронты нельзя не учитывать. Понятно, что это разные уровни абстракции, но разработчик должен иметь представление, что там внизу.

lws0954 Автор

22.11.2023 16:09Безусловно, должен иметь представление. И в техникуме ему это представление давали. Но только на том уровне абстракции, на котором написана обсуждаемая книга, фронты сигналов в процессе ни как не участвуют. Чистая дискретная логика.

iggr63

22.11.2023 16:09Реальные схемы теперь в ПЛИСах. И у разработчиков заливших битовый поток и наступает jitter. Конечно критерии синтеза проверяются на реализованность, но в сложных системах как цифровые радиочастотные трансиверы, воплощение на железе приходиться отлаживать и отлаживать.

lws0954 Автор

22.11.2023 16:09+1Реальные схемы теперь в ПЛИСах...

И что в ПЛИСах учитывают фронты?

checkpoint

22.11.2023 16:09+6Не только учитывают, static timing analysis это вообще овнова основ в плисоводстве. Без STA вы сможете сделать схему простейшего дешифратора, но вот схему многобитового суммутора уже не получится - она у вас просто не заработает на более-менее приемлимых частотах. Фабрика ПЛИС это такой же неидеальный аналоговый мир, как и все вокруг нас.

iggr63

22.11.2023 16:09Я небольшой специалист но можно сказать что фронты учитываются в виде setup и hold задержек.

KotovladeletsGT

22.11.2023 16:09К своему удивлению обнаружил, что в нашем ЖД вузе эти особенности поведения комбинационных схем (у нас они назывались "состязания") объяснялись на хорошем уровне при том, что до сих пор применение цифровой электроники для систем ЖАТ не сильно распространено - почти все системы построены на электромагнитных реле.

lws0954 Автор

22.11.2023 16:09+1И правильно делали. Эти "состязания" есть и в схемах на электромагнитных реле. Ключ он и в Африке ключ - будь то на транзисторе или реле ;).

KotovladeletsGT

22.11.2023 16:09+2Конечно есть, но всё же релейные схемы проектируются не как схемы с логическими элементами. Никто на реле отдельные "И", "ИЛИ" и прочее делать не будет. Так что да, состязания есть, но есть и свои тонкости. Для анализа работы релейных схем с учётом всех замедлений используют вот такие диаграммы

lws0954 Автор

22.11.2023 16:09-1Конечно есть, но всё же релейные схемы проектируются не как схемы с логическими элементами. Никто на реле отдельные "И", "ИЛИ" и прочее делать не будет.

Ну, это далеко не так. Возьмем теорию того же Гаврилова М.А. А нынешнее программирование для ПЛК? Там до сих пор один из базовых языков - язык релейных схем. Да, при реализации могут быть свои тонкости, но на уровне логики принятия решения все можно описать и описывают, используя понятие идеального реле.

checkpoint

22.11.2023 16:09+4Релейные схемы в ПЛК это всего лишь аналогия, причем не очень удачная, предназначенная для того, что бы электрик (не электроник и не программист) смог быстро "запрограммировать" простой алгоритм управления производственным процессом. К цифровым схемам и синтезу это не имеет ни какого отношения, как и к электромеханическому прибору который принято называть словом "реле". И тут уже было верно замечено, реле (прибор) это катастрофически нестабильный, ненадежных элемент, который когда-то по чистой случайности использовался в цифровых схемах и был быстро заменент электровакуумными приборами. Рассматривать реле как идеальный элемент с двумя состояниями просто глупо.

Katarsis29

22.11.2023 16:09+1Как человек, принимающий участие в разработке МПЦ, позволю с вами не согласиться.

KotovladeletsGT

22.11.2023 16:09Приятно видеть специалиста по своему направлению! С чем конкретно вы не согласны? Как я понимаю, с моими словами про то что большинство ЭЦ у нас релейные?

TaGUNil

22.11.2023 16:09Но адаптироваться к ее поведению при программной реализации автоматов не

так уж сложно. Во-первых, нужно считывать входной сигнал только один

раз и строго после переднего фронта тактового сигнала, а, во-вторых, выходной сигнал, как реакция на входной, устанавливать также один раз и до наступления

очередного фронта тактового сигнала. Так мы исключим весьма вероятную

метастабильность поведения автомата в пределах одного такта.Погодите, но при чём тут программная реализация? Это же учебник по цифровой схемотехнике, а не по программной реализации конечных автоматов.

lws0954 Автор

22.11.2023 16:09-1Погодите, а Вы разве не в курсе, что, если создается формальная модель чего бы то ни было (в форме того же конечного автомата), то ее реализация должна в точности ей соотвествовать? А какой будет реализация - программной или аппаратной принципиального значения не имеет. Ну, аппаратная будет быстрее. И только.

checkpoint

22.11.2023 16:09+1Аппаратная реализация автомата никогда, запомните это, никогда не будет на 100% соответствовать формальной (и программной) модели, как модель атомного ядра на 100% не соответствует реальному мироустройству. Формальная модель это астракция, сущность в головах людей. А аппаратная реализация - все эти фронты, глитчи, пограничные случае, глюки вызванные нестабильностью линий питания, температрные эффекты и прочее, прочее... По этой же причине ни одна верификация не даст Вам стопроцентного ответа на вопрос "соответствует Ваш дизайн спецификации или нет" - пока "в натуре" не испытаешь - не поймешь. Но это не значит, что верификация не нужна, совсем на оборот!

lws0954 Автор

22.11.2023 16:09Аппаратная реализация автомата никогда, запомните это, никогда не будет на 100% соответствовать формальной (и программной) модели

Ну это совсем не так. А потому не ставьте телегу впереди лошади. Реализация делает реальной ту модель, которую "в головах" создают люди в форме блок-схемы, автомата и т.п.. И искуство разработчика заключается в том, чтобы довести реализацию до того состояния, чтобы она на 100% соотвествовала задуманному "в голове". И верификация служит этому, чтобы выявить все косяки и довести реализацию до 100%-го совпадения. Чтобы в идеале, глядя на некий "черный ящик" нельзя было отличить аппаратную реализаци от программной. Вот что надо помнить и запомнить.

TaGUNil

22.11.2023 16:09+2Так ведь подраздел 3.5 главы 3 посвящён не созданию формальных моделей в форме конечных автоматов, а особенностям реализации последовательностных схем на реальных D-триггерах, которые обладают реальными временными характеристиками. Получается, что претензия в основном к смешению уровней абстракции?

lws0954 Автор

22.11.2023 16:09-1Реальные временные характеристики не должны влиять/искажать работу модели. В классике рассматривают реализацию не только на D-триггерах, но и на T- и RS- триггерах. И как-то временные свойства этих элементов не влияют на конечный результат. Или, скажем так, такого влияния быть не должно. А особенности могут быть.

TaGUNil

22.11.2023 16:09Так вот чтобы этого влияния не было, необходимо понимать, насколько эта модель вообще реализуема на данных элементах с данными временными свойствами, а точнее - какие временные свойства будут у корректной реализации.

TaGUNil

22.11.2023 16:09+2Вы это, безусловно, понимаете, но мне в таком случае непонятна претензия к конкретному подразделу книги. Ведь читатель тоже должен это понять.

lws0954 Автор

22.11.2023 16:09Я претензий не предъявлял. Если реализация на D-триггера в точности соотвествует формальной модели автомата, то какие могут быть претензии. По мне спорны "терки" вокруг переднего фронта синхросигнала. Я согласен, что реальный сигнал должен быть стабильным в пределах апертурного времени. Но только как Вы сможете указать "обезъяне", чтобы она держала сигнал стабильным? Возьмем, например, дребезг кнопки. Как Вы сможете указать ей, чтобы она не дребезжала? ;) Вы можете только как-то изнутри игнорировать этот дребезг, например, поставив задержку, фильтр или что-то еще. И все! Изменение входного сигнала от Вас не зависит. Хоть трижды объявляйте необходимость стабилизации входного сигнала. Ей (кнопке, обезьяне и т.п.) плевать на Ваше желание - они будут себя вести как им заблагорассудится. Так что претензий к реализации модели нет. Пока нет :) А вот к пожеланию разработчика иметь стабильный сигнал в течение аппертурного времени - есть. Они необоснованны. Ишь чего захотел - чтобы "обезъяна" его слушалась! :).

YuriPanchul

22.11.2023 16:09+4Ни SR-зашелки / RS-триггеры, ни T-триггеры (за особым исключением очень редкого low-power счетчика, подтверждающим правило) не возникают в реальной жизни front-end RTL designer-а (проектировщика на уровне регистровых передач) в электронной компании, проектирующей ASIC-и. Тем более оно не возникает в жизни верификатора (Design Verification engineer).

Это все можно без потери для производства просто пропустить вместе с JK-триггерам или упомянуть в порядке научпопа. И сразу перейти к D-триггерам, из которых собственно и состоит 99% элементов состояния в ASIC и FPGA (остальной 1% идёт на D-защелки для экономии энергопотребления и особых случаев latch array и time borrowing которые первые 10 карьеры юному инженеру не понадобятся).

А вот с D-триггером нужно расписать детали timing analysis - его фронты, skew, slew (задержку изменения фронта), clk-to-q, setup, hold, метастабильности кратко итд).

Реальные временные характеристики разумеется необходимы и в Харрисах описаны (propagation delay, contamination delay, clk-to-q... ) В разделе "временная дисциплина".

Если слишком долго задерживаться на тайминге rs, t-триггерах и jk, то не останется времени семестра для конвейеров, контроля потока данных, очередей - и получится индивидуал, который сможет говорить , но не сможет работать в современных условиях, когда многие вещи абстрагированы с помощью использования библиотек стандартных ячеек (ASIC standard cell library) и автоматического статического анализа тайминга схем из d-триггеров и облаков комбинационной логики

lws0954 Автор

22.11.2023 16:09+2Не надо долго. Надо правильно. Тут вскрикнули - триггер не генерит! Да, реальный не генерит. А почему, если формально он может генерить? А известно ли "студенту", что при переключении триггер обязательно перейдет через запрещенное состояние? Что нужно делать, чтобы эта помеха не привела к сбою. Все это можно объяснить просто, доходчиво и времени займет совсем немного. Но тогда "студент" не будет "голосить" - триггер ни когда не генерит! Генерит и еще как :)

Студента пока он студент надо учить. Учить думать. А не тупо его точить, как карандаш под конкретную тему для конкретных фирм. Кто умеет думать и "правильные книжки в детстве читал" быстро разберется с любой темой. Не надо только кричать - времени нет, денег нет, конкуренты душат! Мы под эти крики развалили всю нашу науку. А за наукой и практику. Но зато научились точить студентов для западных фирм. Тираж книжки, которую я купил - 40000 экз. Предыдущий вариант - еще 41000. А какой тираж у книги Х&X?

YuriPanchul

22.11.2023 16:09+2Сразу после того, как русский перевод X&X выложили на сайт Imagination Technologies в 2015 году, ее только официально с регистрациями скачали 10 тысяч человек. Реальная цифра гораздо больше, потому что в первые два дня регистрация была с глюком (из-за чего надо было регистрироваться два раза), после чего люди стали качать не с сайта Imagination, а с пиратских сайтов, которых уже в первый месяц было больше 30 сайтов (британский менеджер Imagination спрашивал у меня нельзя ли им разослать емейлы чтобы убрали, я ему объяснил что в России это не работает).

*** А известно ли "студенту", что при переключении триггер обязательно перейдет через запрещенное состояние? ***

Запрещенный уровень упомянут еще первой главе, и при описании работы D-триггера указывается, что он переключается не мгновенно, есть clock-to-q.

*** Что нужно делать, чтобы эта помеха не привела к сбою. ***

Это гарантируется конструкцией ячейки standard cell library, на которые отображаются логические D-триггеры во время синтеза. Метастабильность может прийти только из двух источников: 1) внешние сигналы (это есть в X&X)

2) пересечение тактового домена (этого в X&X нет, но это более продвинутая тема, которую стоит рассмотреть уже после того, как студент существенно набьет руку на схемах с одним тактовым сигналом).

*** Кто умеет думать и "правильные книжки в детстве читал" быстро разберется с любой темой. ***

Что значить "быстро разобраться"? По-хорошему даже со студентом олимпиадного типа надо разбирать конвейеры, очереди, многобанковые памяти, арбитры и другие микроархитектурные темы месяцы. Причем сам он будет косячить - например делать дизайн с половинной пропускной способностью, потому что будет интуитивно думать, что в скажем в AXI stream сигнал ready возникает в ответ на valid.

*** Но зато научились точить студентов для западных фирм ***

Требования к инженерам обсуждаемых позиций (а значит и студентам) в российских компаниях Syntacore / Ядро, Байкал Электроникс, НПО Элвис, КМ211, МЦСТ, НИИСИ и других - не отличаются от требований к инженерам на таких же позициях в Apple, Samsung, NVidia, AMD итд. Они используют один и тот же синтез от Synopsys, Cadence, Xilinx, Altera, а в открытых проектах Open Lane.

lws0954 Автор

22.11.2023 16:09Даже Вы меня не поняли, Юрий. А что тогда говорить о студентах? Речь совсем о другом "запрете". У триггера два выхода - прямой и обратный. И почти нигде не доводят, что при переключении из одного устойчивого состояние в другое на его выходах появляет кратковременно запретная комбинация - 1-1 (для триггера на И-НЕ) или 0-0 (для триггера на ИЛИ-НЕ). Кстати в Х&Х об этом тоже кажется ни слова?

У D-триггера мы смотрим только на один выход и этого запретного для RS-триггера состояния мы не видим.Т.е. проблема будет, если мы напрямую в схеме используем RS-триггер и оба его выхода.

И при переключении D-триггера, как его реакция на изменение входного сигнала, будет просто задержка на выходе, а не та "болтанка", которую, как понял, изобразили в книге, назвав ее метастабильностью. Это другое.

YuriPanchul

22.11.2023 16:09+1Понятно. Так как эти вещи все равно устаканиваются в течение такта, то к моменту апертуры записи в следующий D-триггер будет чистое значение. Если мы конечно используем стандартную методологию - использование RS-триггеров в нее не входит.

Для расжевывания таких эффектов есть более сфокусированые на физических эффектах книги, например https://www.amazon.com/CMOS-VLSI-Design-Perspective-Hardcover/dp/B011DAYZTC CMOS VLSI Design: A Circuits and Systems Perspective 4th edition by Weste, Neil, Harris, David (2010)

Про нее тоже была идея ее перевести, но у нее меньше возможный рынок.

YuriPanchul

22.11.2023 16:09+2Вячеслав, я в 2014 году начал эту тему с переводом Харрис & Харрис. Я заметил вашу статью пять минут назад, пока ждал Юбер, и мне ваш текст понравился (я его перечитаю внимательно). Но пока я еду в юбере, два кратких пояснения:

1.Харрис & Харрис - это вводный курс, если студент изучит только его, он интервью в крупную электронную компанию (Apple, NVidia, Samsung итд) не пройдет. Но не потому что он не знает деталей SR-защелки (это для реальной работы по ASIC дизайну чипа в телефоне не нужно), а потому что не знает FIFO и арбитров, которые в Харрисах не рассматриваются, но которые мы спрашиваем на интервью в Самсунге, как и другие электронные компании.

2. У меня только что вышла статья в https://fpga-systems.ru/fsm : Панчул Юрий. "Что умеют и не умеют писать на SystemVerilog для ASIC и FPGA американские студенты?" В ней более фундаментальные проблемы образования, чем то, что пишете вы. Студенты не умеют решать микроархитектурные задачки, и Х&Х им в этом не поможет.

checkpoint

22.11.2023 16:09Юрий, я зашел на этот горе журнал в поисках Вашей стетьи - там кроме заголовков ничего нет. Где статья ? Несите её к нам сюда скорей!

mc2

22.11.2023 16:09Там написано: "Скачать: релиз состоится 20-30 ноября 2023 "

checkpoint

22.11.2023 16:09Понятно, а я то губу раскатал, пошел уже было чай заваривать перед чтением статьи. :)

lws0954 Автор

22.11.2023 16:09+2Студенты не умеют решать микроархитектурные задачки, и Х&Х им в этом не поможет.

Студент и не должен уметь решать все. Но он должен иметь базовое образование, которое затем ему поможет решать все и разобраться во всем. И главное поможет общаться с другими на общем и понятном им языке.

Вводный курс должен вводить студента в это самое базовое образование. А он в H&H видит пример на базе автоматной модели, но при этом ему не дают формального определения автомата. Дело доходит до того в книге граф автомата обзвали таблицей переходов. Может, правда, это опечатка? Но если специалист подобное пропускает, то ... куда он заведет студента? Правда потом называют диаграммой переходов. В правильных же книгах дают сначала определение автомата, потом рассматривают формы его описания - таблица, граф, матрица и т.д. Чтобы все это понять не нужно сверхзнаний. Это и есть вводный курс. В автоматы. А уж потом примеры - светофор и т.п.

В целом же подобный вводный курс (как бы выразиться помягче) все равно, что заниматься алгеброй, не освоив при этом арифметики... Это не значит, что в целом книга такая. Но некоторые ляпы явно "режут глаза".

checkpoint

22.11.2023 16:09Вы случайно не попутали два совершенно разных курса "теория формальных языков, грамматик и автоматов" и "цифровая схемотехника" ? Первый - сугубо териотический, больше с упором на академическую науку (пища для докторов и их аспирантов). Второй - чисто практический, для разработчиков.

lws0954 Автор

22.11.2023 16:09Нет не попутал. Глушков, Баранов, Мелихов и особенно Майоров и Новиков тд. и т.п. - это все про синтез цифровых схем. Или Вам эти авторы не известны? Формальные языки - совсем другая тема.

checkpoint

22.11.2023 16:09+2Нет конечно, на кой мне этот шлак в голове, хватило ТФЯ в вузе. Но ради интереса я загуглил:

В. М. Глушков. "Синтех цифровых автоматов", физматиз. 1962.

Учитывая, что вся теория по синтезу была создана в 80-х с приходом программируемых матриц и изобретением HDL, мне даже стало любопытно о чем там мог писать товарищ Глушков в 1962 году. Я выкачал PDF и немного полистал. Короче, это теория абстрактных автоматов, причем книга написана в лучших советских традициях - куча формул без обьяснения назначения переменных, читать и воспринимать информацию крайне тяжело, более сложного и запутанного обьяснения атоматам Мура и Мили найти невозможно. Практическая ценность этих трудов - собирать пыль в музее.

checkpoint

22.11.2023 16:09+3Честно говоря, не совсем понимаю в чём состоят претензии автора статьи к материалу H&H. Особенно не понимаю пассаж про фронты сигналов. Ведь фронты это весьма важная часть даташитов на цифровые микросхемы, и если разработчик живет в своём сферическом вакууме где есть только "0" и "1" (т.е. игнорирует Tsetup и Thold), то гнать таких в шею.

Книгу H&H я прочитал по совету Юрия Панчула и у меня к ней есть своя претензия. Состоит она в том, что в книге не описаны базовые структуры которыми оперирует современный разработчик, как то: PLL, FIFO, сдвиговые регистры и конвейеры. Так же в книге нет ни слова про тактовые домены и проблемы связанные с переходами между ними. Редкое современное изделие (я имею в виду СБИС или изделие на ПЛИС) обходится без таких вещей. И да, в дедовские времена всего этого не было и в советских вузах не преподавалось никогда. Так, что тезис "в цифровой схемотехнике нет ничего нового" тоже очень сомнителен.

Тем не менее, книга Харрисов годная! Материал в ней подан пусть и кратко, но доходчиво, с примерами и заданиями. И иллюстрации очень даже правильные - с фронтами! Особенно книга полезна для программистов, которые хотят хоть на чуток вникнуть в происходящее под капотом их гоночного боллида.

PS: Простите мне моё невежество, но что такое "моделирование ВКПа" ?

lws0954 Автор

22.11.2023 16:09-5Честно говоря, не совсем понимаю в чём состоят претензии автора статьи к материалу H&H.

Это нормально. Не все доходит с первого раза. Перечитайте и, возможно, понимание придет.

А по ВКПа см. в списке литературы [5].

checkpoint

22.11.2023 16:09+6В [5] находится ссылка на Вашу же статью, но про другое. В той статье термин ВКПа упоминается почти в самом её конце и толком не разьясняется. Но я догадался, что это какая-то среда визуального программирования FSM (конечных автоматов), а вся Ваша та статья про то, что программирование FSM нуждается в еще одном универсальном языке программирования (тушите свет!). От прочтения Ваших статей у меня возникло ощущение, что Вы слишком долго засиделись в академической среде и Вам срочно требуется свежий воздух.

Ну и коментарий к той статье, дух которого я полностью разделяю:

Понятно. Если применяется только в ваших игрушках, то к чему этот высокий штиль и академический формализм?! Ощущение от вашей статьи такое, как будто читаешь нормативно-правовой акт: хочется по-быстрее закрыть, чтобы не сойти с ума. Если хотите разжечь интерес к теории автоматов и практике, нужно проще излагать для широкой публики.

PS: Гипертекст придумали в том числе и для того, чтобы не морочить читателю голову длинным списком литературы. При чтении Вашей статьи я замаялся крутить ролик у мышки постоянно бегая в список и обратно.

andy_p

22.11.2023 16:09Действительно, - генерит.

Нет, RS триггер не генерит.

lws0954 Автор

22.11.2023 16:09Зря Вы так резко ;) Не верите мне - найдите хотя бы книжку Фрике К. Вводный курс цифровой электроники. Может он Вас переубедит. Такие вещи надо знать и понимать.

andy_p

22.11.2023 16:09+2Я не читал книгу уважаемого Фрике К., но знаю, что, например RS триггер, созданный на элементах И-НЕ при подаче входных сигналов 1-1 будет сохранять предыдущее состояние, а при подаче на вход сигналов 0-0 на выходе даст 1-1 и никакой генерации не будет.

checkpoint

22.11.2023 16:09+2Забавно то, что автор статьи сначала пытается доказать, что переходные процессы в цифровых схема (фронты) это все туфта и их не нужно учитывать совсем. А потом вдруг вспоминает, что при определенных условиях и бистабильная ячейка - не ячейка, а генератор. Кино и немцы. :)

TaGUNil

22.11.2023 16:09+2Мне кажется, что интересы автора лежат в области построения тех самых формальных автоматных моделей, в которых переходные процессы, присущие моделируемой системе, предлагается представлять в виде задержек (пример с RS-триггером), а вопросы физической реализации модели автора интересуют постольку-поскольку.

lws0954 Автор

22.11.2023 16:09А Вы знаете, что переключении триггер переходит обязательно через запрещенное состояние? А это источник помех в схеме..

lws0954 Автор

22.11.2023 16:09А Вы почитайте. Не помешает. Особенно обратите на комбинацию, когда после 0-0 на входы подается 1-1. Такая последовательность и провоцирует генерацию.

YuriPanchul

22.11.2023 16:09+2Что касается D-защелок / D-latch, то из педагогических соображений их стоит в вводном курсе вообще объявить ошибкой и просто объяснить как их избегать (не писать 'always_comb if (a) b = c" что порождает D-защелку, а всегда внутри always_comb или ставить 'b = d; if (a) b = c", или ставить 'if (a) b = c; else b = d".

По-хорошему, их стоит вводить при объяснении экономии динамического энергопотребления в контексте конструкции для генерации gated clock, уже после того, как студенты усвоят, как проектировать не только конечные автоматы и конвейеры, но и простые процессорные ядра.

То есть это следующая стадия, когда базовая методология проектирования с помощью d-триггеров и комбинационной логики у них в голове уже устаканится.

Если же вводить ее рано, то они эти D-защелки просто забудут (то есть бессмысленная трата времени семестра) или у них образуется каша в голове и им будет труднее усваивать те же конвейеры и другой непосредственно полезный материал.

Особые случаи использования защёлок (time borrowing, latch arrays вообще имхо должны быть вне базовой вузовской программы, так как они используются очень редко, но сбить фокус могут конкретно

YuriPanchul

22.11.2023 16:09+4Прочитал весь текст. Сухой остаток: если смотреть с позиции максимально эффективно натренировать молодого инженера для трудоустройства в ASIC или FPGA, то по моему мнению:

Бистабильные элементы и циклические генераторы можно пропустить.

D-защелки перенести в более продвинутый курс, где будет объяснение экономии динамического энергопотребления с помощью latch-and-gate примитива который генерит тактовый сигнал только когда блок чем-то занят. В вводном курсе про D-защелки говорить только как их избегать.

Метастабильности рассматривать только для D-триггера, сообщить как устранять метастабильность для сигнала из внешнего мира (пропуская его через два или три D-триггера ), показать формулу матожидания времени сбоя, потом вспомнить снова в курсе после вводного, когда речь зайдет о пересечении тактового домена.

Об rs-триггерах сказать вскользь в порядке научпопа.

Объяснить как работает алгоритм статического анализа тайминга

Упомянуть время фронта тактового сигнала (slew) в дополнение к задержке из-за разницы распространения тактового сигнала (skew).

Про inertial и transport delay можно объяснить факультативно, по статье о моделирования из от Cliff Cummings

sci_nov

22.11.2023 16:09+1Тренировать молодого инженера надо на предприятии. Там должна быть своя школа. В учебном заведении нереально натренировать практическим вещам, я бы сказал априори.

checkpoint

22.11.2023 16:09-1В современном мире на предприятии тренировать студентов некогда и некому - люди знающие и имеющие опыт заняты делом, любое отвлечение их от производственного процесса чревато проигрышем в жесткой конкурентной среде. Но многие крупные предприятия так и делают - строят свои учебные центры. Вопрос в том, что делать нам, тут и сейчас в условиях когда нет ни преподавателей, ни опытных наставников, а у выпускника в голове из арсенала в лучшем случае Булева алгебра и теория автоматов.

YuriPanchul

22.11.2023 16:09Тогда чем они занимаются в вузе? Учат только совсем какие-то простые вещи типа как спроектировать мультиплексор + случшают научпоп о сложном? Или полгода рассусоливают математику вычисления MTBF (среднестатистического времени между сбоями), при том, что про это две строчки в тысячестаничной спецификации на GPU?

Что за фигня, когда студентка-отличница у меня на интервью может поговорить словами про алгоритм Томасуло (структуру для конвейера суперскалярных процессоров), но ставится в тупик вопросом построить статический конвейер для вычисления формулы √(a + √b), если у нее есть в качестве черного ящика конвейерный подмодуль для вычисления квадратного корня. Почему они слышали про сдвиговые регистры и FIFO, но не знают зачем это нужно и все пытаются конечным автоматом делать?

Простым вещам можно научить за два месяца, а научпоп можно в отпуске на пляже читать. Что они делают остальные 4-5-6 лет?

Слава богу, бывают студенты, которые делают в вузе самостоятельные проекты, а также более качественные преподаватели, в штатах - в MIT на курсе 6.111, который уже много лет хороший а в России - МИЭТ, которые это улучшают с другими на Школе Синтеза Цифровых Схем.

sci_nov

22.11.2023 16:09+1Не важно чем занимаются, специфика возраста студента не позволит выйти в вузе на производственный уровень: этот уровень просто-напросто отфильтруется мозгом как что-то чужеродное. К производству надо привыкать, причем очень постепенно.

По моим ощущениям, отучись я сейчас в радиотехническом вузе по второму кругу, я бы по другому воспринимал ту же, например, схемотехнику, электронику или антенны и РРВ. Хотя мат. анализ, вероятно, пропускал бы либо ходил для галочки, потому что во время обучения у меня был перекос в математику. Опыт приходит с годами, и правы те, кто говорят что развитие идет по спирали. Кстати, то, что в советское время учились в вузах после армии, это было очень хорошо.

Теперешних выпускников вообще надо брать без особых собеседований: хочет работать, так надо с радостью брать и натаскивать специфическим вещам. Я помню как у меня спросили что-то типа ветровой нагрузки на параболические антенны... сейчас смешно, а тогда и не знал что ответить. Сотрудники компаний как бы витают в своих облаках, студенты - в своих и область пересечения довольно-таки мала. В вузах учимся 5 лет, в компаниях - всю оставшуюся жизнь :)

Да, конечно, есть студенты исключения, своего рода таланты. К преподавателям вузов (по крайней мере к взрослым и состоявшимся) я претензий не имею вообще - глядя ретроспективно понимаешь, что всё было очень даже ничего.

YuriPanchul

22.11.2023 16:09+1*** Теперешних выпускников вообще надо брать без особых собеседований ***

Даже если брать бесплатных интернов, то для получения от них толка нужно прикрепить к ним старшего инженера, который был их учил. И учить с нуля многим областям просто долго, а интерны - явление временное.

Что касается не интернов, а инженеров на джуниор позиции, то тут есть очевидное ограничение - деньги. Ему сразу надо платить более 10 тысяч долларов в месяц в американских условиях. Если он не знает ничего из того, что нужно для работы, и его учить год, то потом он просто уйдет на лучших условиях в другую компанию, где его уже ничему будет учить не нужно. Итого - компания теряет сто-двести тысяч долларов (вместе с бенефитами), время старших инженеров, и мало того что не получает ничего, так еще и не было возможности интервьировать других людей.

Держать богадельню на 100 человек на зарплатах, из которых какой-то толк будет от 10 и только 1 станет суперстар? С учителями для них из старших инженеров? Это очень неэффективно, лучше повысить эффективность вузовских программ, в которые включить обязательный опыт участия в открытых проектах, по которым видно способности человека.

sci_nov

22.11.2023 16:09Да, ваша правда... Но 10 тысяч на джуниора по мне это слишком)

YuriPanchul

22.11.2023 16:09У него в нашей местности уйдет сразу 3000 на налоги и еще 3000 на съемную квартиру

lws0954 Автор

22.11.2023 16:09Тогда чем они занимаются в вузе?

Признаюсь, что в нынешнее время и для меня это загадка ;)

Почему они слышали про сдвиговые регистры и FIFO, но не знают зачем это нужно и все пытаются конечным автоматом делать?

Вот тут тоже есть вопросы, а, может, и проблема. Я тоже слышал и про сдвиговын регистры и FIFO, но, чесслово, не могу представить, как бы я алгоритмы выражал через эти понятия. Вот с автоматами - проблем нет совсем. Нет, конечно, в каждой области есть своя специфика, но как-то я не могу представить синтез цифровых схем совсем без автоматов. Да и Х&Х им много внимания уделяют. Если бы не они (автоматы то есть) я бы и читать ее не начал.

Вы, Юрий, много внимания уделяете этим вещам, но к автоматам, как мне кажется, у Вас негативное что-то проскакивает :(

Еще раз. Нет, конечно, можно гипотетически представить, что можно алгоритмы выражать, используя FIFO и что-то еще. Но я проектированием процессоров не занимаюсь, я их использую, создавая алгоритмы. И тут без автоматов уже мне не прожить, а без FIFO - на раз :) Может, устарел, а, может, чего-то не понимаю... :(

Вот и сейчас, кровь из носу, мне очень бы хотелось увидеть автомат для упражнения 3.29 из книги и диаграмму. Вот какую бы студенку привлечь, чтобы помогла? Просто автомат и просто диаграмму. А потом уж думать, как приладить сюда сдвиговый регистр или FIFO. Хотя мне просто автомата - за глаза. Как той Вашей студентке. Тут я скорее на ее стороне.

Да, кстати. У меня был когда опыт написания конвейерной сортировки. Даже статья в журнале была на эту тему. Там же - сортировка на базе философов Дейкстры. Веселый был эксперимент, интересные результаты... ;) Давно только это было :(

Да, еще. А Школе Синтеза пользуются трудами Баранова С.И., Майоров-Новиков (Глушков или Мелихов, может, действительно будут чуть сложноваты для "школяров") или чем-то аналогичным? Но нашим - советским, российским. Или все это за пределами Школы?

YuriPanchul

22.11.2023 16:09С автоматом тут все банально. Они конечно применяются на каждом шагу, но если бы сделать весь дизайн только на конечных автоматах, без конвейерной обработки, то пропускная способность была бы в тысячу раз медленнее. Вместо того, чтобы роутер принимал бы смесь из трансферов кучи пакетов и обрабатывал бы их комбинацией конвейеров и FIFO, он бы их брал по одному и медленно ссначала брал один трансфер, потом другой, и только после окончания брал бы другой пакет. Это чисто как на конвейере автомобильного завода - новая машина сходила бы не каждые несколько минут, а каждые несколько дней.

То же самое с компьютерной графикой - в шутерах монстры отрисовывались бы медленно и печально.

Конечно конечные автоматы применяются - например если треугольник не влазит в экран и при этом большой, что его долго растеризовать и нельзя выбросить, то для этого есть несколько параллельно работающих конечных автоматов, которые его порежут, посчитают новые координаты осколков итд. Но это случается раз в тысячу треугольников.

То же самое что и сетевыми пакетами - большинство простых пакетов нужно обработать целой группой, но иногда бывает что-то нетривиальное, что нужно отдать большому конечному автомату или процессору.

На этом построены все современные дизайны, как скажем в 1970-е годы был широко распостранен микрокод (который, как выяснилось в 1980е, трудно конвейеризировать)

Про упражнение посмотрю потом

lws0954 Автор

22.11.2023 16:09Юрий, получил уведомление о Вашем ответе на почту, но почему-то его нет здесь. Ни моего коммента, ни Вашего ответа к нему. Дикий какой-то случай. Первый раз с подобным сталкиваюсь.

Написал Вам в личку, но хочу подстраховаться и здесь. Ясно, что Вы покритиковали мою диаграмму и предложили свое решение. Но в автомат на Верилоге мне сложно вникнуть, да и наглядность не та. Хотелось бы попроще и понагляднее, чтобы избежать путаницы. Пусть это будет даже не граф автомата (но это был бы идеальный вариант), но хотя бы в форме таблиц переходов/выходов (типа табл. 3.1 в книге). Кодирование состояний и выходов не нужно.

YuriPanchul

22.11.2023 16:09+1*** Я тоже слышал и про сдвиговын регистры и FIFO, но, чесслово, не могу представить, как бы я алгоритмы выражал через эти понятия. Вот с автоматами - проблем нет совсем. ***

Вот только что вышла моя статья в сборнике, там про конвейерные вычислители, правда самое начало этого. И про студентов:

https://fpga-systems.ru/fs_fsm/state_0/fsm_state_0.pdf

lws0954 Автор

22.11.2023 16:09+1Спасибо! Даже не вникая, а просто просмотрев материал, скажу одно - впечатлен!

На мой взгляд, именно подобные проекты должно обязательно поддерживать государство, а не просто, судя по последним заявлениям, вливая миллиарды в некие "генеративные нейронные сети". Хотя, как мне кажется, не факт, что и это произойдет, т.к. попахивает очередным "распилом" :(. У меня еще на памяти попытки создать "российскую операционку"...

Так что, еще раз большое спасибо за ссылку! Проштудирую обязательно :)

sci_nov

22.11.2023 16:09+1Спасибо, очень интересно. Я думаю это должно быть нормой в рамках курсового проектирования, тем более в топовых учебных заведениях.

gena_k

22.11.2023 16:09Можно также заметить, что любая схема из нечетного числа инверторов представляет собой генератор прямоугольных импульсов. В том числе состоящая из одного инвертора.

В только одном инверторе будет генерировать в инверторах с триггером Шмитта, но не будет генерировать в простых линейных инверторах на 2-х КМОП-транзисторах (561лн2 или 4049/4069ube).

Также могут генерировать буферизованные 4049b.

lws0954 Автор

22.11.2023 16:09Между прочим. На стр. 430 в книге прямоугольные (?) сигналы. У меня (я повторил схему) - тоже :)

Рис.4.1 (стр 430) в ВКПа

По ходу захотелось пройти собеседование и попытал на вскидку решить Упражнение 3.29 (стр. 409 в H&H). Привлек диаграммой сигналов. Быстренько набросал автомат и получил диаграмму.

Диаграмма для примера 3.29

Даже не знаю - прошел ли тест?... :) Может тоже кто-то попробует? Особенно из фанатов H&H. Хотелось бы увидеть и автомат, и диаграмму. Свой автомат пока не буду показывать. Но обещаю не изменять. Покажу при сравнении. Пока стесняюсь :) А вам - слабо?

YuriPanchul

22.11.2023 16:09Вы говорите про это задачу?

Ваша диаграмма не выглядит верной.

Значение A в такте 1 (выделено синим) равно 0.

Оно записывается в D-триггер в момент 1-красный, CLK меняется с 0 в 1.

Значение A в такте 2 переходит из 0 в 1. Момент перехода я отметил как 2-красный.

Значение B весь 1-й и 2-й такт равно 0.

Поэтому Z (выход автомата Мили) будет равен A1 & A2 = 0 & 1 = 0.

Z станет 1 только в третьем такте, когда A2 & A3 = 1 & 1 = 1

Здесь достаточно конечного автомата с двумя состояниями, который на верилоге описывается так:

module hh329 ( input clk, input rst, input a, input b, output z ); logic a_r; always_ff @ (posedge clk) if (rst) a_r <= '0; else a_r <= a; assign z = b ? a_r | a: a_r & a; endmoduleКоторый симулируется вот с такими диаграммами:

На вот таком тесте:

module testbench; logic clk, rst, a, b, z; hh329 dut (.*); initial begin clk = '0; forever # 500 clk = ~ clk; end initial begin $dumpvars; rst <= '1; @ (posedge clk); rst <= '0; a <= '0; b <= '0; @ (posedge clk); a <= '1; b <= '0; @ (posedge clk); a <= '1; b <= '0; @ (posedge clk); a <= '0; b <= '0; @ (posedge clk); a <= '0; b <= '1; @ (posedge clk); a <= '1; b <= '1; @ (posedge clk); a <= '1; b <= '1; @ (posedge clk); a <= '1; b <= '1; @ (posedge clk); $finish; end endmodule

GarryC

22.11.2023 16:09+4"Тогда такой автомат сможет повторить на выходе любой входной сигнал со сдвигом по времени" - не сможет, иначе проблема пересинхронизации не стояла бы так остро.

Интересно, как неприятие наклонных фронтов в книге Х&Х (кстати, в советское время часто именно так фронты изображали в справочниках и никого это не шокировало) согласуется с представленным ниже рисунком автора поста, где фронты по-прежнему (хотя и менее) наклонные?

-

А что касается генераторов на задержках вентилей (на нечетном количестве), равно как и задержкам на вентиле, то меня в МИЭТ 40 лет назад учили избегать подобных решений ввиду их нестабильности.

Резюмируя, не могу понять, что именно так возбудило автора поста - я Х&Х прочитал не без удовольствия, хотя не верю, что по этой книге можно реально проектировать процессоры.

lws0954 Автор

22.11.2023 16:09Чему Вас только там в МИЭТ учили? :)

Об этом даже Википедия знает. Наберите - теорема Котельникова...

У Вас острый глаз ;) Наклон сигнала зависит от скорости параллельного процесса, который отображает дискретные сигналы. Здесь это тоже автомат. Чем он медленнее, тем больше будет наклон. Но если сделать его очень быстрым, то графика будет нагружать среду.

-

Здесь больше интересует факт их наличия (работа в соотвествующем режиме - генерации). А так - Вам сказали правду.

Резюмирую. Освежите в памяти теорию автоматов, если Вам, конечно, ее преподавали. Может был синтез цифровых/микропрограммных автоматов или что-то подобное (все-таки МИЭТ). Может, тогда поймете.

Да. Книгу Вы прочли. Может попробуете Упражнение 3.29? Было бы интересно: сможет ли, судя по всему, опытный инженер МИЭТ нарисовать автомат по выданному заданию на его проектирование?

GarryC

22.11.2023 16:09Меня в МИЭТ в первую очередь учили правильно применять теоремы.

В данном конкретном случае это означает (и это наверняка написано в Википедии), что теорема Котельникова говорит о входном сигнале с ограниченным спектром, который подвергается дискретизации по времени. Совершенно очевидно, что прямоугольный сигнал (любой частоты) имеет бесконечный спектр и поэтому субъектом вышеуказанной теоремы не является. Соответственно, он не может быть восстановлен без потерь при конечной частоте дискретизации (и даже со сдвигом).Ответ не зачтен - либо Вы категорический противник наклонов на фронтах и тогда с этим злом следует бороться, невзирая на нагрузки, либо их наличие не является существенным обстоятельством и тогда не следует упоминать их в качестве критикуемых недостатков книги - определяйтесь (или крестик или ...).

То есть мы оба понимаем, что делать такие генераторы на практике нельзя, несмотря на чисто теоретическую возможность подобной реализации (что не есть факт) - меня это устраивает.

Честно говоря не понял, что же там такого страшного в 3.29, пойду посмотрю.

ovn83

22.11.2023 16:09+1Книга замечательная, 2 года ВУЗа, несколько предметов, ужали в книгу, жаль, что 20 лет назад её не было.

MAXH0

К сожалению общий уровень технического образования со времен СССР снизился. Вот на таких примерах это видно объективно...

YuriPanchul

Х&Х - это вводный курс, он не претендует на доведение студента до трудоустройства на RTL-дизайнера (см. более подробный коммент ниже).

А что касается СССР, то советские учебники цифровой электроники не разбирали конвейеры и FIFO, поэтому даже если их вызубрить и доучить синтаксис верилога, работать в группе проектирования современного процессора, GPU или сетевого чипа студент не сможет. И знание SR-зашелки ему никак на интервью не поможет.

SIISII

И конвейеры, и FIFO я встречал именно в советской литературе -- только за давностью лет уже не скажу, в какой. Плюс, более-менее устройство конвейерного проца расписано, по меньшей мере, применительно к ЕС-1050/1052, о чём надеюсь как-нибудь написать серию статеек -- но это уже не учебник, конечно, был.

YuriPanchul

Именно - это не был учебник. То, что я видел в советской литературе, был научпоп о конвейерах, объяснить словами, но не показать как делать руками. Учебники в лучшем случае заканчивались на конечных автоматах и последовательных процессорах (на основе схематики, синтез был изобретен только в 1988 году), после чего шел разрыв и в учебнике говорили о программировании (не проектировании) процессоров типа 8080.

Кроме этого, конвейер - это гораздо более общая концепция, чем конвейер в execution unit процессора. Например, в сетевых устройствах пакеты обрабатываются конвейерами, которые принимают их трансферы. В GPU по конвейерам блоков фиксированных функций идут сначала треугольники с координатам, а потом фрагменты (это в дополнение к конвейерам шейдеров). Конвейеры используются вместе с контролем потока данных с помощью двойной буферизации (skid buffer) и кредитными счетчиками итд - короче там целая кухня.

Если эту кухню в вузе не учить, а выпускать только студентов, которые умеют построить конечный автомат, их придется учить на рабочем месте, в условиях жестких графиков на выход массовых чипов и занятости старших инженеров. То, что они разобрались в RS-триггерах и timing violations в защелках, никак этому не поможет, так как RS-триггер перед ними не появится, а в реальных static timing analysis reports, которые они будут разбирать, будут критические пути между D-триггерами, составляющими конвейер, которы они так и не научились строить.

iggr63

Похоже, особенно если это касается современных технологий и их практического применения. У меня сын съездил в Зеленоград, на один семестр по Верилогу, оказался единственным из группы который смог сдать работающую на ПЛИС курсовую.