Серия статей Дмитрия Руднева (эта и др.) натолкнула меня на мысль написать заметку о реальном использовании простых микросхем 155-й серии в отечественных вычислительных машинах начала 1970-х годов — в первую очередь, ЕС-1020 (1971 год), по которой имеется довольно подробная литература.

Практически вся логическая часть процессора этой машины, как и создаваемой одновременно с ней более мощной ЕС-1030, была построена всего на девяти типах только-только освоенных производством микросхем 155-й серии, в те годы (первая половина 1970-х) носивших обозначения К1ЛБ551, К1ЛБ552, К1ЛБ553, К1ЛБ554, К1ЛБ556, К1ЛБ557, К1ЛР551, К1ЛР553 и К1ЛП551. В 1975-м году была принята новая система обозначений, используемая с некоторыми расширениями и доработками до сих пор; перечисленным старым обозначениям соответствуют К155ЛА1, ЛА2, ЛА3, ЛА4, ЛА6, ЛА7, ЛР1, ЛР3 и ЛД1. В дальнейшем я буду использовать только привычные новые обозначения, для краткости опуская обозначение серии.

Триггеры

Как нетрудно заметить, среди доступных на тот момент разработчикам микросхем нет ни одного запоминающего элемента; между тем, даже в самом простом компьютере не обойтись не только без оперативной памяти (которая в те годы строилась исключительно на ферритовых сердечниках), но и без регистров и триггеров: нужно же как-то хранить состояние процессора, чтобы управлять его работой, и данные, над которыми выполняются операции. В зависимости от потребностей из логических элементов собиралось несколько разновидностей триггеров.

RS-триггеры и полярность входных сигналов

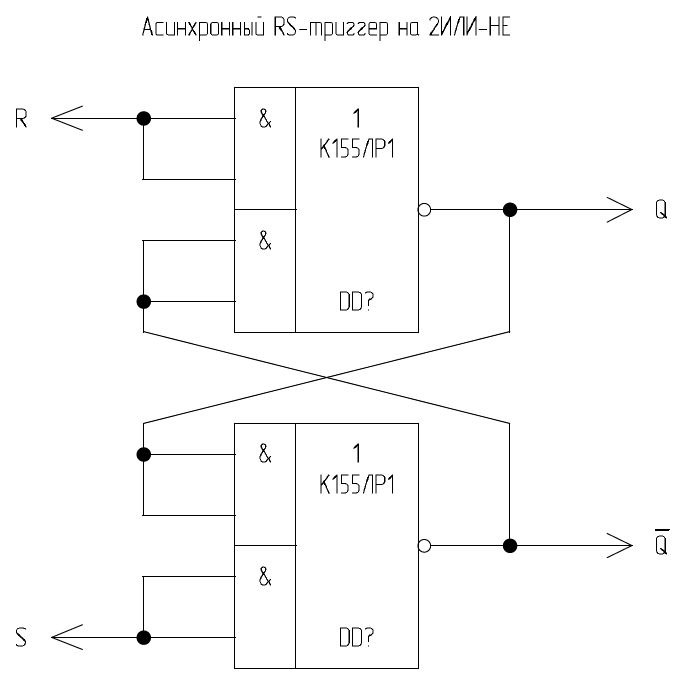

Простейший асинхронный RS-триггер, описанный в упомянутых выше статьях, состоит из двух элементов 2И-НЕ, т. е. из половины микросхемы ЛА3, в состав которой входит четыре таких элемента. Отличительной особенностью этого триггера является использование инвертированных входных сигналов: переключение состояния происходит, когда на один из входов подаётся низкий уровень (логический нуль), а при подаче на оба входа высокого уровня (единицы) триггер сохраняет своё состояние.

Иногда желательно, чтобы активным уровнем сигнала был высокий; соответственно, требуется триггер с неинвертированными входами. Самым очевидным и прямолинейным решением было бы добавить инверторы к инвертированным входам RS-триггера. Один инвертор можно получить из элемента И-НЕ с любым числом входов, просто объединив входы между собой; соответственно, на одной микросхеме ЛА3 можно построить либо два RS-триггера с инвертированными входами, либо один с неинвертированными. Однако наличие инверторов увеличивает время переключения триггера: сигналу требуется пройти ещё один уровень логики. Довольно часто такие дополнительные «тормоза» роли не играют, но, очевидно, бывают случаи, когда лишние задержки нежелательны. В этом случае можно было бы собрать RS-триггер из двух элементов 2ИЛИ-НЕ, однако на тот момент соответствующие микросхемы (ЛЕ1) ещё не производились, поэтому в роли элементов 2И-НЕ использовались элементы 2,2И-2ИЛИ-НЕ (ЛР1), у которых оба входа каждого из элементов И объединены. Заметим, что оба способа реализации RS-триггера с неинвертирующими входами требуют одинакового числа корпусов микросхем (одна штука; в ЛР1 имеется два элемента).

Несколько управляющих сигналов

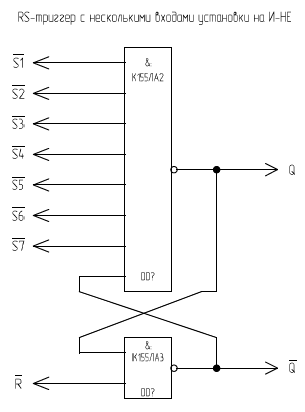

Иногда триггер должен устанавливаться или сбрасываться не единственным сигналом, а одним из нескольких альтернативных, т. е. должен иметь несколько входов сброса и/или установки. Несколько сигналов можно объединить в один, поступающий на триггер, с помощью дополнительных элементов; если используется уже готовая микросхема триггера, почти всегда так и приходится делать (и увеличивать время задержки за счёт лишних слоёв логики). Однако, собирая триггер из логических элементов, имеется и другой путь: вместо элементов 2И-НЕ можно применять элементы с большим числом входов. Например, соединив вместе элемент 8И-НЕ (ЛА2) и 2И-НЕ, можно получить триггер, переводимый в одно из состояний только одним сигналом, а в другое — любым из семи.

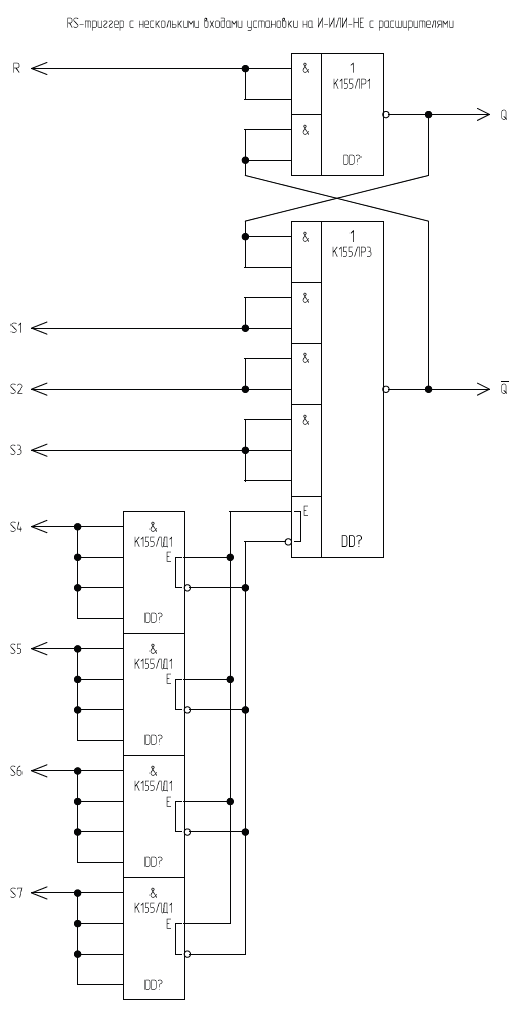

В случае триггера с неинвертированными входами аналогичный эффект, очевидно, достигается использованием элементов 2,2,2,3И-4ИЛИ-НЕ (ЛР3): каждый элемент позволяет организовать три управляющих входа. Однако имеется и альтернативный, более экзотический вариант, позволяющий ещё больше увеличить число входов: применение микросхемы расширителя ЛД1. Она может быть подключена как к единственному элементу микросхемы ЛР3, так и к одному из двух элементов ЛР1 (второй элемент не имеет входов расширения). По своей логической сути расширитель — это дополнительный элемент 4И, подключаемый к элементу ИЛИ-НЕ внутри ЛР1 или ЛР3 (на схемотехническом уровне это, однако, не готовый логический элемент, а лишь его входной каскад, сравните схемы элементов ЛР1 и ЛД1). Если бы транзисторы и соединительные линии были идеальными, расширитель позволял бы неограниченно увеличивать число входов элемента ИЛИ-НЕ, однако реальность куда более сурова, поэтому максимальное количество элементов расширения, подключаемых к одному базовому элементу ЛР1 или ЛР3, ограничено, если не изменяет память, восемью.

Управление управлением

Использование для построения RS-триггера элементов И-ИЛИ-НЕ вместо И-НЕ даёт возможность бесплатно (без дополнительных элементов) расширить возможности управления триггером: поскольку сигнал сброса или установки поступает на элемент ИЛИ-НЕ не прямо, а через «встроенный» элемент 2И (либо 4И, если используется ЛД1), остальные входы элемента И можно не соединять с первым, «упраздняя» тем самым элемент И как таковой, а использовать их для разрешения или блокирования действия управляющего сигнала (если на втором входе удерживается логический нуль, состояние первого входа будет безразличным). Для триггеров на базе элементов И-НЕ потребуются дополнительные элементы, что влечёт увеличение времени срабатывания и, к тому же, превратит управляющие входы в неинвертирующие. Оба способа реализации триггеров со входом разрешения позволяют легко реализовать наряду с синхронными (блокируемыми сигналом разрешения) и асинхронные сигналы сброса и установки, причём последние будут инвертированными независимо от того, на каких элементах построен триггер.

Пара реально применявшихся вариантов так называемых тактируемых RS-триггеров приведена на рисунке. Вход разрешения в этих схемах имеет активный высокий уровень и управляет обоими прямыми входами сброса и установки, но при необходимости для них можно использовать отдельные входы разрешения. Заметим, что вход разрешения обозначен, по тогдашней традиции, как C — и это может сбивать с толку более молодых читателей, привыкших видеть такое обозначение (или обозначение CLK) для тактовых сигналов, действующих своим фронтом, а не уровнем (вообще, система синхронизации старых машин почти всегда сильно отличается от применяемой сейчас — и не без веских причин).

D-триггеры

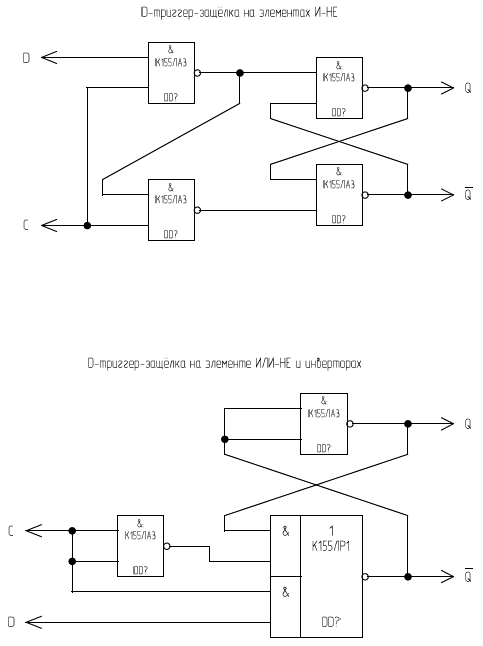

RS-триггеры весьма широко используются для хранения состояний и управляющей информации, однако для хранения обычных данных не всегда неудобны, поскольку для установки и сброса RS-триггера используются разные сигналы. Эта проблема решается с помощью D-триггеров типа «защёлка» (latch по-английски). При активном значении синхросигнала C такой триггер передаёт на свои выходы состояние входа данных D (т. е., если состояние линии D меняется при активном уровне на C, состояния выходов триггера тоже меняются), а при переходе синхросигнала в неактивное состояние происходит «защёлкивание» установленной в этот момент на линии данных информации. Схемотехнически такой триггер обычно собирается либо из четырёх элементов 2И-НЕ, либо из одного элемента 2,2И-2ИЛИ-НЕ и пары инверторов, в свою очередь, собранных, как правило, из элементов 2И-НЕ. По расходу места на печатной плате оба варианта потенциально равнозначны (половина микросхемы ЛР1 и половина ЛА3 против одной целой микросхемы ЛА3).

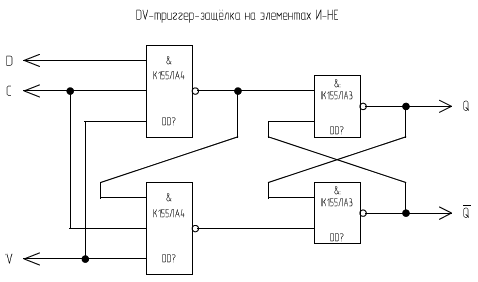

DV-триггеры

Название «DV-триггер» встречается нечасто, хотя в 1970-х в отечественной литературе оно было весьма популярно. За ним скрывается обычный триггер-защёлка, имеющий дополнительный вход V, разрешающий изменение его состояния. По сути, вход разрешения V ничем не отличается от тактового входа C: изменение состояния триггера происходит, когда оба этих входа активны. Схемотехнически такой триггер получается заменой в обычном D-триггере двух входных элементов 2И-НЕ на 3И-НЕ (ЛА4). На основе доступных на тот момент элементов И-ИЛИ-НЕ построить подобный триггер столь же эффективным способом было невозможно: для него требуется трёхвходовые элементы И, а в наличии были только двухвходовые. Конечно, совместно с ЛР1 можно использовать расширитель ЛД1 с его четырьмя входами, но такое решение требует большего числа корпусов микросхем.

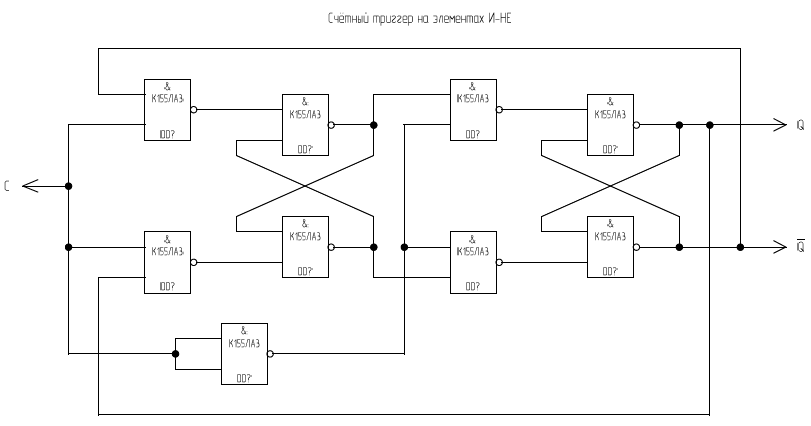

Счётные триггеры

Счётный триггер меняет своё состояние на противоположное при каждом перепаде тактового импульса; он является основой счётчика. Технически такой триггер собирается из двух последовательно включённых тактируемых RS- или D-триггеров, что в англоязычной литературе раньше именовалось совершенно неполиткорректным термином «master-slave» (в отечественной литературе — «мастер-помощник», «ведущий-ведомый», «основной-вспомогательный»). Пока «хозяин» меняет своё состояние на противоположное при высоком уровне на входе C, «раб» удерживает свои выходы в стабильном состоянии, поскольку на него подаётся инвертированный сигнал C. При смене уровня синхросигнала триггеры меняются ролями: «хозяин» хранит запомненное обновлённое состояние, а «раб» — переходит в него. Счётные триггеры одинаково легко (и с одинаковыми затратами корпусов микросхем: два корпуса на собственно два триггера плюс ещё четверть ЛА3 в качестве инвертора) собираются и на элементах И-НЕ, и на элементах И-ИЛИ-НЕ.

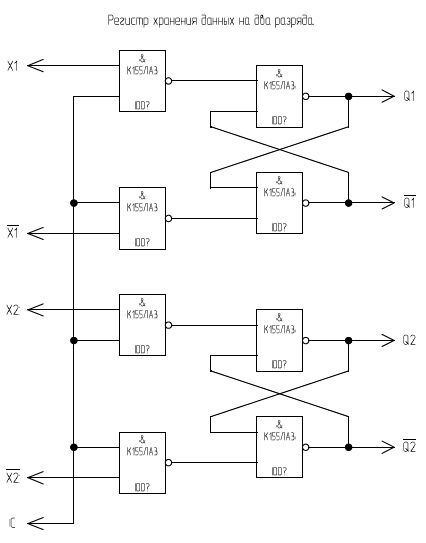

Регистры и счётчики

Дешевизна (в смысле меньшего количества необходимых логических элементов) RS-триггеров по сравнению с триггерами других типов побуждала конструкторов как можно более широко использовать именно их. Типичный регистр, принимающий данные с некоторой шины, в собранных на «рассыпухе» машинах состоит не из «современных» D-триггеров, принимающих информацию со входа D по фронту синхросигнала (общепринятое русское название для них так и не придумали, обычно называя просто D-триггерами, а сейчас нередко используют английское — flip-flop; такие триггеры, конечно, не являются современным изобретением — в 1960-х они уже точно встречались, но довольно редко в силу своей относительной сложности) и даже не из защёлок, а из «честных» тактируемых RS-триггеров.

«Секрет» заключается в том, что в ранних машинах информация по шинам очень часто передавалась с использованием так называемых парафазных сигналов, внешне напоминающих современные дифференциальные пары: если по одному проводу передаётся высокий уровень, то по второму — низкий, и наоборот. Сходство, однако, чисто внешнее: если логическое значение дифференциального сигнала (1 или 0) определяется разностью напряжений на передающих его линиях, а напряжения каждой из линий пары сами по себе безразличны (в разумных пределах, конечно), то в случае парафазного сигнала обе образующих его линии технически являются совершенно независимыми сигналами с обычными логическими уровнями, просто один из них всегда инвертирован по отношению к другому. Благодаря этому парафазные сигналы могут напрямую управлять RS-триггерами, а их формирование, как правило, не требует дополнительных аппаратных затрат: на вход одного регистра зачастую поступает информация с выхода другого регистра, а соответственно, прямое и инверсное значения каждого бита уже имеются.

Дополнительным бонусом от использования парафазных сигналов являются расширенные возможности контроля правильности передачи информации: если на момент приёма данных обе линии парафазного сигнала имеют одинаковое значение, значит, что-то где-то сломалось. Впрочем, организация аппаратного контроля работы машины — отдельная тема.

Довольно остроумно решается и проблема приёма и хранения данных, считываемых из памяти, с минимальными затратами оборудования. Регистр данных тоже строится на RS-триггерах, причём на сей раз самых простых — даже без входа тактирования. В начале цикла считывания все триггеры регистра сбрасываются в нуль (сигналом сброса в данном случае может служить сигнал занесения адреса в регистр адреса памяти, с чего начинается обращение к ней). Считывание единичного бита из некоторого разряда ячейки памяти вызывает появление импульса на входе усилителя считывания, который усиливает его и при необходимости растягивает во времени, после чего передаёт на вход установки соответствующего триггера регистра данных. Как следствие, триггеры регистра данных для тех разрядов ячейки памяти, которые хранили единицы, устанавливаются, а остальные триггеры остаются сброшенными.

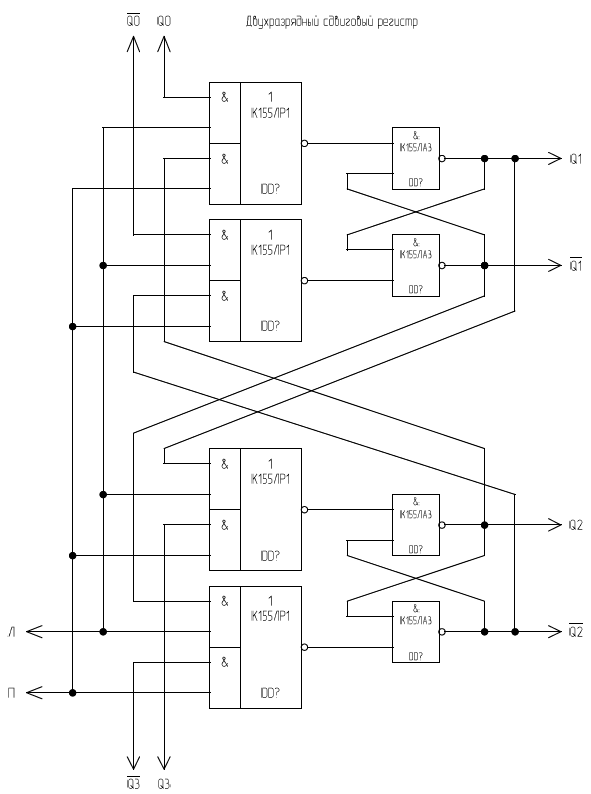

Сдвиговый регистр тоже собирается на слегка модифицированных RS-триггерах. Как видно на схеме, первый каскад образован элементами 2,2И-2ИЛИ-НЕ, на каждый из входных элементов И которых подаётся свой управляющий сигнал П или Л, вызывающий соответственно сдвиг вправо или влево. Кстати, насчёт обозначений П и Л: в документации на ранние машины действительно используется русско-английская смесь, где П и Л соседствуют с R и D — благо, ватманы с кульманами, в отличие от многих САПР, всё стерпят.

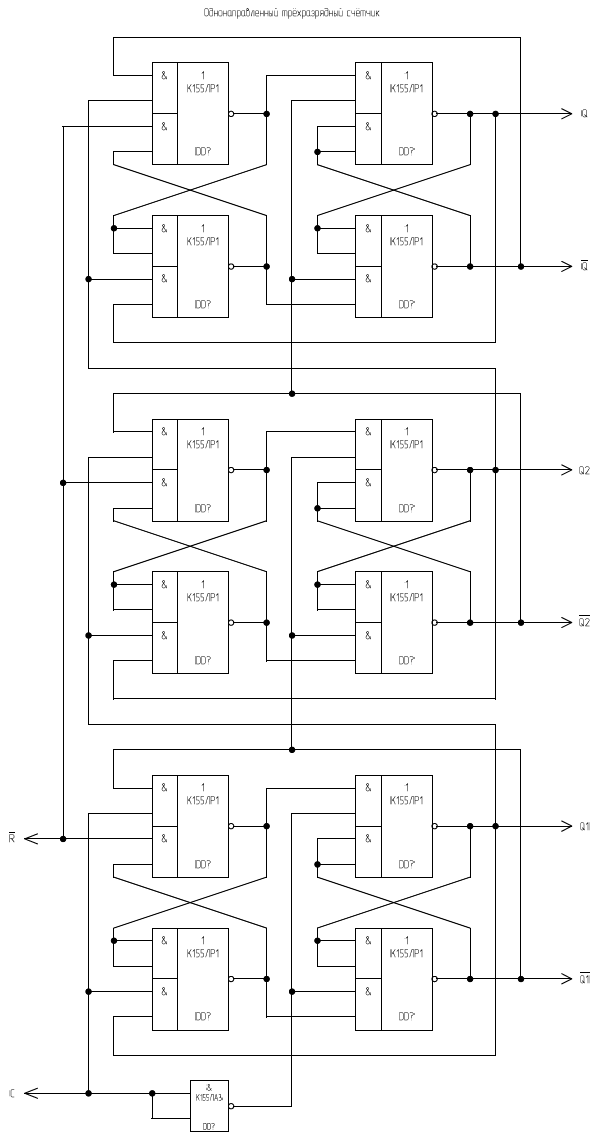

Счётчики создаются на основе счётных триггеров. В качестве примера показана схема 3-разрядного однонаправленного счётчика со входом сброса на основе элементов 2,2И-2ИЛИ-НЕ. Каждый его разряд требует две микросхемы ЛР1; кроме того, требуется ещё один инвертор на весь счётчик.

Комбинационные схемы

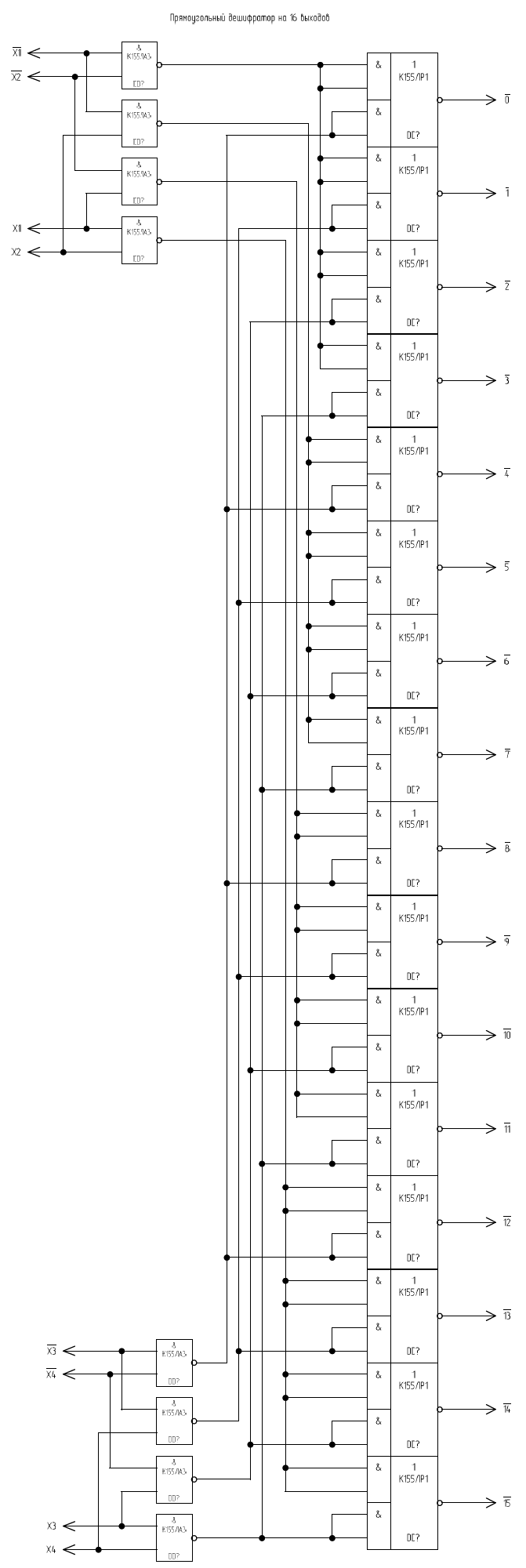

Вполне ожидаемо, что «ископаемые» дешифраторы по своему устройству, по большому счёту, не отличаются от более современных. Единственным заметным отличием является то, что в состав «рассыпных» схем обычно не включаются инверторы, необходимые для формирования обратных значений исходных сигналов: поскольку почти всегда входная информация подаётся с регистров, а те выполнены на триггерах, имеющих и прямой, и инверсный выходы, совершенно естественно пользоваться их «услугами». В качестве примера показаны схемы так называемых линейного импульсного дешифратора на 8 выходов («импульсный» в данном случае означает наличие дополнительного входа управления, разрешающего или запрещающего работу дешифратора, благодаря чему на одной из выходных линий можно в нужный момент времени сформировать импульс) и прямоугольного дешифратора на 16 выходов. Как видим, выходы у них всегда инвертированные; если нужно получить результат в прямом виде, приходится ставить инверторы.

Мультиплексоры в явном виде как отдельные законченные функциональные блоки в конструкции ранних машин не выделялись, хотя они, конечно, были. Собственно выбор одного из входных сигналов и передача его на выход осуществляется элементом И-ИЛИ-НЕ на нужное число входов (два у ЛР1 и четыре у ЛР3, при необходимости они дополняются расширителями ЛД1). Какой именно из элементов И будет открыт, определяется управляющими сигналами, поступающими с дешифратора, а последний в типичном случае управляется выходами некоего регистра. Таким образом, мультиплексор в современном понимании оказывается «размазан» между: 1) выходами регистра, содержащего код источника (оттуда поступают прямые и инверсные значения разрядов кода), 2) дешифратором кода источника, 3) инверторами на выходах дешифратора (поскольку с него поступают инвертированные сигналы, а управлять они должны элементами И — т. е. быть прямыми) и 4) схемой выбора одного из входных сигналов на элементах И-ИЛИ-НЕ.

Вот устройство самой сложной комбинационной схемы ранних машин — АЛУ — заметно отличается от, например, классической микросхемы К155ИП3, в девичестве SN74181. Впрочем, эта тема весьма обширна и заслуживает отдельной статьи.

Литература

В. В. Пржиялковский и др. Электронная вычислительная машина ЕС-1020. Под общей редакцией А. М. Ларионова. — М., «Статистика», 1975

Р. М. Асцатуров и др. Процессор ЭВМ ЕС-1020. Под общей редакцией А. М. Ларионова. — М., «Статистика», 1975

Р. И. Абражевич и др. Каналы ввода-вывода ЭВМ ЕС-1020. Под общей редакцией А. М. Ларионова. — М., «Статистика», 1975

А. Т. Кучукян и др. Электронная вычислительная машина ЕС-1030. Под общей редакцией А. М. Ларионова. — М., «Статистика», 1977