Некоторое время назад появилась в моем распоряжении плата Raspberry Pi3. Ее возможности действительно впечатляют: и быстрый четырехядерный процессор, и встроенные аппаратные кодеки/декодики аудио/видео/jpeg, сеть Ethernet/WIFI, USB2, HDMI… Прямо настоящий компьютер. Очень круто, что есть разъем GPIO, который позволяет разным умельцам подключать что-то свое нестандартное и особенное. Существует огромное число различных плат расшрения, которые устанавливаются на этот разъем: дисплеи, светодиодные экраны, адаптеры для двигателей, платы АЦП…

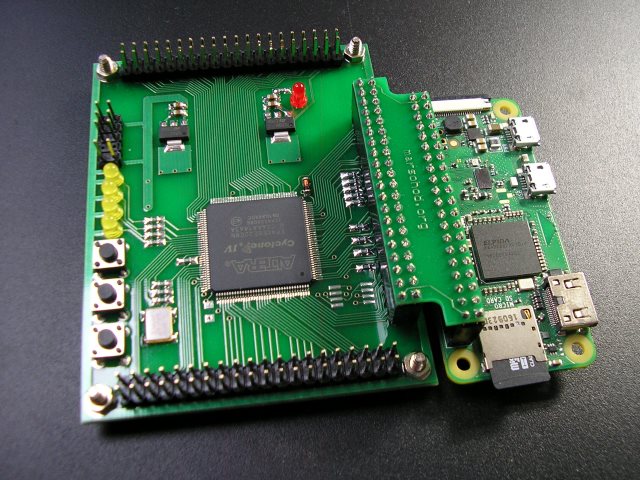

Я хотел бы немного рассказать об FPGA плате Марсоход2RPI, которая, как и другие платы расширения, подключается к разъему GPIO распберри, и добавляет нашему микрокомпьютеру совершенно новые свойства.

Плата довольно проста. На ней установлены:

- FPGA Cyclone IV EP4CE6E22C8

- логических элементов 6272;

- встроенная память 270Кбит;

- Умножителей 15 (18x18);

- PLL 2;

- Четыре светодиода;

- Три кнопки;

- Кварцевый генератор 100Мгц;

- Возможность установки чипа EPCS4 (для случая, если плата будет использоваться автономно);

- Разъем JTAG (для случая, если плата будет использоваться автономно);

- Два 40 пиновых разъема на каждом по 28 пользовательских GPIO — разъемы совместимые с Raspberry;

- Один 40 пиновый разьем для подключения к Raspbery, на котором можно использовать 24 или 20 GPIO (в зависимости от того, установлен чип EPCS4 или нет).

Плата Марсоход2RPI устанавливается не над платой Raspberry Pi, а сбоку, через специальный переходник. Это сделано умышленно. Raspberry Pi3 и так довольно сильно греется при загрузке 4-х ядер, накрывать плату сверху кажется не очень гуманным с точки зрения охлаждения.

Так можно подключить плату Raspberry Pi2/ Pi3:

А вот так Pi-zero:

Возможно (но это не точно), эту же плату расширения можно будет использовать с OrangePi.

Самое первое применение этой платы, которое приходит на ум — это увеличение количества GPIO сигналов в два раза: был один разъем, а стало два. Нужно только создать и загрузить в ПЛИС нужный проект, ну и управлять входами выходами придется каким-то особым образом, тут вариантов много: последовательный порт, SPI, GPIO, можно задействовать DMA…

Загружать ПЛИС платы Марсоход2RPI можно прямо из Raspberry через JTAG сигналы, которые, конечно, отображаются в GPIO

- tck > GPIO7

- tms > GPIO0

- tdi > GPIO11

- tdo < GPIO1

Есть такой open source проект OpenOCD, отладчик и дебагер, который позволяет использовать Raspberry как JTAG программатор. OpenOCD — это сервер, его можно запустить, а потом подключаться к нему хоть удаленно телнетом и выполняя команду «svf» можно загрузить образ скомпилированного проекта в ПЛИС. Подробнее об OpenOCD на raspberry pi.

Вот тут как раз видеодемонстрация:

Самый первый «тестовый» проект для платы Марсоход2RPI уже готов, хотя пока не очень впечатляет своей функциональностью. Первый проект для ПЛИС — это обычно всегда «моргание светодиодом», такой своего рода «hello World!» мира микроконтроллеров и FPGA.

Его исходники можно взять на github: github.com/marsohod4you/m2rpi_first

Но и тут, даже в этом простом случае уже есть взаимодействие ПЛИС и микрокомпьютера. Из raspberry можно посылать через последовательный порт в ПЛИС байты, которые меняют скорость моргания светодиода. Более того, первый «тестовый проект» ПЛИС принимает байт из последовательного порта, модифицирует его (добавляет единицу), и отправляет назад. Конечно, довольно примитивное, но уже взаимодействие двух систем ПЛИС и процессора.

Видеодемонстрация:

Это мой первый опыт доступа к ПЛИС из Raspberry. Я думаю, что было бы интересно попробовать делать действительно сложные проекты, как, например, захватывать в распберри кадры от видеокамеры и передавать их по DMA в ПЛИС для обработки. Думаю интересных проектов с этой платой расширения может быть много.

Комментарии (93)

igor_suhorukov

28.11.2017 00:20Насколько описанная здесь связка удобнее, мощнее или дешевле DE0-Nano-SoC?

nckma Автор

28.11.2017 11:24Разные весовые категории. Понятно, что в Cyclone V связка с FPGA будет гораздо более широкополосной. Но Cyclone V и дороже.

romanetz_omsk

28.11.2017 14:28DE0-Nano-SoC с производства сняли

nckma Автор

28.11.2017 14:32Зато теперь рекламируют DE10-nano.

И объявили конкурс проектов mail.terasic.com.tw/epaper/2017/innovatefpga_en2

Полуфиналисты получат уже эту DE10-nano плату для опытов.

Sun-ami

28.11.2017 00:56Лучше соединить платы шлейфом с разъёмами. Тогда можно будет сложить платы бутербродом тыльной стороной, если нужна большая компактность, это не помешает охлаждению, если Raspberry Pi будет сверху, или бутерброд будет установлен вертикально. И выйдет проще, дешевле, без проблем с точным выравниванием для того чтобы установить переходник, и выламывания разъёмов, если платы не прикручены к корпусу или основанию.

Sdima1357

28.11.2017 00:58Картинку по DMA нет смысла передавать. Слишком мало встроенной памяти на плате fpga. А видео процессинг с таким маленьким футпринтом (270 кбит)дешевле делать на самой распи. Лучше обратно- читать внешний hdmi например

tronix286

28.11.2017 09:13Самый главный минус, на мой взгляд, отсутствие какой-либо памяти. Куда на 100МГц байты складывать? Ответ — никуда. Вот и превращается Cyclone IV в обычный ногодрыг уровня 51 контроллера, который может дрыгнуть ногой, выплюнуть по SPI или принять по UART. На этом все.

Andy_Big

28.11.2017 09:25Это же не NAS. Приняли порцию данных, обработали ее, вернули (или передали дальше) результат. Как пример — прием данных от АЦП, цифровая узкополосная фильтрация в несколько ступеней с промежуточной децимацией и выдача результата

Andy_Big

28.11.2017 09:38Например, я занимался проектом, в котором 4-й циклон являлся прослойкой между хитрым АЦП и микроконтроллером. Он полностью управлял АЦП и по команде контроллера считывал с АЦП порцию данных, прогонял ее последовательно по четырем фильтрам (каждый последующий — с более узкой полосой, последний с полосой то ли единицы, то ли десятые доли Гц, по-моему) и накапливал указанное количество результатов для выдачи контроллеру. Всего во всех фильтрах было несколько тысяч коэффициентов и при каждом новом значении на входе каждый фильтр должен произвести перемножений по количеству коэффициентов в нем, просуммировать результаты и сдвинуть буфер входных данных, а данные с АЦП считывались на 10 МГц. И все это в два параллельных канала :)

Вот Вам и недодрыг уровня 51 контроллера :)

nafikovr

28.11.2017 09:59все хорошо, но только когда микроконтроллер реального времени. например типичная беда USBee — комп не успевает забирать данные с анализатора. был бы буфер — не было бы проблем.

Andy_Big

28.11.2017 10:10Никто не мешает прицепить к FPGA память SRAM или SDRAM. Ее отсутствие — это проблема реализации устройства, а не Cyclone IV :)

Так-то в недостатки FPGA можно записать еще и отсутствие дисплея, физического уровня Ethernet 1G, АЦП, выхода HDMI и т.п. И несовместимость с Ардуиновскими скетчами :)

tronix286

28.11.2017 10:12Мешает отсутствие на плате хотя-бы посадочного места под память, не говоря уже о ее наличии. Прицеплять к плате SRAM в TSOP II будет МГТФом?

Andy_Big

28.11.2017 10:15Если хочется поизвращаться, то можно и МГТФ. Если не хочется — то платка с разъемами, вставляющимися в разъемы платы из статьи.

tronix286

28.11.2017 10:19Ну понятно, платка на платку через платку в платку.

Andy_Big

28.11.2017 10:25Что в этом не так? Это же не специализированное под накопление больших данных устройство, это демонстрационная плата для изучения работы с FPGA. Кому что понадобится — тот то и прицепит дополнительно, к чему повышать стоимость без веских оснований?

nafikovr

28.11.2017 10:28что то скоростное параллельное на одной то плате не всегда нормально разводится.

Andy_Big

28.11.2017 10:30Ну значит уровень этой платки уже пройден и пора переходить к более серьезному подходу — делать свою плату со всей нужной периферией под свою задачу.

nafikovr

28.11.2017 10:36тут скорее ограничение в количестве ног. приходится выбирать или в 2 раза больше GPIO, или память. мне кажется память была бы интереснее.

Andy_Big

28.11.2017 10:51А зачем Вам столько ног? :)

nafikovr

28.11.2017 10:58мне незачем, я же написал что мне память была бы интереснее

Andy_Big

28.11.2017 11:00Ну так сделайте платку и подключите :) Или купите отладочную плату с интегрированной памятью, если делать неохота :)

Я бы еще понял, если бы на этой плате были только светодиоды и пара кнопок, и все, никаких коннекторов расширения.

tronix286

28.11.2017 10:32+1О каких больших данных идет речь? Простая задача — захватить кадр видео с VGA выхода и передать на Пи, который из кадра сделает jpeg скриншот. Не реализуемо на данной конфигурации. Кадр VGA — большие данные?

Andy_Big

28.11.2017 10:45Для этой задачи в любом случае нужно еще соответствующий АЦП.

А вот, например, гнать в FPGA поток какого-то сигнала и получать от нее спектр этого сигнала — легко.

uterr

28.11.2017 11:03Такие задачи делаются на FPGA, только кадр захватывается не целиком, а поточно, так что такого объема памятик, для такой задачи как вы назвали, достаточно.

Во вторых, как уже заметили, отсутствие памяти это не проблема, хотите — просто подключите внешнюю память, многие FPGA это умеют нативно, для других же есть библиотеки работы с памятью

tronix286

28.11.2017 11:26Ну-ка, поподробнее про захват «поточно». Особенно если пиксельклок у VGA самое низкое 25 с хвостиком МГц. Пока вы будете «поточно» отдуплять как текущую точку просунуть через UART в Пи на 9600 бот, вы потеряете не только следующую точку, но и вообще все остальные точки из кадра, а может быть даже и несколько следующих полных кадров.

Andy_Big

28.11.2017 11:30Во-первых можно сжимать, что сильно снизит поток, а во-вторых в статье что-то упоминается об использовании DMA, а это чуть быстрее, чем UART на 9600.

Bluewolf

28.11.2017 21:35Для статичных кадров можно. Захватываем несколько строк, медленно передаем через уарт (и да, у многих уартов скорость все же не 9600, а до единиц мегабит), потом захватываем следующие и так далее. Собственно, для многих применений «дешево посмотреть, почему удаленный комп не отвечает по основному интерфейсу» этого достаточно.

tronix286

28.11.2017 10:36На сколько повысится стоимость из-за перетаскивания в КАДе мышкой корпуса TSOP на плату и подвода к этому корпусу дорожек?

nafikovr

28.11.2017 10:38камень надо менять ибо ног не хватит

Andy_Big

28.11.2017 10:54Не хватит для чего? К этому камню можно прицепить два чипа памяти в TSOP44 — каждый с со своими шинами и сигналами.

nafikovr

28.11.2017 11:07я к тому что нельзя просто добавить память. надо выбирать или гпио, или память. или же ставить более жирный камень.

Andy_Big

28.11.2017 11:18Или память и штук 20 внешних гпио (для малинки там свои гпио еще остаются). Поэтому и спрашиваю — для чего Вам не хватит гпио?

nafikovr

28.11.2017 11:39я уже третий раз пишу что мне хватит. и я так и написал что есть вариант ими пожертвовать. я про то что нельзя просто взять и вставить память в данную плату.

Andy_Big

28.11.2017 11:44Можно взять и вставить, при этом останется около 20 свободных пользовательских IO. Это при условии, что плата воткнута в малину, а не подключена к ней по SPI, например. Тогда останется что-то около 50 IO :)

Andy_Big

28.11.2017 10:58И АЦП с ЦАП. И Ethernet. И USB. И какой-нибудь радиомодуль. И датчик температуры-влажности.

Не нужно усложнять без необходимости. Возможность подключить любую периферию. в том числе и память, имеется. Кому она понадобится — прицепит без проблем :)

nafikovr

28.11.2017 11:04поставим вопрос подругому. вы часто используете fpga без памяти? тем более такой емкости.

Andy_Big

28.11.2017 11:16Я с ними вообще нечасто работаю. Но вот Вам практическая и довольно актуальная задача — контроллер движения для станков с ЧПУ. Нужно формировать управляющие сигналы для 4-5 шаговых двигателей на основе задаваемых извне параметров. Например, управляющий контроллер задает новую координату одной из осей и контролер движения должен выдать на ШД необходимые импульсы с учетом кривых разгона и торможения, максимально допустимого ускорения, а так же того, что в данный момент эта ось уже может двигаться с некими скоростью и ускорением. Или чуть сложнее — от управляющего контроллера поступают команды для движения сразу всех осей в определенные координаты и контроллер движения должен рассчитать все это синхронно для всех осей сразу с учетом всего, перечисленного выше. Можно и дальше усложнять задачу контроллера движения, облегчая тем самым жизнь управляющему контроллеру.

Тут памяти нужно совсем немного, и вот этот обсуждаемый чип с такой задачей справится.

Sdima1357

28.11.2017 11:30Распи отлично с этим справляется. С 6 шаговыми двигателями CNC. В реальном времени.6 каналов ШИМ на 2 кГц 8 бит на цикл. 1 core занят на 100%

Andy_Big

28.11.2017 11:35Не совсем понял. 2 КГц — это частота выдаваемых на двигатели импульсов?

nafikovr

28.11.2017 11:40и 8бит О_о

Andy_Big

28.11.2017 11:42Да, этот момент я тоже не понял, но может он разъяснится в ответе про 2 КГц :)

Sdima1357

28.11.2017 12:042 кГц — частота прерывания переключения процессов настраивается при компиляции ядра(по умолчанию 1000 гц). На 8 бит (256 шагов ) делятся задержки внутри одного цикла переключения пинов «step” и «dir”

То есть вымажете программировать время фронта пинка “step” с резолюцией ~2 мкс но не чаще чем 2000 импульсов в секунду на каждый двигатель

Andy_Big

28.11.2017 12:11время фронта пинка “step” с резолюцией ~2 мкс

Это много для плавной и тихой работы ШД.

не чаще чем 2000 импульсов в секунду на каждый двигатель

Это очень-очень мало. При микрошаге 1/16 и ШВП 5 мм/оборот скорость перемещения получается всего около 190 мм/мин. Или я до сих пор что-то не понимаю.

Sdima1357

28.11.2017 13:37Вопрос ценовой категории. Для дешевого станочка можно и 1/2 step использовать — получите 5мм/200/2 = 0.0125mm резолюцию и 2000*60*5/200/2 = 1500 mm/min. А для приличного можно и ардуину добавить

Andy_Big

28.11.2017 13:56Для дешевого станочка можно и ардуину с прошивкой GRBL :) И дешевле и скорость перемещений выше при большем дроблении шага :)

Sdima1357

28.11.2017 14:54У ардуины телевизора нет :(

Andy_Big

28.11.2017 15:50Не особо-то он и нужен таким станкам :)

Sdima1357

28.11.2017 16:16тогда STM32F103C8T6 за пару долларов.

Andy_Big

28.11.2017 16:22А для них уже адаптировали какой-нить планировщик? Я кроме небольших частных проектов не встречал такого :)

Sdima1357

28.11.2017 16:32Я не знаю. По идее пинов и скорости хватает.Мне просто не нужно было, не смотрел с этой точки на STM.

Мне распи хватило на хексапод(6 axis ), с камерой и прочими наворотами, правда требования по скорости перемещения были низкие, а к точности позиционирования -высокие

Andy_Big

28.11.2017 18:48Да по идее хватает, их даже гораздо больше, чем у ардуины :) Но вот не видал я такого, никто не реализовал в доступном виде.

nafikovr

28.11.2017 11:35у меня почему то все задачи связанные с fpga требовательны к памяти.

по примеру — интерполяция дуг на стороне контоллера или на стороне fpga? если на стороне fpga — память может понадобиться. если на стороне контроллера — можем получить рывки, когда будет необходимость передавать/выполнять малые перемещения в большом количестве. не забываем что контроллер в данной статье не realtime. так что опять же может понадобиться память для буфера. но согласен, тут ее не так много надо

Andy_Big

28.11.2017 11:39Интерполяция даже 3-мерных дуг не требует мегабитов памяти и прекрасно может быть реализована на этом циклоне :)

Я давно хочу сделать такой контроллер движения, управляемый высокоуровневыми командами (почти уровня G-кода) но все никак не выберу время заняться этим проектом...

nafikovr

28.11.2017 11:41сталкивался с такими на УФ принтерах. но там 3 координаты + растровый датчик + печатная головка на

домного сопел. в чпу не встречал.

Andy_Big

28.11.2017 11:47Для ЧПУ есть контроллер для Mach на FPGA — Smooth Stepper. После перехода с LPT на него (у меня ethernet-вариант этого контроллера) скорость перемещений получилось поднять в 1.5 раза и двигатели потише стали работать :)

nafikovr

28.11.2017 13:34я думал он тупой. в смысле команды все равно в mach3 обрабатываются.

Andy_Big

28.11.2017 13:58Да, траектория все равно планируется в Mach-е. Честно говоря, не знаю какие именно функции возложены на саму ПЛИС, вроде бы Мач отдает контроллерам сервоциклы с готовыми количествами импульсов по каждой оси, так я понял из отрывочных сведений по его API. Но могу и ошибаться.

nafikovr

28.11.2017 14:12суть же не в количестве импульсов, а во времени между ними. ethernet таки не LPT (да и там далеко не realtime) и временные интервалы надо отслеживать уже на контроллере.

Andy_Big

28.11.2017 14:35Ну, у сервоциклов-то длительность строго фиксированная, так что это не проблема :)

Да, LPT далек от рилтайма, к сожалению. Да и входов-выходов у него маловато. В этом плане ESS рулит :)

GPavlikh

28.11.2017 10:17Наверняка это было сделано на несколько большем чем 15 умножителей и 270 кбит памяти. Здесь же — ресурсы ограничены довольно сильно. Подойдет разве что для первоначального погружения в тему FPGA.

Andy_Big

28.11.2017 10:23Да, это было сделано на чуть более старшем представителе семейства с 56 умножителями и 500 кбит памяти. Потому что требовалась очень узкая полоса фильтра.

Автор вроде и заявил эту плату как для начального погружения :)

DenisDangerous

28.11.2017 10:17Насколько мощная эта Raspberry Pi? На ней можно сделать станцию для веб разработки? Как она графическое окружение тянет? Опыт был с кубибордом 1м, там чисто графическое окружение 90-100% проц грузит, для софта уже нет ресурсов… Работает сейчас как аудио плеер, чисто консолька

Sdima1357

28.11.2017 10:33Процессор слабее среднего пс от 6 до 20 раз, в зависимости от задачи. Графика слабее дискретной карты от 100 до 200 раз. ( порядка гигапикселя в секунду отрисовки ). Дривер графики не поддерживает большого количества треугольников(до 32000) в opengl который довольно древний

Alexey2005

28.11.2017 20:11Пробовал запускать тяжёлый софт, комфортной работы закономерно не получается.

WebStorm запускается и даже в режиме пониженной задержки позволяет набирать текст без подтормаживаний, но о какой-либо комфортной работе можно забыть, даже просто синтаксический анализ тормозит нещадно.

Кроме того, работать на RPi 3B с полноценными браузерами не выйдет, очень уж тормознуты. Только что-то специальное вроде links2 (идёт отлично, без тормозов) или kweb.

Также возможно поставить плагины к pidgin, чтобы получить Skype- или Telegram-мессенджер. Причём сборка telegram-purple ещё год назад требовала не только самостоятельной компиляции, но и правки исходников (не знаю как сейчас).

Также RPi можно использовать в качестве простой рисовалки. Мой графический планшет (wacom) увидело после установки пакета xserver-xorg-input-wacom. Комфортно и без подтормаживаний работают простейшие рисовалки вроде MyPaint и mtPaint.

GIMP уже притормаживает, работать некомфортно, но возможно. Krita не запускается вовсе, вываливаясь с сегфолтом.

Из всех способов увеличения производительности максимальный прирост даёт полное отключение журналирования через tune2fs с последующей правкой fstab. На втором месте — разгон SD-ридера (при условии, что карточка нормальная, а не китайский самопал).

Использование в качестве аудиоплеера проблемно, т.к. звук в аналоговом выходе полный отстой, нужно брать звук исключительно от HDMI-выхода, а туда без переходника наушников не воткнуть.

defecator

28.11.2017 10:181. Для чего-нибудь более-менее серьёзного слишком мала ёмкость FPGA

2. Чтобы не грузить каждый раз FPGA логично было бы установить на плату микросхему EPCS.

3. Имхо, сопряжение малинки и DE0-Nano прибавит возможностей гораздо больше, чем просто голая ПЛИСина.

umarsohod

29.11.2017 13:46+11. Емкость — понятие относительное. Кому-то и маленькой емкости хватает, у кого-то и на большой ничего не получается.

2. А если статью еще раз внимательно перечитать?

3 Не просто «голая ПЛИС », а с максимальным количеством GPIO.

dernasherbrezon

28.11.2017 12:11А можно на fpga декодировать радио сигналы? Там большой поток входных данных и крайне малый выходной поток. Я так понимаю это идеально для FPGA без памяти?

Andy_Big

28.11.2017 12:25А что Вы подразумеваете под "декодировать радиосигналы"?

dernasherbrezon

28.11.2017 12:40На вход поступает поток float. Далее этот поток обрабатывается последовательно несколькими операторами. Каждый из них достаточно простой:

- Либо меняет текущее значение на основе предыдущего (или массива предыдущих)

- Либо отбрасывает

- Либо ищет подпоследовательность и пока не нашел, отбрасывает

На выходе получается сравнительно небольшой поток float. В моих тестах из 300000 байт получается где то 180 байт.

Andy_Big

28.11.2017 12:41А скорость входного потока какая?

dernasherbrezon

28.11.2017 12:48Скорость может регулироваться, но максимум — 50mbit/sec. (3.2M sample/sec, 3.2M 16bit float/sec)

Andy_Big

28.11.2017 12:49Ну… В принципе может получиться. Но нужно, конечно, смотреть более детально :)

safari2012

28.11.2017 13:38Заранее извиняюсь за глупый вопрос, а почему «марсоход»?

Просто слово красивое, или что-то смысловое?

Andy_Big

А зачем загружать по JTAG если можно по родному последовательному протоколу загрузки, по которому и EPCS ее грузит? Там обычный SPI, плюс контроль одного или двух статусных пинов, сейчас точно не помню :)

nckma Автор

Предполагалось далее сделать сетевой сервер для распберри, чтобы удаленно из среды Altera Quartus можно было бы отладку делать в SignalTap. Для этого нужен JTAG.

Andy_Big

А, тогда понятно :)